Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем для ре20

шения задач, алгоритмы которых имеют последовательно-параллельную структуру..

Цель изобретения - увеличение производительности обмена за счет исполь-jj зования режима блочной передачи.

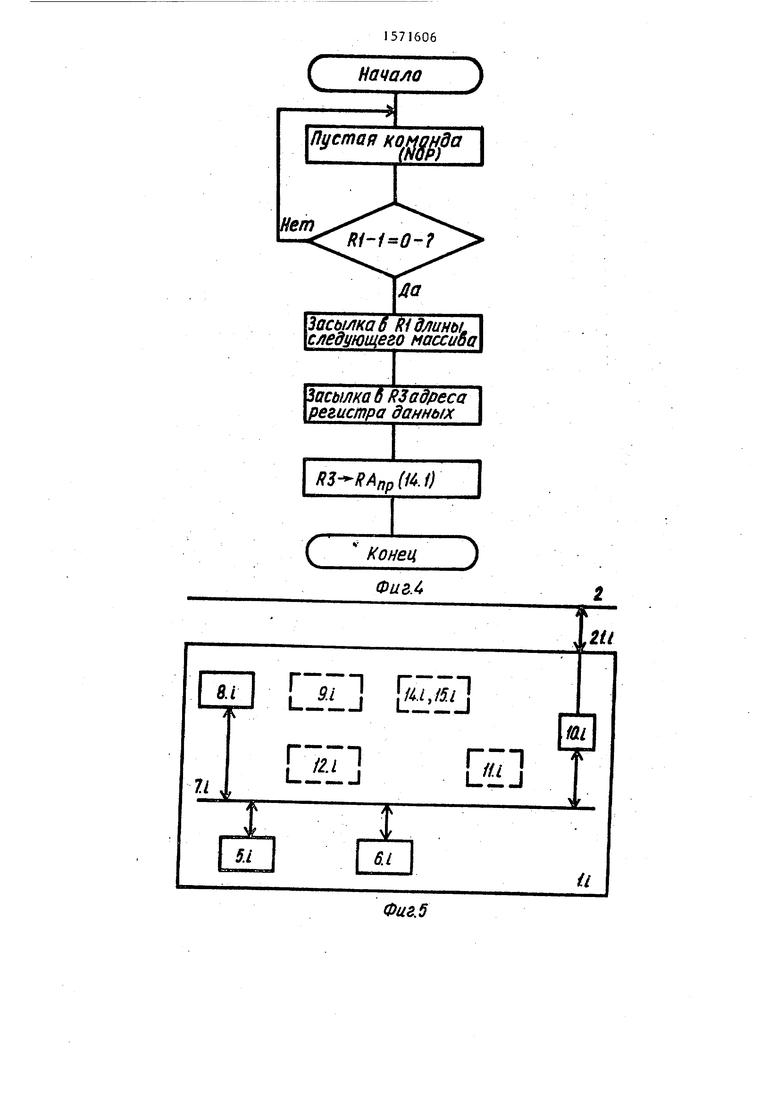

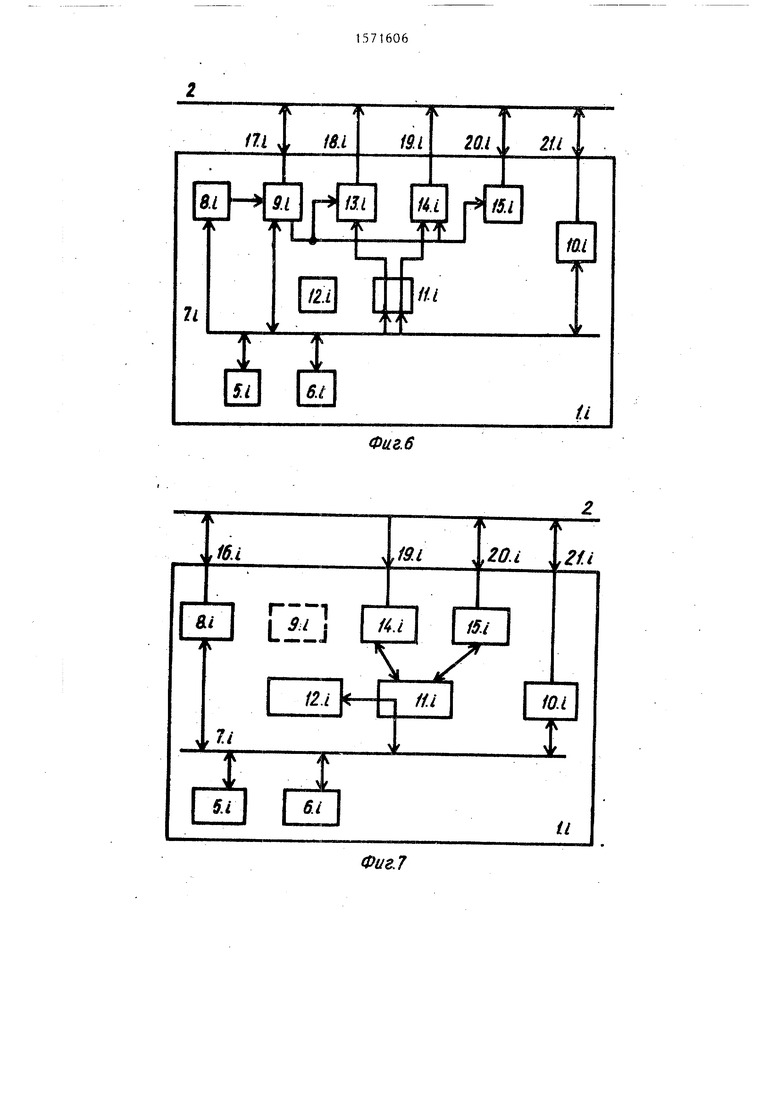

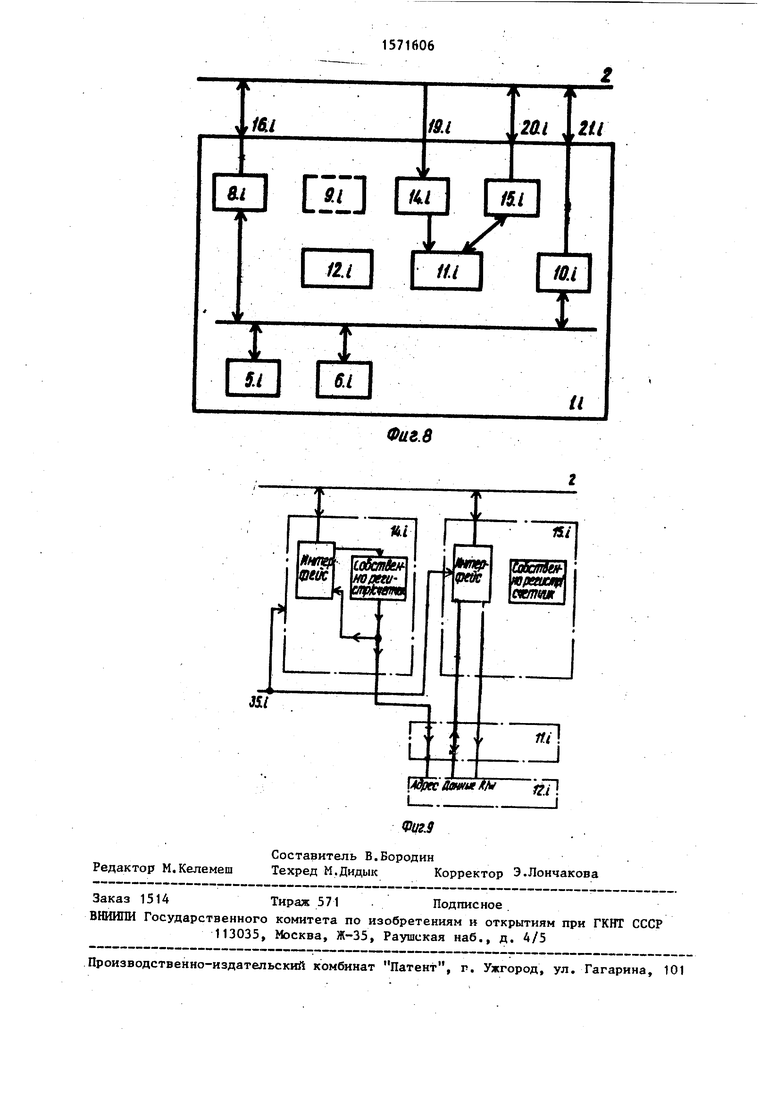

На фиг. 1 представлено использование устройства в мультипроцессорной системе; на фиг. 2 - пример формата регистра состояния; на фиг. 3 - при- „ мер реализации блока управления; на фиг. 4 - алгоритм обмена информацией между процессорными блоками; на фиг.5 - конфигурация связей процессорного блока в режиме управляющего процессорного блока; на фиг,- 6 - то же, в режиме коммуникационного процессорн ого блока; на фиг. 7 - то же, в режиме выполнения программы; на фиг. 8 - то же, в режиме обмена между процессорными .,. блоками; на фиг. 9 - схема подключения регистров адреса к общей шине системы и блоку коммуникационной памяти.

Мультипроцессорная система (фиг.1) содержит процессорные блоки 1.1,..., д- 1.п, общую шину 2 системы, к которой подключены блок 3 общей памяти и устройства 4.1,...,4.т ввода-вывода.

В каждом процессорном блоке 1.1 процессор 5.1 и блок 6.1 локальной па-.

50

мяти объединены между собой локальной шиной 7.1, к которой также подключены регистр 8.1 состояния и блок 9.1 управления.

Локальная шина 7.1 соединена также с коммутатором 10.1, а через коммутатор 11.1 подведена к блоку 12.1 коммуникационной памяти, к регистру 13.1 адреса источника, регистру 14.1 адре0

j

,.

-

0

5

са приемника, регистру 15.1 данных. Регистр 8.1, блок 9,1, регистр 13.1, регистр 14.1, регистр 15.1 и коммутатор 10.1 соединены с общей шиной 2 через входы-выходы 16.1 - 21.1.

Назначение блока 9.1 управления состоит в выработке сигналов, которые необходимы для реализации циклов обращения к общей шине 2, а также управляющих сигналов, обеспечивающих реконфигурацию системы, т.е. определенного соединения между собой функциональных узлов с помощью коммутатора 11.1. Режим работы блока 9.1 управления определяется значением соответствующих разрядов регистра 8.1 состояния.

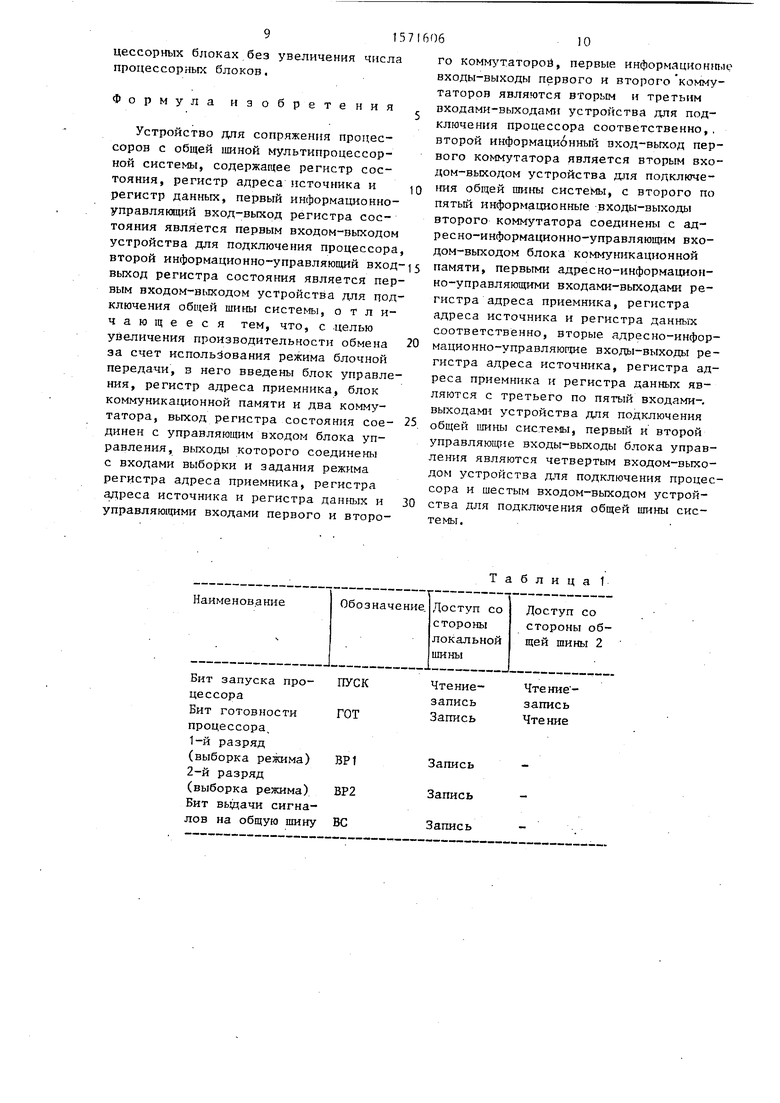

Возможный формат регистра 8.1 состояния представлен на фиг. 2, а назначение каждого разряда поясняется табл.1 и 2.

Пример построения блока 9.1 управления представлен на фиг. 3.

Блок 9.1 управления содержит триггер 22, элемент И-НЕ 23, буферный регистр 24, элемент И 25, первый выход 26, элемент И-НЕ 27, элемент И 28, второй выход 29, первый 30 и второй 31 входы, дешифратор 32, с третьего по шестой выходы 33 - 36, элемент И 37, элемент ИЛИ 38, третий вход 39 и седьмой выход 40.

Коммутатор 11 предназначен для установки связей .в соответствии со значениями разрядов ВР1 и ВР2 регистра 8 состояния между локальной шиной 7 и блоком 12 коммуникационной памяти, локальной шиной 7 и регистрами 13 и 14, а также между блоком 12 коммуникационной памяти и регистрами 14 и 15.

Система работает следующим образом (фиг. 1).

При инициализации системы (по внешнему сигналу Сброс) процессоры 5.1,...,5.п начинают выполнять программу, расположенную в своей локальной памяти с определенного начального адреса (например, нулевого). В результате выполнения этой программы производится инициализация каждого процессорного блока. Один из процессорных блоков, например 1.1, выполняет функции управляющего процессорного блока, а остальные - подчиненных процессорных блоков 1.2,..., 1.п (это достигается, например, установкой в соответствующее состояние разрядов ВР1 и ВР2 выборки режима в регистре 8 состояния по внешнему сигналу Сброс).

- В процессе функционирования системы процессорный блок 1.1 может работать в режиме управляющего процессорного блока или в режиме коммуникационного процессорного блока. Остальные процессорные блоки 1.2,...,1.п являются подчиненными и могут работать в двух режимах, а именно: в режиме выполнения программы, записанной в блоке 6 локальной памяти, и в режиме обмена информацией с другими устройствами системы. Перевод процессорного блока 1 в любой режим работы осуществляется записью информации в разряды ВР1 и ВР2 регистра 8 состояния в соответствии с табл. 2.

В каждом режиме процессорные блоки 1.1,...,1.п имеют определенную конфигурацию связей. Настройка каждого процессорного блока 1 на определенный режим работы осуществляется с помощью коммутаторов 10 и 11, которыми управляет блок 9 управления. В зависимости от значений разрядов ВР1 и ВР2 регистра 8 состояния дешифратор 32, входящий в состав блока 9 управления, формирует активный уровень сигнала на одном из четырех выходов 33 - 36 (фиг. 3). В соответствии с этим осуществляется необходимое соединение устройств, связанных с коммутатором 11, или переключается коммутатор 10, обеспечивая связь между шинами 2 и 7.

Работа системы при решении определенной задачи включает чередующиеся этапы параллельного выполнения программ в процессорных блоках 1.1

1.п и обмена информацией между подчиыьме

Г / 6П66

ненными процессорными

0

5

0

5

0

5

0

5

0

1.п.

При выполнении собственной программы каждый процессорный блок 1 имеет конфигурацию, представленную на фиг.7, когда процессор 5 имеет доступ к блоку 6 локальной памяти, блоку 12 коммуникационной памяти, регистру 8 состояния. В процессе обработки информации в блоке 12 коммуникационной памяти формируются массивы данных, предназначенные для передачи в другие устройства системы на этапе обмена информацией.

После завершения выполнения своей программы процессор 5 устанавливает в своем регистре 8 состояния разряд Готовность в единицу. Этап обмена информацией между процессорными блоками 1.2,...,1.п начинается после завершения выполнения программ в каждом подчиненном процессорном блоке (в этом случае бит Готовность в каждом регистре состояния 8.2,...,8.п установлен в единицу). Этот момент определяется либо путем опроса управляющим процессорным блоком 1.1 соответствующих разрядов регистров 8.2,...,8.п состояний, либо формированием сигнала прерывания для управляющего процессорного блока 1.1, который формируется при единичном значении разрядов готовности во всех подчиненных процессорных блоках 1.2,..., 1,п. Управляющий процессорный блок 1.1 (фиг. 5) переключается в режим коммуникационного процессора установкой разрядов , регистра 8.1 состояния (табл.2) и принимает конфигурацию связей, показанную на фиг.6, а подчиненные процессорные блоки 1.2,...,1.п имеют конфигурацию, представленную на фиг.8.

Программа обмена между подчиненными процессорными блоками 1,2,..., 1.п, таблицы адресов регистров данных процессорных блоков-источников и соответствующие им таблицы адресов регистров данных процессорных блоков- приемников, а также размерности массивов данных для передачи между процессорными блоками хранятся в блоке 6.1 локальной памяти коммуникационного процессорного блока 1.1, который управляет процессом передачи информации.

Рассмотрим в качестве примера процесс передачи массива данных из подчиненного процессорного блока 1.1-ис- точника в подчиненный процессорный блок 1.j-приемник. Перед началом обмена в регистре 13.1 адреса источника записан адрес регистра 15 данных процессорного блока-источника 1.1, в регистре 14.1 адреса приемника записан адрес регистра 1 5. j данных процессорного блока 1.j-приемника, а во внутренних регистрах процессора 5.1 записаны соответственно информационное слово L i, которое характеризует длину j-ro массива данных, и указа

ра 15.1 данных коммуникационного процессорного блока 1.1 записывается в регистр 15.J данных коммуникационного процессорного блока 1.j-приемника. При чтении информации из регистра 15.i данных источника фактически осуществляется чтение из его блока 12.1 коммуникационной памяти по адресу, находящемуся в регистре 14.1 адреса процессорного блока 1.1.

После каждого чтения к содержимому регистра 14.1 адреса прибавляется единица (в общрм случае длина в байтах

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обработки данных для многопроцессорной системы | 1988 |

|

SU1683039A1 |

| Мультипроцессорная система | 1990 |

|

SU1732351A1 |

| Мультипроцессорная система | 1987 |

|

SU1524063A1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство доступа к общей памяти | 1990 |

|

SU1836686A3 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| Многопроцессорная вычислительная система | 1991 |

|

SU1820391A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2001 |

|

RU2202123C2 |

Изобретение относится к вычислительной технике и может быть использовано для построения надежных мультипроцессорных систем. Цель изобретения - увеличение производительности обмена за счет использования режима блочной передачи. Устройство для сопряжения содержит процессорные блоки 1.1,...,1.N, блок 3 общей памяти, устройства ввода-вывода 4.1,...,4.M. В состав каждого процессорного блока 1 входят процессор 5, блок 6 локальной памяти, регистр 8 состояния, блок 9 управления, коммутаторы 10, 11, блок 12 коммуникационной памяти, регистр 13 адреса источника, регистр 14 адреса приемника, регистр 15 данных. В процессе функционирования системы управляющий процессорный блок осуществляет инициализацию системы и производит запуск подчиненных процессорных блоков. В режиме вычисления каждый подчиненный процессорный блок осуществляет подготовку массива данных для обмена между другими подчиненными процессорными блоками. Настройку межпроцессорных связей для обмена осуществляет управляющий процессорный блок по программе, которая хранится в его локальной памяти. Кроме того, управляющий процессорный блок (по прерыванию) может переходить на подпрограмму проверки работоспособности подчиненных процессорных блоков. 9 ил., 2 табл.

тель адреса регистра 15.К данных под- «5 читаемого слова). За счет этого подгочиненного процессорного блока 1.К-при- емника, который будет выполнять функцию приемника при передаче следующего массива данных из подчиненного процессорного блока 1,1-источника. 7п Параметр L , определяется как

Ь.РГЗ,

где PJ - количество информационных слов в массиве, предназначенном для 25 передачи из блока 12 коммуникационной памяти-источника в блок 12.J коммуникационной памяти -приемника. Коммуникационный процессорный блок 1.1 устанавтавливается адрес слова, которое будет читаться из блока 12.1 коммуникационной памяти при следующем обращении к этому процессорному блоку.

При записи информации в регистр 15.J данных приемника информация записывается в блок 12.J коммуникационной памяти по адресу, находящемуся в регистре 14.J адреса. Как и при чтении, содержимое этого регистра увеличивается на единицу, подготавливая адрес для блока 12.J коммуникационной памяти для записи следующего слова.

Начальные адреса передаваемого и

ливает в своем регистре 8.1 состояния зо принимаемого массивов устанавливаются

разряд ВС в единицу, что настраивает блок 9.1 управления на преобразование управляющих сигналов, формирующихся в локальнрй шине 7.1, в сигналы для обв соответствующем подчиненном процессорном блоке 1,2,...,1.п после завершения им своей программы, непосредственно перед установкой в единицу бищей шины 2 системы, обеспечивающие по-,, та Готовность в своем регистре 8.2,

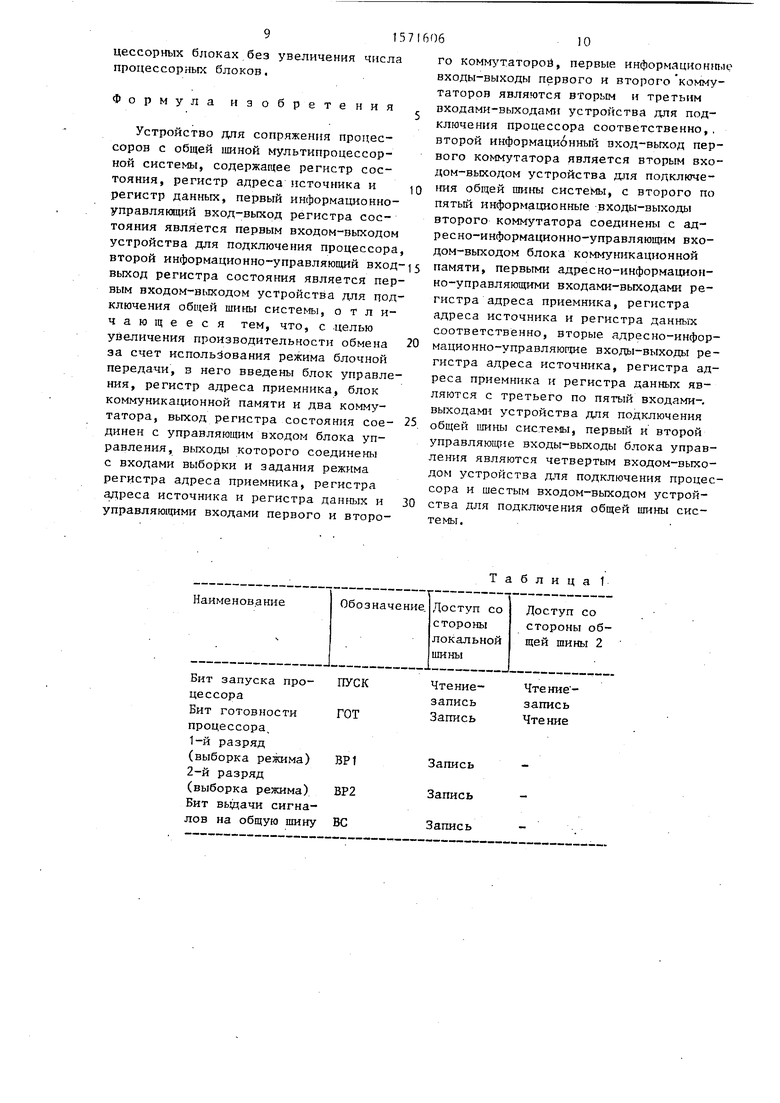

очередное выполнение циклов чтения и записи. Управляющие сигналы на локальной шине 7.1 формируются в процессе выполнения программы, соответствующей алгоритму, показанному на фиг.4. 0

При выполнении программы должно осуществляться 2Р; циклов чтения блока 6.1 локальной памяти, кроме того, подсчет числа передаваемых слов, а

...,8.п состояния.

В данной системе на шаге обмена информацией процессы передачи одного массива данных по общей шине 2 между двумя процессорными блоками совмеща- щаются с подготовкой информации для передачи следующего массива данных в другой подчиненный процессорный блок. Следовательно,, на передачу одтакже засылка в конце программы адре- 5 ного слова по общей шине 2 использует-

са регистра 15.К данных подчиненного процессорного блока 1.К в регистр 14.1 адреса приемника.

С помощью блока 9.1 управления сигся в среднем два цикла обращения к общей шине 2 (Чтение и Запись). Система имеет однотипные процессорные блоки, что уменьшает аппаратурные, эаналы, формирующиеся при чтении блока 6 ,1 go траты и упрощает резервирование уст- локальной памяти, преобразуются в

ройств системы.

сигналы, которые обеспечивают поочередно циклы чтения и записи для общей шины 2. При выполнении цикла Чтение осуществляется чтение данных из реги- -, стра 15.1 данных источника и занесения их в регистр 15.1 данных коммуникационного процессорного блока 1.1. В цикле Запись информация из регистчитаемого слова). За счет этого подготавливается адрес слова, которое будет читаться из блока 12.1 коммуникационной памяти при следующем обращении к этому процессорному блоку.

При записи информации в регистр 15.J данных приемника информация записывается в блок 12.J коммуникационной памяти по адресу, находящемуся в регистре 14.J адреса. Как и при чтении, содержимое этого регистра увеличивается на единицу, подготавливая адрес для блока 12.J коммуникационной памяти для записи следующего слова.

Начальные адреса передаваемого и

в соответствующем подчиненном процессорном блоке 1,2,...,1.п после завершения им своей программы, непосредственно перед установкой в единицу би...,8.п состояния.

В данной системе на шаге обмена информацией процессы передачи одного массива данных по общей шине 2 между двумя процессорными блоками совмеща- щаются с подготовкой информации для передачи следующего массива данных в другой подчиненный процессорный блок. Следовательно,, на передачу одся в среднем два цикла обращения к общей шине 2 (Чтение и Запись). Система имеет однотипные процессорные блоки, что уменьшает аппаратурные, эатраты и упрощает резервирование уст-

ройств системы.

Таким образом, изобретение позволяет упростить аппаратуру без снижения быстродействия (по сравнению с системами, содержащими коммуникационный процессор, т.е. содержащими блоки разных типов), а также повысить производительность систем на однотипных про

9157

цессорных блоках без увеличения числа процессорных блоков.

Формула изобретения

Устройство для сопряжения процессоров с общей шиной мультипроцессорной системы, содержащее регистр состояния, регистр адреса источника и регистр данных, первый информационно- управляющий вход-выход регистра состояния является первым входом-выходом устройства для подключения процессора, второй информационно-управляющий входвыход регистра состояния является первым входом-выходом устройства для подключения общей шины системы, отличающееся тем, что, с целью увеличения производительности обмена за счет использования режима блочной передачи, в него введены блок управления, регистр адреса приемника, блок коммуникационной памяти и два коммутатора, выход регистра состояния соединен с управляющим входом блока управления, выходы которого соединены с входами выборки и задания режима регистра адреса приемника, регистра адреса источника и регистра данных и управляющими входами первого и второ

Бит запуска про- цессора

Бит готовности процессора, 1-й разряд

(выборка режима) 2-й разряд

(выборка режима) Бит выдачи сигналов на общую шину

606

10

5 0

5

0

го коммутаторов, первые информационные входы-выходы первого и второго коммутаторов являются вторым и третьим входами-выходами устройства для подключения процессора соответственно,. второй информацибнный вход-выход первого коммутатора является вторым входом-выходом устройства для подключения общей шины системы, с второго по пятый информационные входы-выходы второго коммутатора соединены с ад- ресно-информационно-управляющим входом-выходом блока коммуникационной памяти, первыми адресно-информацион- но-управляющими входами-выходами регистра адреса приемника, регистра адреса источника и регистра данных соответственно, вторые адресно-инфор- мационно-управляющие входы-выходы регистра адреса источника, регистра адреса приемника и регистра данных являются с третьего по пятый входами-, выходами устройства для подключения общей шины системы, первый и второй управляющие входы-выходы блока управления являются четвертым входом-выходом устройства для подключения процессора и шестым входом-выходом устройства для подключения общей шины системы.

Таблица 1

Чтение запись

Чтение

Запись Запись Запись

К локальной шине U

Таблица2

Фиг.3

( Начало

Пустая комнда

Нет

Засылка в К1 длины. следующего масс ибо

Шылка б R3 адрес а регистра данных

M+RAnp /74. f)

С Конец }

Фиг.4

г

ти

ш

Фиг. 5

Ш

ill

(2.1

t t

Фиг.6

,19.1

/4.1

/X/

fO.i

V

t

tl

Фиг.7

D ID

a/

n

Фиг 8

| Вейцман К | |||

| Распределение системы мини- и микроЭВМ | |||

| И.: Финансы и статистика, 1983, с | |||

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

| Хвощ С.Т | |||

| Микропроцессоры и микро- ЭВМ в системах автоматического управления | |||

| Л.: Машиностроение, 1987, с | |||

| АВТОМАТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ПОДАЧИ УГЛЯ К ТОПКАМ | 1920 |

|

SU297A1 |

| Патент США № 4523272, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1990-06-15—Публикация

1988-08-11—Подача