Изобретение относится к автоматике.

Известен цифровой регулятор мощности, состоящий из вентильного преобразователя, нуль-органа, блока задания регулируемого параметра, двух регистров

кода, регистра остатка, триггера, двух элементов И, двух коммутаторов, сумматора, вычитающего счетчика импульсов, генератора импульсов, распределителя импульсов, аналого-цифрового преобразователя.

элемента ИЛИ, датчика обратной связи и вычитателя,

Целью изобретения является повышение качества регулирования, путем обеспечения равномерного поступления в нагрузку полуволн сетевого напряжения с изменяемым диапазоном регулирования, тиристорного устройства для регулирования мощности.

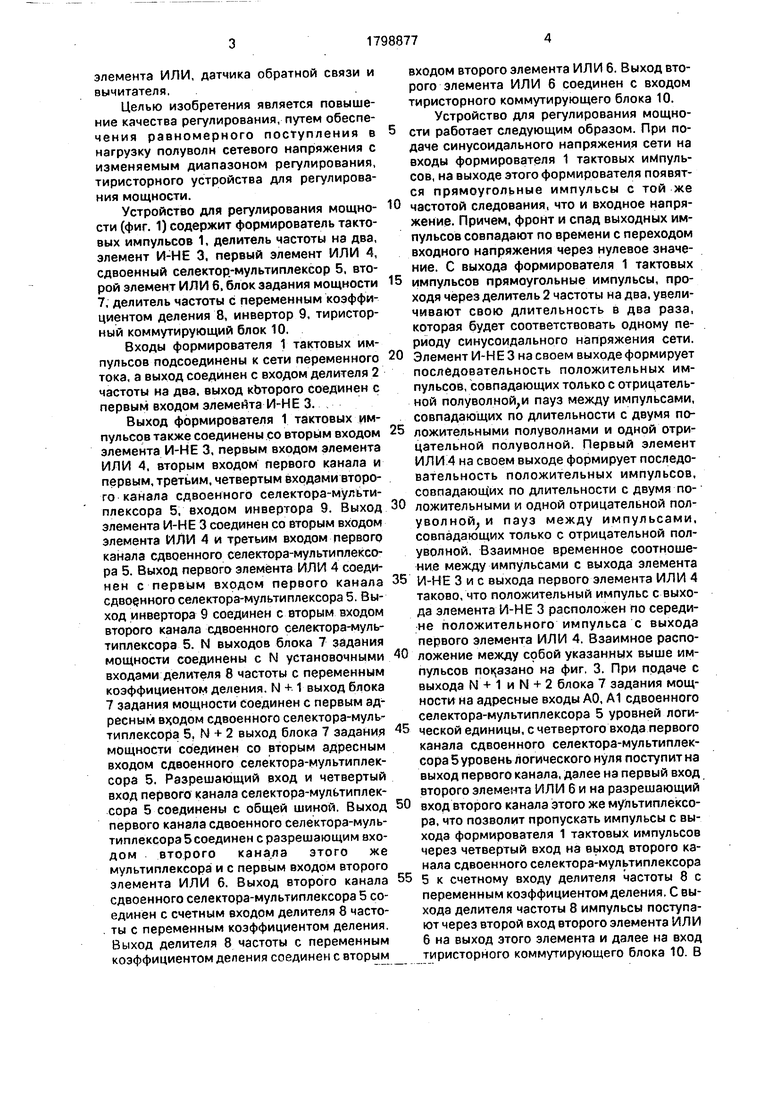

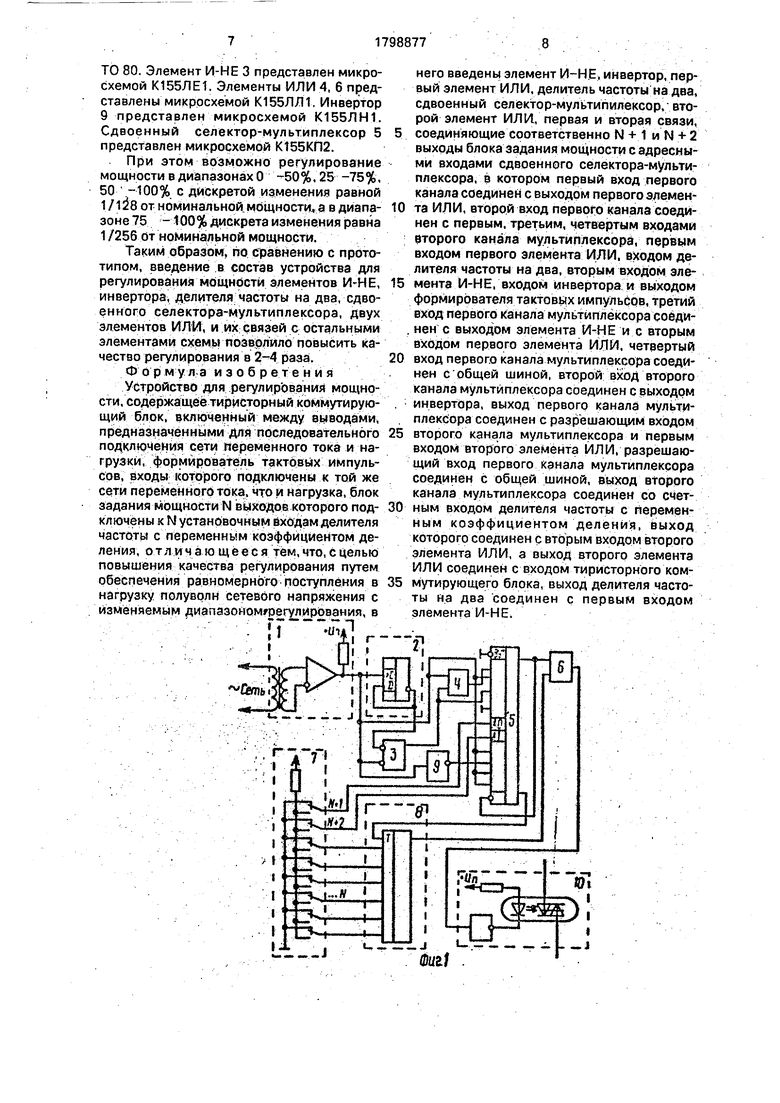

Устройство для регулирования мощности (фиг. 1) содержит формирователь тактовых импульсов 1, делитель частоты на два, элемент И-НЕ 3, первый элемент ИЛИ 4, сдвоенный селектор-мультиплексор 5, второй элемент ИЛИ 6, блок задания мощности 7, делитель частоты с переменным коэффициентом деления 8, инвертор 9, тиристор- ный коммутирующий блок 10.

Входы формирователя 1 тактовых импульсов подсоединены к сети переменного тока, а выход соединен с входом делителя 2 частоты на два, выход которого соединен с первым входом элемейта И-НЕ 3. ,

Выход формирователя 1 тактовых импульсов также соединены со вторым входом элемента И-НЕ 3, первым входом элемента ИЛИ 4, вторым входом первого канала и первым, третьим, четвертым входами второго канала сдвоенного селектора-мультиплексора 5, входом инвертора 9. Выход элемента И-НЕ 3 соединен со вторым входом элемента ИЛИ 4 и третьим входом первого канала сдвоенного селектора-мультиплексора 5. Выход первого элемента ИЛИ 4 соединен с первым входом первого канала сдвоенного селектора-мультиплексора 5. Выход инвертора 9 соединен с вторым входом второго канала сдвоенного селектора-мультиплексора 5. N выходов блока 7 задания мощности соединены с N установочными входами делителя 8 частоты с переменным коэффициентом деления. N + 1 выход блока 7 задания мощности соединен с первым адресным входом сдвоенного селектора-мультиплексора 5, N + 2 выход блока 7 задания мощности соединен со вторым адресным входом сдвоенного селектора-мультиплексора 5. Разрешающий вход и четвертый вход первого канала селектора-мультиплексора 5 соединены с общей шиной. Выход первого канала сдвоенного селектора-мультиплексора 5 соединен с разрешающим вхо- дом второго канала этого же мультиплексора и с первым входом второго элемента ИЛИ 6. Выход второго канала сдвоенного селектора-мультиплексора 5 соединён с счетным входом делителя 8 часто- . ты с переменным коэффициентом деления. Выход делителя 8 частоты с переменным коэффициентом деления соединен с вторым

входом второго элемента ИЛИ 6. Выход второго элемента ИЛИ 6 соединен с входом тиристорного коммутирующего блока 10. Устройство для регулирования мощности работает следующим образом. При подаче синусоидального напряжения сети на входы формирователя 1 тактовых импульсов, на выходе этого формирователя появятся прямоугольные импульсы с той же

0 частотой следования, что и входное напряжение. Причем, фронт и спад выходных импульсов совпадают по времени с переходом входного напряжения через нулевое значение. С выхода формирователя 1 тактовых

5 импульсов прямоугольные импульсы, проходя через делитель 2 частоты на два, увеличивают свою длительность в два раза, которая будет соответствовать одному периоду синусоидального напряжения сети.

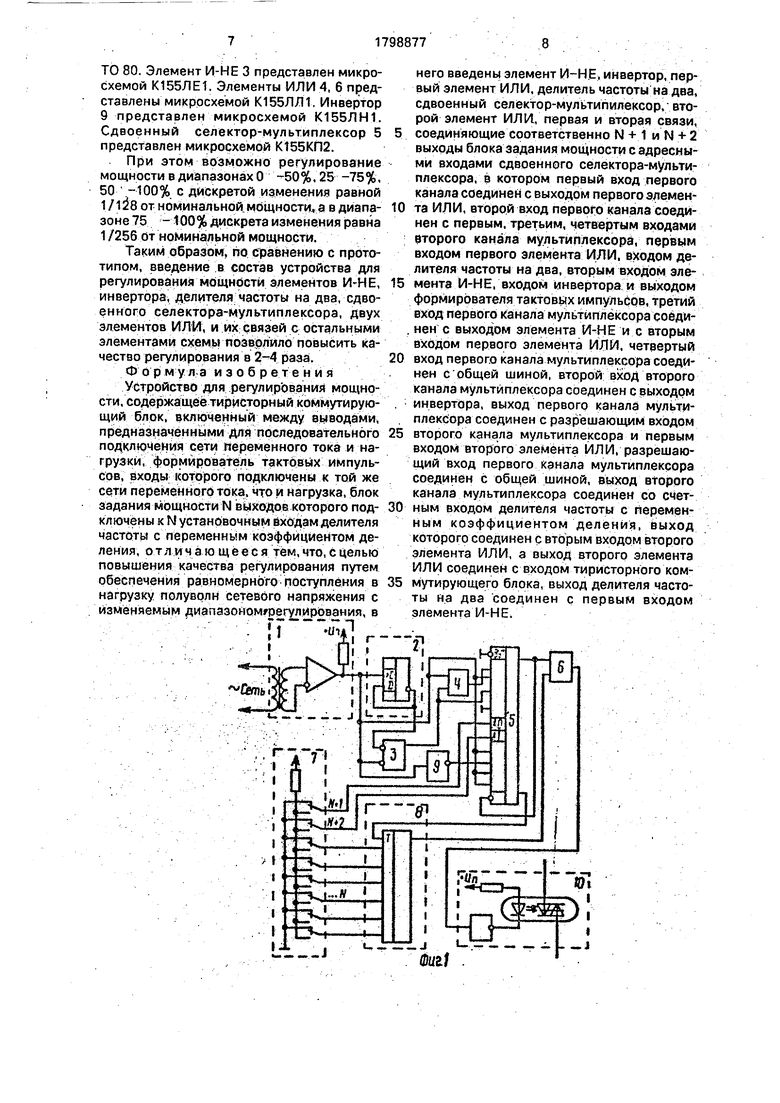

0 Элемент И-НЕЗ на своем выходе формирует последовательность положительных импульсов, совпадающих только с отрицательной полуволной,и пауз между импульсами, совпадающих по длительности с двумя по5 ложительными полуволнами и одной отрицательной полуволной. Первый элемент ИЛИ4 на своем выходе формирует последовательность положительных импульсов, совпадающих по длительности с двумя по0 ложительными и одной отрицательной пол- уволной, и пауз между импульсами, совпадающих только с отрицательной полуволной. Взаимное временное соотношение между импульсами с выхода элемента

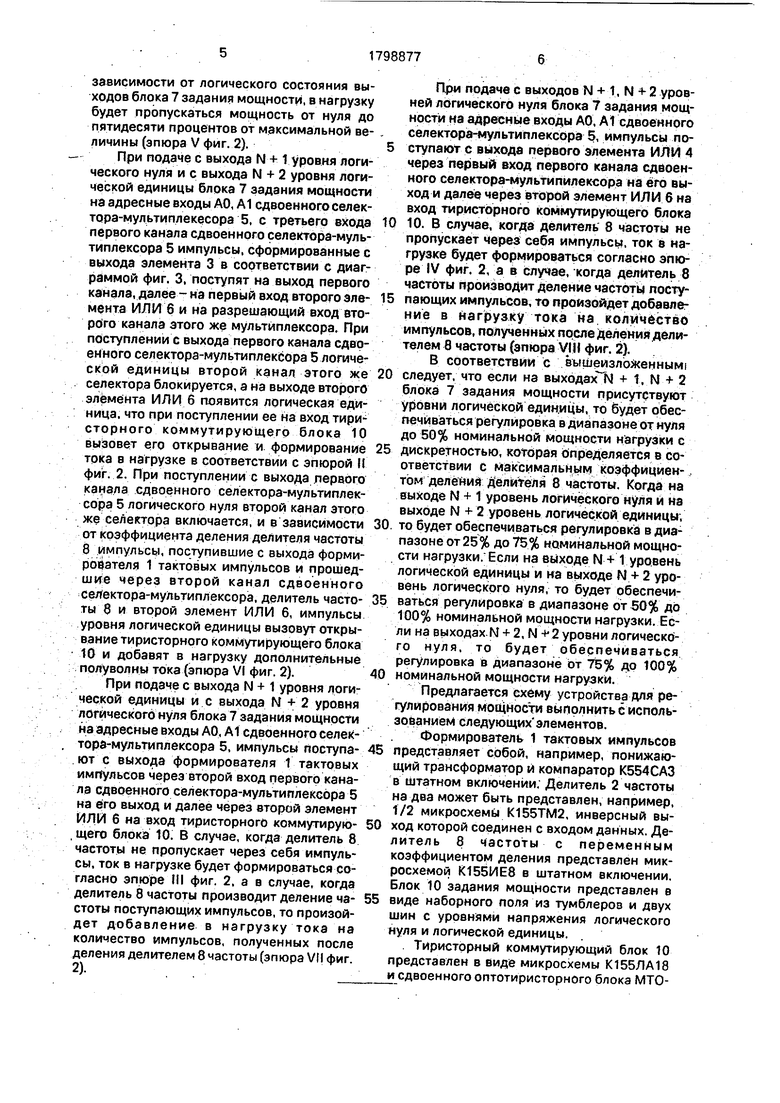

5 И-НЕ 3 и с выхода первого элемента ИЛИ 4 таково, что положительный импульс с выхода элемента И-НЕ 3 расположен по середине положительного импульса с выхода первого элемента ИЛИ 4. Взаимное распо0 ложение между собой указанных выше импульсов показано на фиг. 3. При подаче с выхода N + 1 и N + 2 блока 7 задания мощности на адресные входы АО, А1 сдвоенного селектора-мультиплексора 5 уровней логи5 ческой единицы, с четвертого входа первого канала сдвоенного селектора-мультиплексора 5 уровень логического нуля поступит на выход первого канала, далее на первый вход второго элемента ИЛИ 6 и на разрешающий

0 вход второго канала этого же мультиплексора, что позволит пропускать импульсы с выхода формирователя 1 тактовых импульсов через четвертый вход на выход второго канала сдвоенного селектора-мультиплексора

5 5 к счетному входу делителя частоты 8 с переменным коэффициентом деления, С выхода делителя частоты 8 импульсы поступают через второй вход второго элемента ИЛИ б на выход этого элемента и далее на вход тиристорного коммутирующего блока 10. В

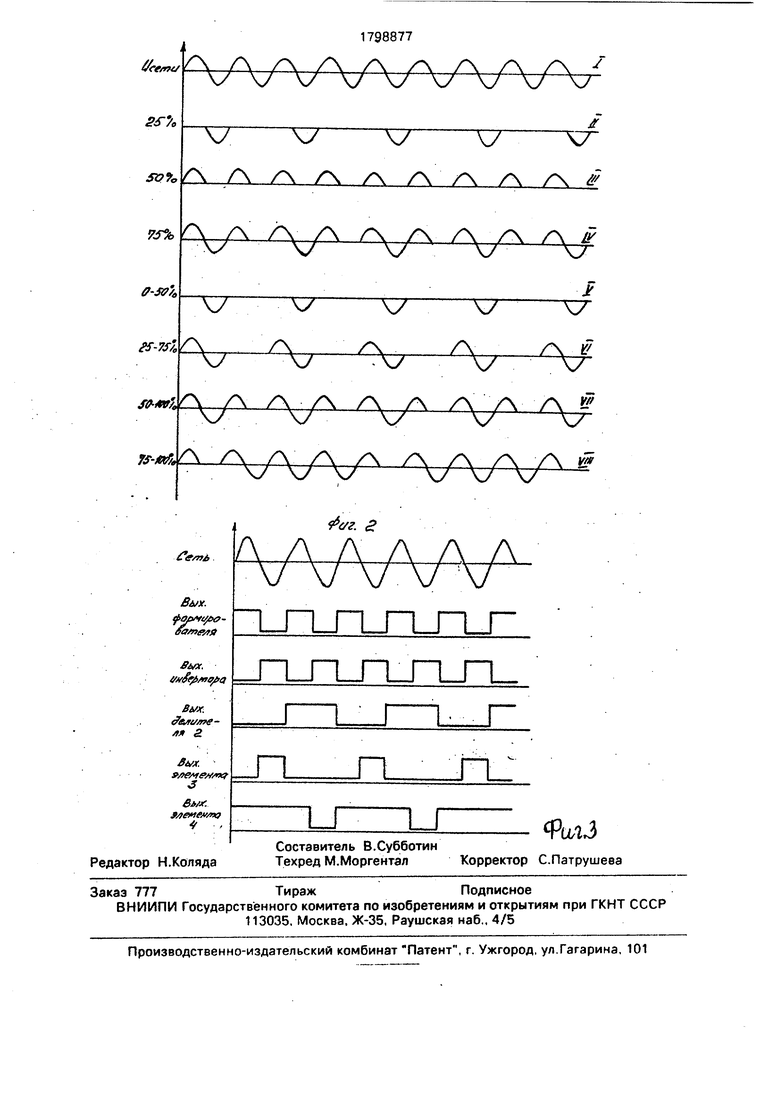

зависимости от логического состояния выходов блока 7 задания мощности, в нагрузку будет пропускаться мощность от нуля до пятидесяти процентов от максимальной величины (эпюра V фиг. 2).

При подаче с выхода N + 1 уровня логического нуля и с выхода N + 2 уровня логической единицы блока 7 задания мощности на адресные входы АО, А1 сдвоенного селек- тора-мультиплекесора 5, с третьего входа первого канала сдвоенного селектора-мультиплексора 5 импульсы, сформированные с выхода элемента 3 в соответствии с диаграммой фиг. 3, поступят на выход первого канала, далее - на первый вход второго элемента ИЛИ б и на разрешающий вход второго канала этого же мультиплексора. При поступлении с выхода первого канала сдвоенного селектора-мультиплексора 5 логической единицы второй канал этого же селектора блокируется, а на выходе второго элемента ИЛИ б появится логическая единица, что при поступлении ее на вход тиристорного коммутирующего блока 10 вызовет его открывание и формирование тока в нагрузке в соответствии с эпюрой It фиг. 2. При поступлении с выхода первого канала сдвоенного селектора-мультиплексора 5 логического нуля второй канал этого же селектора включается, и в зависимости от коэффициента деления делителя частоты 8 импульсы, поступившие с выхода формирователя 1 тактовых импульсов и прошедшее через второй канал сдвоенного селектора-мультиплексора, делитель частоты 8 и второй элемент ИЛИ 6, импульсы уровня логической единицы вызовут открывание тиристорного коммутирующего блока 10 и добавят в нагрузку дополнительные полуволны тока (эпюра VI фиг. 2).

При подаче с выхода N + 1 уровня логической единицы и с выхода N + 2 уровня логического нуля блока7 задания мощности на адресные входы АО, А1 сдвоенного селектора-мультиплексора 5, импульсы поступа- . ют с выхода формирователя 1 тактовых импульсов через второй вход первого канала сдвоенного селектора-мультиплексора 5 на его выход и далее через второй элемент ИЛИ 6 на вход тиристорного коммутирую- . щего блока 10. В случае, когда делитель 8 частоты не пропускает через себя импульсы, ток в нагрузке будет формироваться согласно эпюре III фиг. 2, а в случае, когда делитель 8 частоты производит деление частоты поступающих импульсов, то произойдет добавление в нагрузку тока на количество импульсов, полученных после деления делителем 8 частоты (эпюра VII фиг. 2).. .

При подаче с выходов N + 1, N + 2 уровней логического нуля блока 7 задания мощности на адресные входы АО, А1 сдвоенного селектора-мультиплексора 5, импульсы по- 5 ступают с выхода первого элемента ИЛИ 4 через первый вход первого канала сдвоенного селектора-мультипилексора на его выход и далее через второй элемент ИЛИ 6 на вход тиристорного коммутирующего блока

0 10. В случае, когда делитель 8 частоты не пропускает через себя импульсы, ток в нагрузке будет формироваться согласно эпюре IV фиг. 2, а в случае, когда делитель 8 частоты производит деление частоты посту5 пающих импульсов, то произойдет добавле- ние в нагрузку тока на количество импульсов, полученных после деления делителем 8 частоты (эпюра VIU фиг. 2).

В соответствии с вышеизложенным

0 следует, что если на выходах N + 1, N + 2 блока 7 задания мощности присутствуют уровни логической единицы, то будет обеспечиваться регулировка в диапазоне от нуля до 50% номинальной мощности нагрузки с

5 дискретностью, которая определяется в соответствии с максимальным коэффициен-, том делений Делйтёли 8 чистоты. Когда на выходе N + 1 уровень логического нуля и на выходе N + 2 уровень логической единицы,

0. то будет обеспечиваться регулировка в диапазоне от 25% до 75% номинальной мощности нагрузки/Если на выходе N +1 уровень логической единицы и на выходе N + 2 уровень логического нуля, то будет обеспечи5 ваться регулировка в диапазоне от 50% до 100% номинальной мощности нагрузки. Если на выходах N + 2, N +2 уровни логического нуля, то будет обеспечиваться регулировка в диапазоне от 75% до 100%

.0 номинальной мощности нагрузки.

Предлагается схему устройства для регулирования мощности выполнить с использованием следующих элементов. . Формирователь 1 тактовых импульсов

5 представляет собой, например, понижающий трансформатор и компаратор К554САЗ в штатном включении; Делитель 2 частоты на два может быть представлен, например, 1/2 микросхемы К155ТМ2, инверсный вы0 ход которой соединен с входом данных, Делитель 8 частоты с переменным коэффициентом деления представлен микросхемой К155ИЕ8 в штатном включении. Блок 10 задания мощности представлен в

5 виде наборного поля из тумблеров и двух шин с уровнями напряжения логического нуля и логической единицы.

. Тиристорный коммутирующий блок 10 представлен в виде микросхемы К155ЛА18 и сдвоенного оптотиристорного блока МТОТО 80. Элемент И-НЕ 3 представлен микросхемой К155ЛЕ1. Элементы ИЛИ 4, 6 представлены микросхемой К155ЛЛ1, Инвертор 9 представлен микросхемой К155ЛН1. Сдвоенный селектор-мультиплексор 5 представлен микросхемой К155КП2.

При этом возможно регулирование мощности в диапазонах 0 -50%, 25 -75%, 50 -100% с дискретой изменения равной от номинальной мощности, а в диапа- зоне 75. -100% дискрета изменения равна 1 /256 от номинальной мощности.

Таким образом, по сравнению с прототипом, введение в состав устройства для регулирования мощности элементов И-НЕ, инвертора, делителя частоты на два, сдвоенного селектора-мультиплексора, двух элементов ИЛИ, и их связей с остальными элементами схемы позволило повысить качество регулирования в 2-4 раза.

Ф 0 р мул а изобретения

Устройство для регулирования мощности, содержащее тиристорный коммутирую- щий блок, включенный Между выводами, предназначенными для последовательного подключения сети Переменного тока и нагрузки, формирователь тактовых импульсов, входы которого подключены к той же сети переменного тока, что и нагрузка, блок заданий мощности N выходов которого под- ключены к N установочным входам делителя частоты с переменным коэффициентом деления, отличающееся тем,что.сцелью повышения качества регулирования путем обеспечения равномерного поступления в нагрузку полуволн сетевого напряжения с изменяемым диапазономгрегулирования, в

него введены элемент И-Н.Е, инвертор, первый элемент ИЛИ, делитель частоты на два, сдвоенный селектор-мультипилексор, второй элемент ИЛИ., первая и вторая связи, соединяющие соответственно N + 1 и N + 2 выходы блока задания мощности с адресными входами сдвоенного селектора-мультиплексора, в котором первый вход первого канала соединен с выходом первого элемента ИЛИ, второй вход первого канала соединен с первым, третьим, четвертым входами второго канала мультиплексора, первым входом первого элемента ИЛИ, входом делителя частоты на два, вторым входом элемента И-НЕ, входом инвертора и выходом формирователя тактовых импульсов, третий вход первого канала мультиплексора соединен с выходом элемента И-НЕ и с вторым входом первого элемента ИДИ, четвертый вход первого канала мультиплексора соединен с общей шиной, второй; вход второго канала мультиплексора соединен с выходом инвертора, выход первого канала мультиплексора соединен с разрешающим входом второго канала мультиплексора и первым входом второго элемента ИЛИ, разрешающий вход первого канала мультиплексора соединен с общей шиной, выход второго канала мультиплексора соединен со счетным входом делителя частоты с переменным коэффициентом деления, выход которого соединен с вторым входом второго элемента ИЛИ, а выход второго элемента ИЛИ соединен с входом тиристорного коммутирующего блока, выход делителя частоты на два соединен с первым входом элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМЫЙ ГЕНЕРАТОР ИМПУЛЬСОВ | 1992 |

|

RU2019907C1 |

| Цифровой следящий электропривод | 1985 |

|

SU1308982A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| СПОСОБ УПРАВЛЕНИЯ ГРУППОЙ ИМПУЛЬСНЫХ ПРЕОБРАЗОВАТЕЛЕЙ | 1983 |

|

SU1284443A1 |

| @ -Разрядный распределитель импульсов | 1984 |

|

SU1231495A1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ С МНОЖЕСТВЕННЫМ ДОСТУПОМ И ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2003 |

|

RU2240653C1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1982 |

|

SU1077539A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ С АВТОНОМНЫМ ИНДУКТОРОМ | 2005 |

|

RU2291548C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Электропривод | 1979 |

|

SU928574A1 |

Использование: изобретение относится к области автоматики. Сущность изобретения: устройство содержит тиристррный коммутирующий блок 10, включенный между выводами, предназначенными для последовательного подключения сети переменного тока к нагрузке, формирователь тактовых импульсов, входы которого подключены к той же сети переменного тока, что и нагрузка, блок задания мощности, N выходов которого подключены к N установочным входам делителя частоты с переменным коэффициентом деления. Новым в устройстве является то, что введены элемент И-НЕ, инвертор, первый элемент-ИЛИ, сдвоенный селектор- мультиплексор, второй элемент ИЛИ. С адресными входами сдвоенного селектора-мультиплексора соединены соответственно (N + 1)-й и (N + 2}-й выходы блока задания мощности. В селекторе-мультиплексоре первый вход первого канала соединен с выходом первого элемента ИЛИ, второй вход первого канала соединен с первым, третьим, четвертым входами второго канала, первым входом первого элемента ИЛИ входом делителя частоты на два, вторым входом элемента И-НЕ, входом инвертора. Выход делителя 2 частоты на два соединен с первым входом элемента 3 И- НЕ, Третий выход первого канала селектора-мультиплексора соединен с выходом элемента И-НЕ и с вторым входом первого элемента ИЛИ. Четвертый вход первого канала селектора-мультиплексора соединен с общей шиной. Второй вход второго канала селектора-мультиплексора соединен с выходом инвертора. Выход первого канала селектора-мультиплексора соединен с разрешающим входом второго канала этого же селектора-мультиплексора и первым входом второго элемента ИЛИ. Разрешающий вход первого канала селектора-мультиплексора соединен с общей шиной. Выход второго канала селектора-мультиплексора соединен со счётным входом делителя частоты с переменным коэффициентом деления, выход которого.соединен с вторым входом второго элемента ИЛИ, а выход второго элемента ИЛИ соединяется с входом тирйсторного коммутирующего блока. 3 ил. Ч| Ю 00 00 Ч VI

| Цифровой регулятор мощности | 1986 |

|

SU1372276A1 |

| Импульсный регулятор мощности | 1986 |

|

SU1339531A1 |

| кл | |||

| СПОСОБ ПРИГОТОВЛЕНИЯ РУДНО-УГОЛЬНЫХ БРИКЕТОВ | 1922 |

|

SU605A1 |

| Журнал Радио, 1986, № 4, с | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

Авторы

Даты

1993-02-28—Публикация

1990-07-09—Подача