счетчик, восемь элементов И, два элемента НЕ, триггер и три элемен та задержки, при этом информационные входы коммутатора и счетчика образуют первьй вход, блока, информационные выходь счетчика соединены с управляющими входами коммутатора, управляющий вход счетчикасоединен с выходом первого элемента: И, первьй вход которого и первый вход второго элемента И соединены с первым выходом триггера:, выход коммутатора соединен с вторым входом второго элемента И, выход которого соединен с первым входом третьего элемента И выход которого является разрешаюпщм выходом ,блока, выход счетчика соединен с первым входом четвертого элемента И, выход которого, соединен с вторым входом первого элемента И и является ВЫХОДОМ Оконча1ше слова блока, первые входы цятого и шестого элементов И соединены соответственно с лервым и вторым выxoдa ш триггера, первый и второй входы которого соединены соответственно с выходамл седьмого и восьмого элементов И, второй вход четвертого элемента 11 через первый элемент задержки соедгчен с выходом второго эле93655

мента задержки, соединенным с вторы-ми входами третьего, пятого и шестого эльментов И, выходы пятого и шестого элементов И являются соответственно выходами Верно и Неверно блока, четвертый вход блока соединен с входом второго элемента задержки и через третий элемент задержки - с первыми входами седьмого и восьмого элементов И, второй и тре.тий входы восьмого элемента И соединены с вторьм и третьим входами блока, через первый и второй элементы НЕ соединенными с вторым и третьим входами седьмого элемента И.

2. Преобразователь по п.1, о т л и ч а ющ ийс я тем, что формирователь сигнала запроса содержит де-шнфратор, триггер и элемент И, при-.

.чем тактовьш, запускающий и стробирующий входы формирователя соединенны С группой входов дешифратора, первый и второй выходы -которого со единены с R - и S входами тригге-

ра, выход которого соединен с пер. вым входом элемента И, второй вход и выход которого соединены соответственно с тактовым входом н выходом формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМПУЛЬСНЫЙ КОДОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2248607C1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Приемник последовательного кода | 1988 |

|

SU1674378A1 |

| Преобразователь последовательного биполярного кода в параллельный униполярный код | 1989 |

|

SU1695511A1 |

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1438007A2 |

| Дешифратор времяимпульсных кодов | 1991 |

|

SU1807562A1 |

| Устройство для формирования и передачи сообщения | 1990 |

|

SU1778767A1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Преобразователь последовательного кода в параллельный | 1985 |

|

SU1283980A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

1 .ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ, содержащий генератор тактовых импульсов, регистр сдвига, выходной регистр, блок управления, регистр команды, причем информационный вход регистра сдвига соединен с первым информационным входом преобразователя, вход регистра команды является входом задания режима преобразователя, а первый выход соединен с первым входом блока управления, разрешакнций выход которого соединен с управляющим входом выходного регистра, выход которого является информационным выходом преобразователя, отличающийся тем, что, с целью повышения достоверности работы, в него введены схема сравнения, первый и второй вычитающие счетчики, узел контроля на нечетность, два элемента ИЛИ, триггер, элемент ИС1ШЮЧАЮЩЕЕ ИЛИ и формирователь сигнала запроса, причем первый и второй информационные входы преобразователя через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом регистра команды, а выход - со сдвиговыми входами регистра сдвига и счетным входом первого вычитающего счетчика, вход сброса которого и входы сброса триггера второго вычитающего счетчика и узла контроля на нечетность соединены с выходом второго элемента ИЛИ, первьй вход которого соединен с выходом Окончание слова блока упрашлення, а второй вход является входом запуска преобразователя, первый информационный вход которого соединен с информационным входом узла контроля на нечетность, выход которого соединен с вторым входом блока управления, третий вход которого соединен с выходом схемы сравнения, первый и второй входы которой соединены соответ(Л ственно с выходом первого и первым с выходом второго вычитающих счетчиков , выход регистра команды соединен с управляющим входом регистра сдвига, выход которого соединен с информационным входом выходного регистра, вьсход генератора тактовых со со импульсов соединен с тактовым входом формирователя сигнала запроса, Од вход запуска и стробирующий вход ко01 торого соединены соответственно с выходом триггера и первым выходом ел второго вычитающего счетчика, второй вьсход которого соединен с вторым входом триггера и четвертым входом блока управления, выход формирователя сигнала запроса соединен со счетным входом второго вычитающего счетчика и является выходом запроса преобразователя, третий и четвертый выходы блока управления являются соответственно выходами Верно и Неверно преобразователя, причем блок управления содержит коммутатор.

. . ,

..- .

Изобретение относится к вычислительной тех1шке и автоматической передаче и преобразованию данных и может быть использовано в системах ввода информащп в ЭВМ от источника ин-форма1.щи, находящегося на расстоянии до 200 м.

Целью изобретения является повышение достоверности работы.

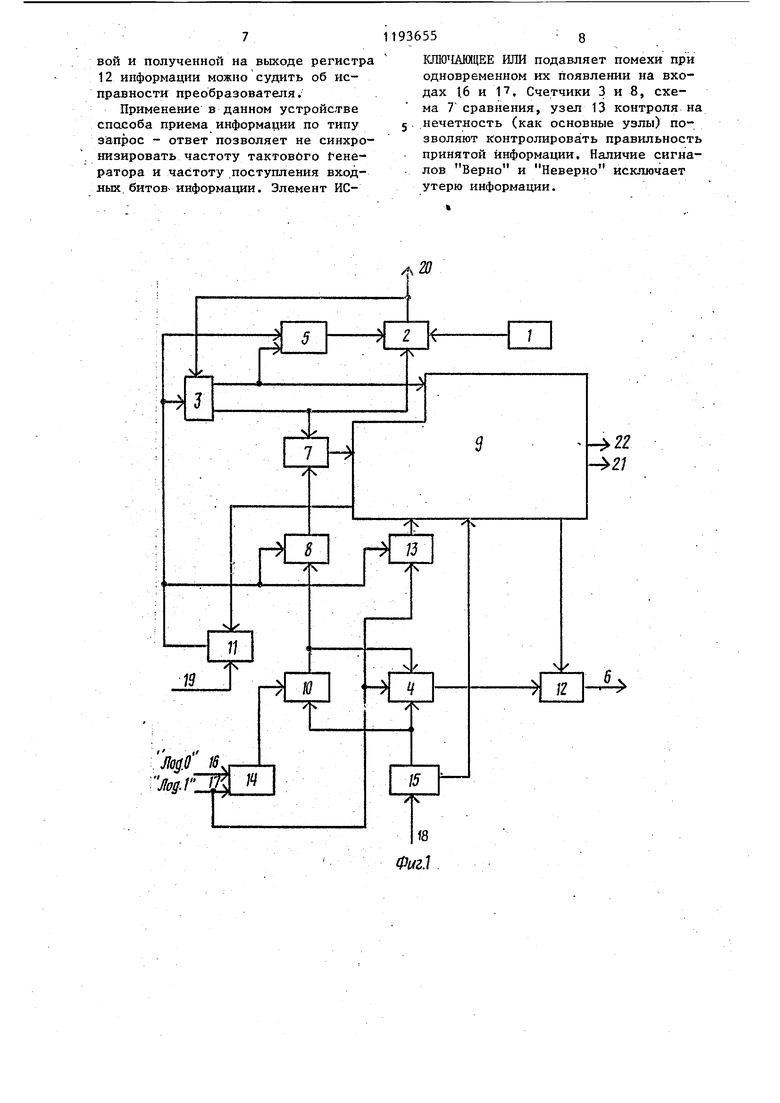

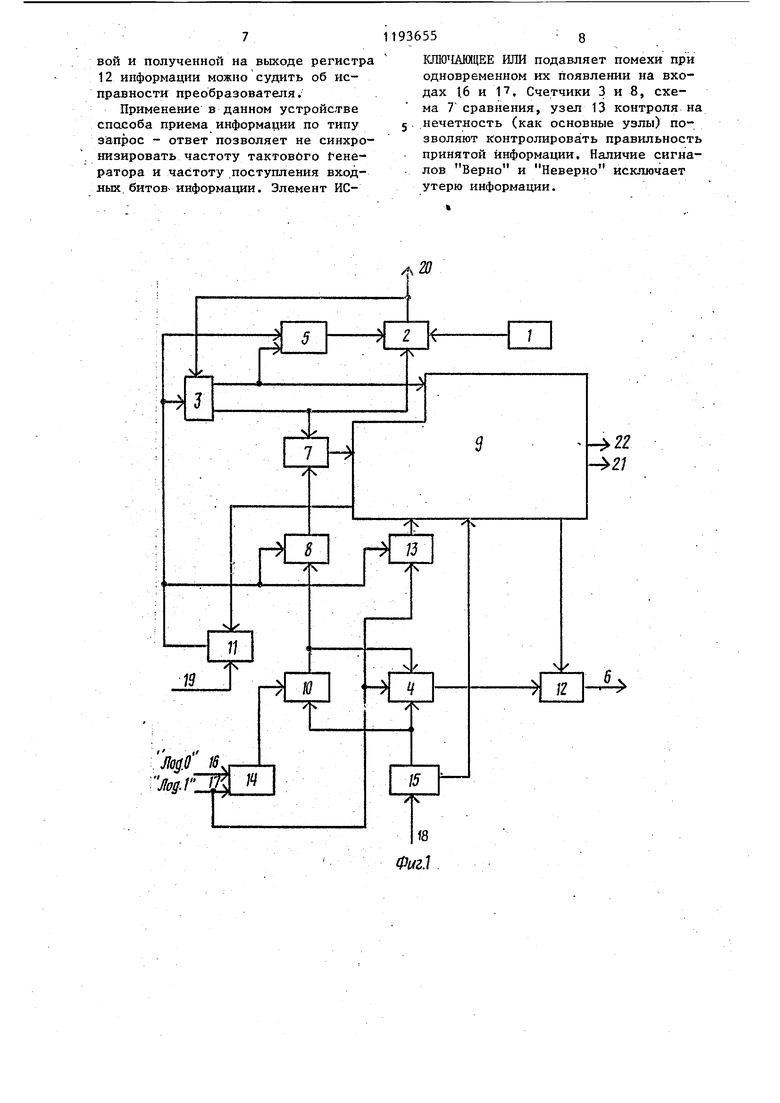

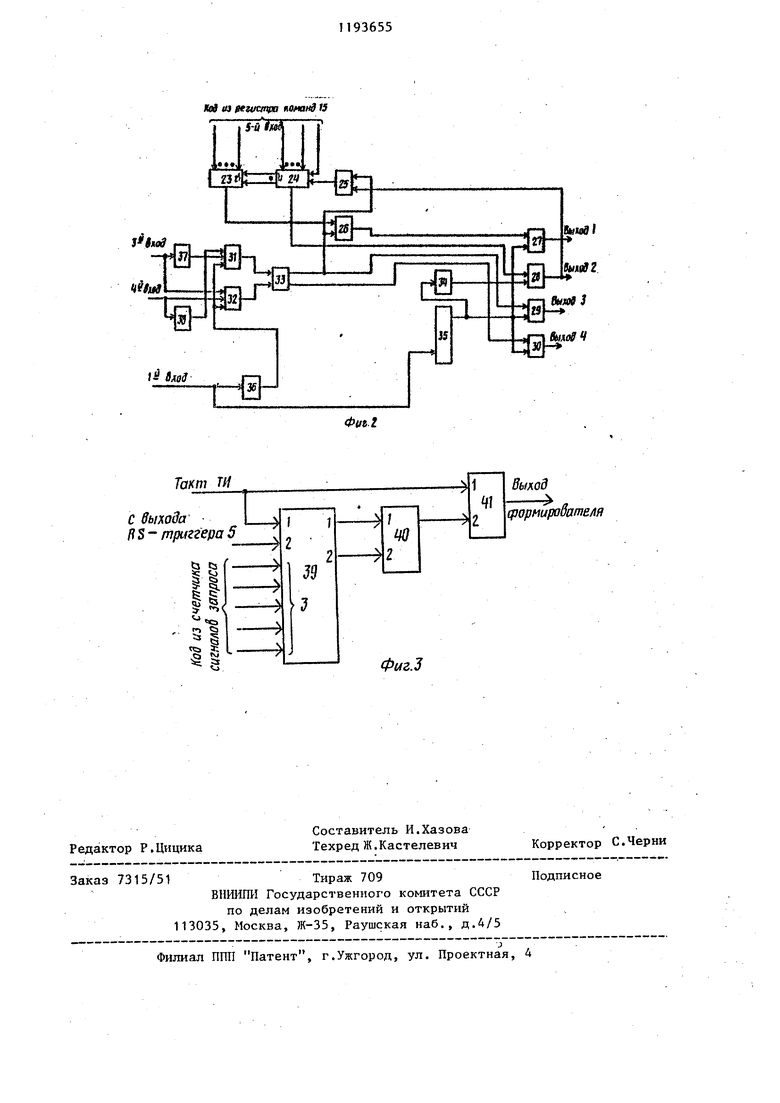

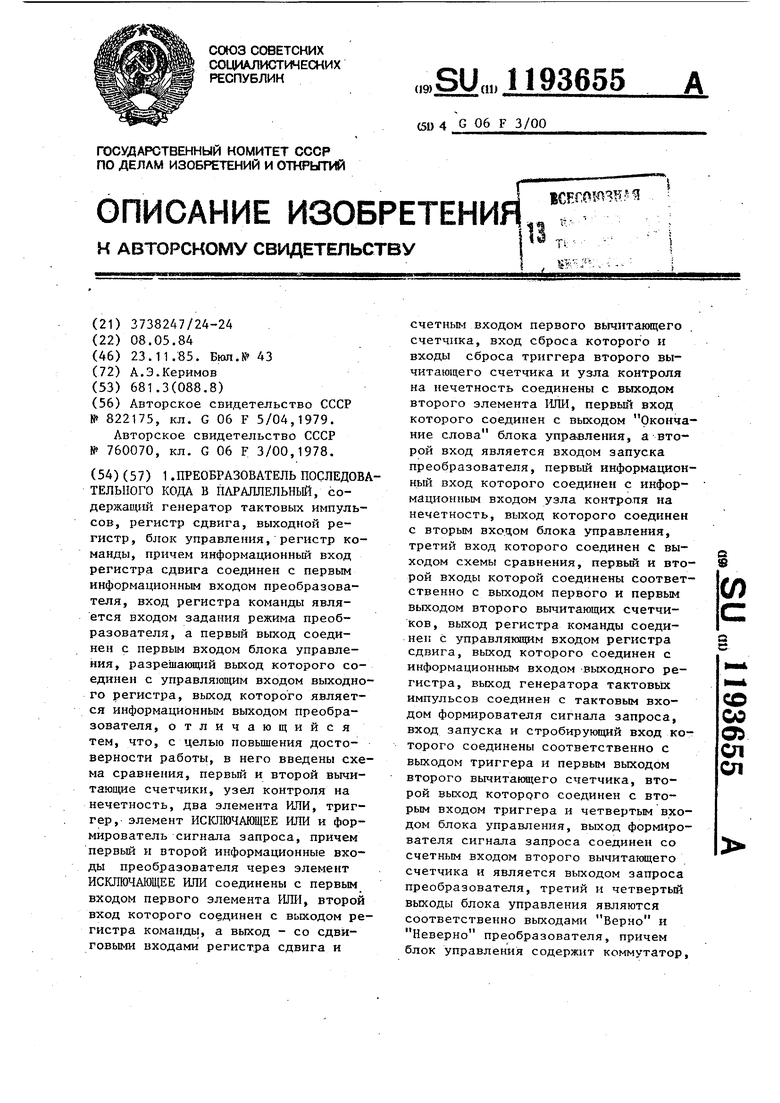

На фиг.1 показана схема преобразоват.еля; на фиг,2 - схема блока управлеьшя; на фиг.3 - схема формирователя сигнала запроса.

Преобразователь содержит генератор 1 тактовых импульсов, формирователь 2 сигналов запроса, первьй вычитаюпщй счетчик 3, регистр 4 сдви-г га, триггер 5, информационньй выход бJ схему 7 сравнения, второй вычитаощнй счетчик 8, блок 9 управления, элементы ИЛИ 10 и 11, выходной регистр 12, узел 13 контроля на нечетность, .элемент ИСКЛЮЧАЮЩЕЕ 1-ШИ 1А, регистр 15 команды, информационные входы 16 и 17, вход 18 команды, вход

19 запуска, выход 2U запроса, выходы Неверно 21 и Верно 22. .

Блок управления содержит коммутатор 23, счетчик 2А,-элементы И 2532, триггер 33, элементы 34-36 задержки, элементы FIE 37 и 38.

Формирователь сигнала запроса содержит дешифратор 39, триггер 40, элемент И 41.

Генератор 1 тактовых импульсов

предназначен для вьфаботки прямоугольных импульсов. Запуск формирователя 2 осуществляется подачей на его второй вход разрешающего сигна- . ла с триггера 5 и при наличии на

третьих входах двоичного кода 10001 (число 33,) со счетчика 3.

31

При этом на первом выходе дешифратора 39 появляется импульс, устанавливающий триггер 40 в 1. Разрешается прохождение тактовых импульсов через элемент И 41 на выход формирователя 2 сигналов запроса.

При появлении кода 00000 на входе деашфратора на его втором выходе появляется импульс, устанавливающий триггер 40 в О. Прекращается выдача сигналов запроса. Первый, второй, третий выходы формирователя 2 являются первым, вторым, третьим входами деишфратора 39.

Выход элемента И 41 является выходом формирователя 2 и.соединен с счртным входом счетчика 3.

Счетчик 3 управляет работой формирователя 2, отсчитывает количество выданных сигналов запроса и при обнулении вырабатывает стробирующий импульс.

Перед каждым циклом в счетчике 3 по первому установленному входу записывается число 10001. Счетчик работает на вычитание.

Регистр 4 сдвига предназначен для заполнения входной информацией. Выходы регистра 4 соединены с вторыми входами выходного регистра. Триггер 5 предназначен для выдачи разрешающего сигнала на формирователь 2 сигналов запроса при поступлении на его первый вход сигнала элемента ИЛИ .11.

Схема 7 сравнения сравнивает коды, поступающие со счетчиков 3 и 8, при равенстве на его выходе 1.

Счетчик 8 предназначен для подсчитывания количества информационных битов, поступающих на первые входы 17 и 16 устройства, т.е. сигналов Лог.1 и Лог.О, соответственно.

Счетчик 8 работает на вычитание, предварительно по установочному входу в него записывается число 10001. Счетные выходы счетчика 8 соединены с вторыми входами схемы 7 сравнения.

БЛОК 9 управления принимает код команды из регистра 15 команд и записывает в счетчик 24. В коде, записанном в счетчик, указывается количество информационных слов которые необходимо принять от источника информации, в коде, поступающем на выходы коммутатора 23, указывается порядок перезаписи информации из регистра 12 сдвига. Изменяя свое со936554

стояние, счетчик 24 подключает один из входов коммутатора 23 на его вы:ход. При обнулении счетчик 24 вьща-ет на свой второй выход сигнал О, 5 означающий конец приема информации. После приема 33-х импульсов схема 7 сравнения и узел 13 контроля на нечетность выдают сигналы 1 и на третий и второй входы блока 9 управ-

10 ления, а счетчик 3 вьщает стробирующ 1й импульс на четвертый вход. Элемент 36 задержки увеличивает длительность входного импульса. На входе лемента И 32 появляется сигнал,

15 устанавливающий триггер 33 в 1.. При отсутствии сигналов от схемы 7 сравнения и (или) узла 13 контроля на нечетность появляется сигнал на выходе элемента И 31, устанавливающий триггер 33 в О. Это состояние означает неправильность приема информации. Выходы элементов И 27-30 являются выходами блока 9 упр вления.

25 Выходной регистр J2 предназначен для приема информационных слов из регистра сдвига и хранения их в течение цикла приема одного информа- . |ционного слова.

Узел 13 контроля на нечетность

30 проверяет принятьп информационный код на нечетность. При правильной передаче и приеме в информационном коде всегда будет количество 1 нечетное, поэтому в данном устройстве в качестве схемы, реализующей функцию проверки на нечетность, может служить триггер со счетным входом и установкой в О.

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14 предназначен для формирова шя тактовых сдвигающих импульсов, необходимых для продвижения информации в регистре 4 сдвига. Он исключает появление на выходе сигнала при одновременном появлении сигналов, т.е. помех, на двух ее входах.

Регистр 15 команд служит для приема команды из ЭВМ, хранения ее и выдачи в блок 9 управления, а в

0 автономном режиме вьщает тестовую программу, проверки преобразователя, т.е. служит имитатором источника информации .

Устройство работает следующим образом.

Б регистр 15 команд из памяти ЭВМ по входу 18 заносится команда ввода, в которой указывается порядок пере-

информации из регистра 4 сдвига, количество информационных слов и разрядов в слове и другие признаки. В зависимости от вида принимаемой информации на первый вход блока 9 из , регистра 15 передаются соответствующие коды. Заполнение регистра 4 сдвига происходит полностью зз каждом цикле. Заполнение выходного регистра 12 может происходить не в каждом дик- ю ле .

С небольшой задержкой относительно команды ввода на вход 19 преобразователя поступает сигнал, которьш, проходя через элемент. 1-ШИ 11, 15 записывает в счетчики 3 и 8 число 33, устанавливает в О узел 13 контроля, триггер 5 в 1. Получив разрешающий сигнал, формирователь 2 сигналов запроса выдает сигналы в источ-20 ник информащш. Счетчик 3, отсчитав 33 импульса, обнуляется. При появлении, нулевого кода на входе формирователя 2 прекращается выдача сигналов запроса, триггер 5 устанавли- 25 вается в О импульсом с выхода счетчика 3. В ответ на ка;«дый сигнал

запроса источник информации выдает на входы 16 и 17 преобразователя импульса информационного кода Лог. 30 1 или Лог.о соответственно первый импульс-контрольный бит.

Лог.1 1-ШИ Лог.о информационного кода поступает на вход эпемен- 35 та ИСКЛЮЧАЮЩЕЕ ШШ 14, который формирует тактовые сдвигающие импульсы. Эти импульсы через элемент ИЛИ 10 поступают на вход регистра 4 сдвига и счетчика 8. С входа 17 сиг- 0 нал Лог.1 поступает на информационный вход pepiCTpa 4 сдвига и узел 13 контроля на нечетность, происходит заполпение регистра 4, и определяется нечетность принятого кода. 5 Отсутствие сигнала на первом входе регистра 4 и наличие сдвигающего тактового импульса воспринимается как Лог.о. Счетчик 8, отсчитав 33 импульса, обнуляется. Схема 7 срав- 50 нения сравнивает коды счетчиков 3 и 8 и при равенстве на ее выходе 1, которая поступает на вход блока 9, счетчик 8 обнуляется несколько позже

Счетчика 3 за счет задержки распро- 55 странения сигналов в линии связи между преобразователем и источником

информации.

Эта задержка компенсируется за сче увеличения длительности импульса, поступающего с первого выхода счетчика 3 в блок 9 управления. Эту функцию выполняет элемент 36 задержки.

С некоторой задержкой времени, определяемой элементом 35 задержки в зависимости от кода, пришедшего на первые входы элементов И 27 - 30, на их вьгходах появляются сигналы. ПроИсх одит запись информации в вы- . ходной регистр 12, выдается сигнал Верно, а также в элемент ИЛИ 11, означающий конец цикла и начало нового. Источник информации, получив сигнал Верно подготавливает к передаче новое информационное слово. Ци1сл повторяется. Таким образом принимается весь массив информации.

Если в линии связи появляются помехи, поступают на входы 17 или 16, и могут быть восприняты преобразователем как полезные сигналы, при этом счетчик 8 отсчитывает большое количество импульсов, схема 7сравнения вьщает О в блок управления, триггер 33 устанавливается в О. Схема проверки па нечетность может выдать сигнал о, если код четный, триг- гер 33 также устанавливается в О. Аналогичное произойдет,ecnvi в счетчик 8 поступит меньшее количество импульсов. Блок 9 управления выдает сигнал Неверно и сигнал об окончании цикла. Записи ниформации при. этом не произойдет и поскольку на втором входе элемента И 25 запрещающий сигнал О, то вычитание 1 из счетчика 24 не произойдет. При получении сигнала Неверно источник информации повторяет передачу неправильно принятого информационного слова. Информация в выходном регистре 12 может храниться в течение времени заполнения регистра 4 сдвига. Емкость регистров 4 и 12 4-х байтная, выбрана из условий быстродействия ЭВМ и времени приема всего массива информации. Из этих же условий выбирается частота генератора 1.

В автономном режиме информация с второго входа регистра 13 команд поступает на вход регистра 4 сдвига. Заполнение тестовой информацией регистров 4 и 12 происходит так же, как и от исто:.ника информации. Путем программного сравнения тестовой и полученной на выходе регистра 12 информации можно судить об исправности преобразователя.

Применение в данном устройстве спасоба приема информации по типу запрос - ответ позволяет не синхронизировать частоту тактового feHeратора и частоту поступления входных битов- информации. Элемент ИСКГПО1АЮЩЕЕ ИЛИ подавляет помехи при одновременном их появлении на входах 16 и 17. Счетчики 3 и 8, схема 7 сравнения, узел 13 контроля на нечетность (как основные узлы) позволяют контролировать правильность принятой информации. Наличие сигналов Верно и Неверно исключает утерю информации.

М la fegvtytya laiMiHd 15

| Преобразователь последовательногоКОдА B пАРАллЕльНый | 1979 |

|

SU822175A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 760070, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-23—Публикация

1984-05-08—Подача