Изобретение относится к приемным устройствам импульсной информации и предназначено для использования в РЛС для фильтрации сигналов движущихся целей на фоне пассивной помехи.

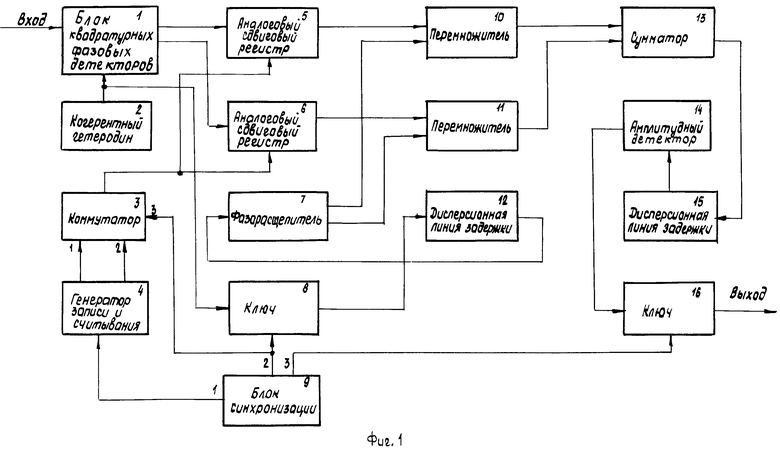

В настоящее время одним из перспективных направлений разработки адаптивных устройств селекции движущихся целей (СДЦ) являются устройства, основанные на использовании Фурье процессоров на поверхностных акустических волнах (ПАВ) и приборов с зарядовой связью (ПЗС). В [Electronics Letters, October 1975, vol. 11, p. 525-526] описан принцип работы устройства СДЦ на Фурье процессорах на ПАВ и ПЗС, приведена упрощенная структурная схема устройства. Полная схема такого устройства изображена на фиг. 1 материалов данной заявки. Устройство содержит блок квадратурных фазовых детекторов 1, когерентный гетеродин 2, коммутатор 3, генератор записи и считывания 4, аналоговые сдвиговые регистры 5, 6, квадратурный фазорасщепитель 7, ключи 8, 16, блок синхронизации 9, перемножители 10, 11, дисперсионные линии задержки 12, 15, сумматор 13, амплитудный детектор 14. Входом устройства является первой вход блока 1, а выходом - выход ключа 16.

На вход устройства поступает сигнал промежуточной частоты. С выхода блока квадратурных фазовых детекторов 1 на информационные входы аналоговых сдвиговых регистров 6, 5 подаются видеосигналы (синфазная и квадратурная составляющие), которые записываются в реальном масштабе времени в регистрах 6, 5. В режиме записи на втором выходе блока синхронизации 9 формируется положительный импульс, который открывает коммутатор 3 по его первому входу. При этом сигнал записи с первого выхода генератора 4 поступает на входы записи и считывания регистров 5, 6. Синхронизация генератора 4 производится импульсами блока синхронизации. Частота сигналов записи равна частоте повторения зондирующих импульсов РЛС. При заданных емкости сдвиговых регистров и частоте следования импульсов РЛС число импульсов, записанных в регистрах 6, 7, определяется длительностью импульса записи. В момент времени, соответствующему заднему фронту импульса записи, на втором выходе блока синхронизации 9 формируется отрицательный импульс (импульс считывания), который открывает коммутатор 3 по второму входу. При этом на входы записи и считывания регистров 5, 6 со второго выхода генератора 4 подается сигнал считывания. Частота сигнала считывания выбирается такой, чтобы длительность считанного сигнала равнялась длительности сигнала с линейной частотной модуляцией (ЛЧМ), формируемого дисперсионной линией задержки 12 (ДЛЗ). Например, при количестве импульсов пачки N=20, длительности ЛЧМ сигнала Т=5 мкс, частота сигнала считывания составляет Fсч=4 МГц. В известном устройстве частота сигнала считывания фиксирована. Импульс считывания открывает также ключ 8. Колебания когерентного гетеродина 2 проходят на вход ДЛЗ-12 и вызывают формирование на ее выходе ЛЧМ сигнала. С выходов квадратурного фазорасщепителя 7 ортогональные ЛЧМ сигналы подаются на вторые входы перемножителей 10, 11, а считанные с регистров 5, 6 ортогональные сигналы - на их первые входы.

На выходе сумматора 13 выделяется сигнал одной боковой полосы частот спектра выходного сигнала перемножителей 10, 11. ДЛЗ-15 осуществляет разложение во времени спектра выходных сигналов регистров 5, 6. Амплитудный детектор 14 выделяет огибающую выходного сигнала ДЛЗ-15. Различные допплеровские частоты помехи и сигнала на входе устройства преобразуются на выходе ДЛЗ-15 в различные временные положения импульсов помехи и сигнала. Различные временные положения сигнала и помехи позволяют стробированием выделять полезные сигналы и подавлять помеху. В устройстве операция стробирования осуществляется ключом 16, на второй вход (управляющий вход) которого подается импульс строба с третьего выхода блока синхронизации 9. На выходе ключа 16 имеется отфильтрованный полезный сигнал.

Достоинством известного устройства СДЦ являются широкие возможности по регулировке временного положения и длительности строба. Например, для фильтровых устройств СДЦ это эквивалентно регулировке частоты среза и полосы пропускания фильтра. Таким образом, известное устройство СДЦ является адаптивным (адаптация по длительности строба и его временному положению).

Практическое использование в РЛС устройств СДЦ на Фурье-процессорах на ПАВ и ПЗС позволяет получать оптимальные коэффициенты подавления для широкого диапазона доплеровских частот и различных спектров помехи.

Современные и перспективные РЛС являются адаптивными к изменению помеховой обстановки. В РЛС при решении задачи обнаружения целей предъявляются требования минимизации энергетических затрат и времени решения задачи, что особенно важно в РЛС с фазированными антенными решетками. Применительно к устройствам СДЦ перечисленные требования означают, что в зависимости от уровня помехи длительность обрабатываемой пачки должна быть переменной, т.е. число импульсов в пачке обрабатываемой устройством СДЦ, определяется уровнем помехи. Устройство СДЦ должно быть адаптивно по длительности пачки. Большие диапазоны изменения уровня помехи приводят к необходимости вариации в широких пределах (4-5 раз) длительности пачки.

Известное устройство имеет узкий (порядка 20-30%) диапазон вариации длительности пачки, что является его недостатком. Данный недостаток обусловлен тем, что изменение длительности пачки в известном устройстве приводит к различным моментам появления на входах перемножителей считанных с регистров обрабатываемых сигналов и ЛЧМ сигнала, а также происходит их рассогласование по длительности. Рассогласование параметров сигналов вызывает ухудшение разрешающей способности Фурье-процессора, увеличивает потери амплитуды полезного сигнала. Это приводит к уменьшению коэффициента подавления помехи, т.е. эффективность системы СДЦ снижается.

Предлагаемое техническое решение направлено на расширение возможностей адаптации устройства СДЦ по длительности пачки.

В качестве прототипа заявляемого объекта выбираем устройство, схема которого приведена на фиг. 1 материалов данной заявки.

Целью настоящего изобретения является расширение возможностей адаптации устройства СДЦ.

Поставленная цель достигается тем, что в известное устройство, содержащее блок квадратурных фазовых детекторов, когерентный гетеродин, два ключа, первый вход блока квадратурных фазовых детекторов является входом устройства, а второй - подключен к выходу когерентного гетеродина и к первому входу второго ключа, два аналоговых сдвиговых регистра, перемножители, коммутатор, генератор записи и считывания, причем информационные входы аналоговых сдвиговых регистров подключены к выходам блока квадратурных фазовых детекторов, входы записи и считывания - к выходу коммутатора, а выходы - к первым входам перемножителей, блок синхронизации, сумматор, квадратурный фазорасщепитель, две дисперсионные линии задержки, амплитудный детектор, первый выход блока синхронизации подключен ко входу генератора записи и считывания, а второй и третий - соответственно к управляющему входу коммутатора и ко второму входу первого ключа, первый выход генератора записи и считывания соединен с первым входом коммутатора, выход второго ключа через вторую дисперсионную линию задержки подключен ко входу квадратурного фазорасщепителя, выходы которого соединены со вторыми входами перемножителей, входы сумматора соединены с выходами перемножителей, а выход - через последовательно включенные первую дисперсионную линию задержки и амплитудный детектор - к первому входу первого ключа, выход которого является выходом устройства, дополнительно введены управляемый делитель частоты, вход которого соединен с выходом генератора записи и считывания, а выход - со вторым входом коммутатора, счетчик импульсов, выход коммутатора подключен к счетному входу счетчика, блок сравнения, три регистра, второй коммутатор, блоки деления, вычитания, умножения, блок управляемой задержки, выходы первого и второго регистров подключены к входам второго коммутатора и блока вычитания, входы блока сравнения подключены к выходам второго коммутатора и счетчика импульсов, а выход - к входу блока синхронизации и к входу сброса счетчика импульсов, входы блока деления соединены с выходами второго и третьего регистров, а выход - с управляющим входом управляемого делителя частоты и со вторым входом блока умножения, выход блока вычитания подключен к первому входу блока умножения, выход которого соединен с управляющим входом блока управляемой задержки. Второй выход блока синхронизации через блок управляемой задержки подключен ко второму входу второго ключа, а управляющий вход второго коммутатора соединен со вторым выходом блока синхронизации.

Счетчик импульсов, блок сравнения, управляемый делитель частоты, регистры, коммутаторы, блок деления позволяет сделать одинаковыми длительности считанных с регистров сигналов и ЛЧМ сигналов на входах перемножителей, а блок вычитания, умножения и блок управляемой задержки - одинаковыми моменты появления этих сигналов.

Введение в известное устройство указанных элементов и связей позволило получить новый эффект - расширение возможностей адаптации устройства СДЦ по длительности пачки.

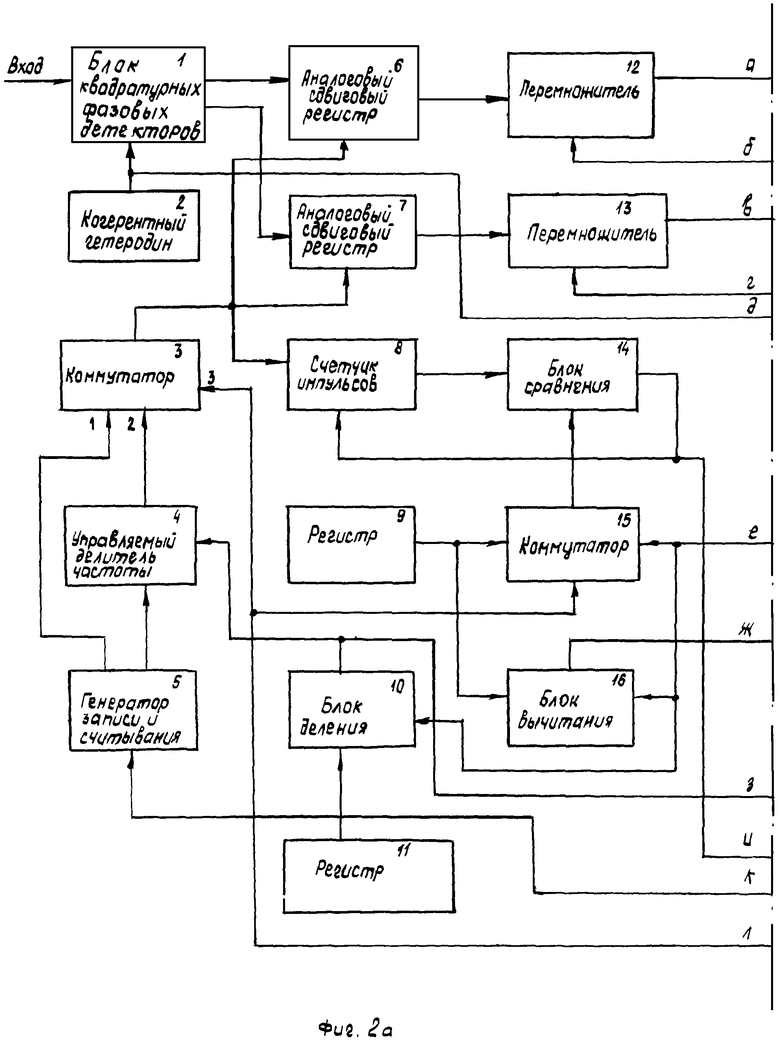

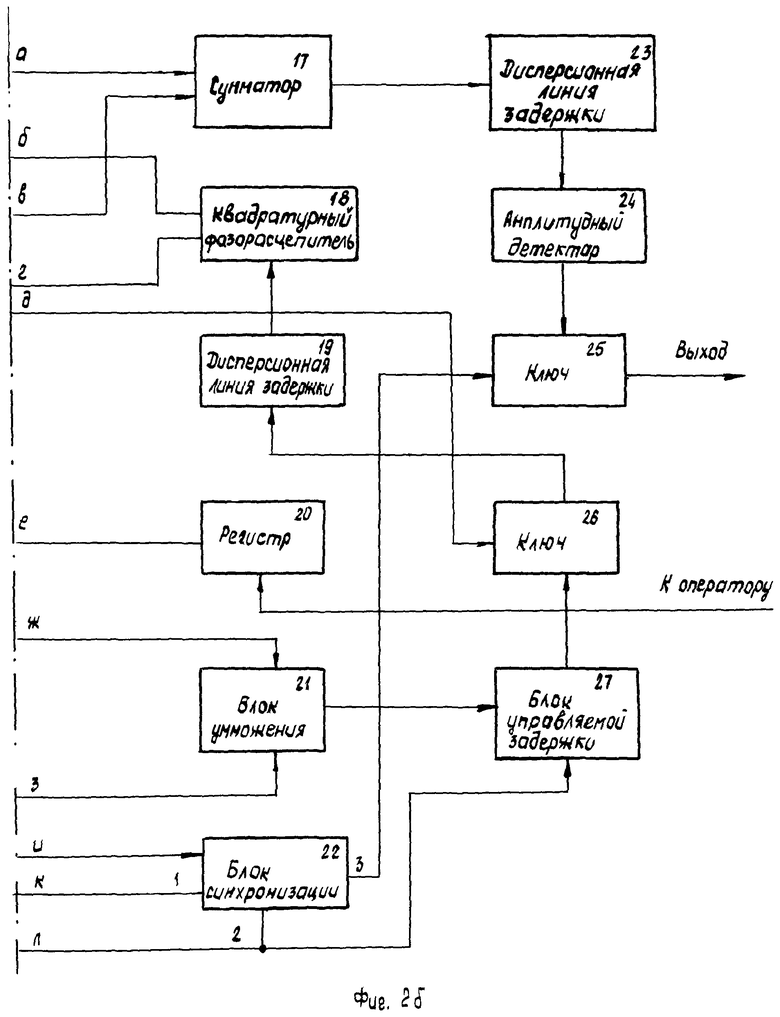

На фиг. 2 изображена функциональная схема предлагаемого устройства. Устройство содержит блок квадратурных фазовых детекторов 1, когерентный гетеродин 2, коммутаторы 3, 15, управляемый делитель частоты 4, генератор записи и считывания 5, аналоговые сдвиговые регистры 6, 7, счетчик импульсов 8, регистры 9, 11, 20, блок деления 10, перемножители 12, 13, блок сравнения 14, блок вычитания 16, сумматор 17, квадратурный расщепитель 18, дисперсионные линии задержки 19, 23, блок умножения 21, блок синхронизации 22, амплитудный детектор 24, ключи 25, 26, блок управляемой задержки 27.

Входом устройства является первый вход блока 1, а выходом - выход ключа 25. Второй вход блока 1 соединен с выходом когерентного гетеродина 2 и с первым входом ключа 26. Информационные входы регистров 6, 7 подключены к выходам блока 1, входы записи и считывания - к выходу коммутатора 3, а выходы - к первым входам перемножителей 12, 13. Первый выход генератора записи и считывания 5 соединен с первым входом коммутатора 3, а второй - через управляемый делитель частоты 4 подключен ко второму входу коммутатора 3. Выход ключа 26 через дисперсионную линию задержки 19 соединен со входом квадратурного фазорасщепителя 18, выходы которого подключены ко вторым входам перемножителей 12, 13. Входы сумматора 17 подключены к выходам перемножителей 12, 13, а выход - через последовательно включенную дисперсионную линию задержки 23 и амплитудный детектор 24 соединен с первым входом ключа 25. Первый выход блока синхронизации подключен к входу генератора записи и считывания 5, второй - к управляющим входам коммутаторов 3, 15 и к входу блока управляемой задержки 27, третий - ко второму входу ключа 25. Выходы регистров 9, 20 подключены к входам коммутатора 15 и блока вычитания 16. Входы блока сравнения 14 соединены с выходами счетчика 8 и коммутатора 15, а выход - с входом сброса счетчика 8 и входом блока синхронизации 22. Выход коммутатора 3 подключен к счетному входу счетчика 8.

Входы блока деления 10 соединены с выходами регистров 11, 20, а выход - с управляющим входом управляемого делителя частоты 4 и вторым входом блока умножения 21. Выход блока вычитания 16 подключен к первому входу блока умножения 21, выход которого соединен с управляющим входом блока управляемой задержки 27. Второй вход ключа 26 подключен к выходу блока управляемой задержки 27.

Рассмотрим работу предлагаемого устройства. Описание работы проведем в предположении, что на вход устройства поступают промчастотные сигналы только с одного элемента дальности.

В устройстве в зависимости от уровня помехи на входе РЛС оператором либо ЦВМ выбирается число импульсов в пачке, которое записывается в регистре 20 (выбирается рабочая длительность пачки). В регистре 9 записано максимальное число импульсов пачки (максимальная длительность пачки). На первом выходе блока синхронизации 22 формируется последовательность видеоимпульсов с частотой следования зондирующих сигналов РЛС, которые синхронизируют работу генератора записи и считывания 5. В режиме записи на втором выходе блока синхронизации 22 формируется положительный импульс, который открывает коммутаторы 3, 15 по первым входам. Сигнал записи, частота которого равна частоте повторения импульсов РЛС, поступает на входы записи и считывания регистров 6, 7 и на счетный вход счетчика 8. В регистрах 6, 7 производится запись сигналов, поступающих с выходов блока 1, а счетчик 8 фиксирует число записанных в регистрах 6, 7 импульсов. С выхода счетчика 8 код записанного числа подается на первый вход блока сравнения 14. На второй вход блока сравнения 14 через коммутатор 15 поступает код рабочего числа импульсов. При равенстве чисел, записанных в счетчике 8 и в регистре 20, на выходе блока сравнения 14 формируется видеоимпульс, который подается на вход блока синхронизации 22. Импульс блока сравнения 14 формирует задний фронт импульса записи и сбрасывает записанную в счетчике 8 информацию. При этом процесс записи заканчивается. Таким образом, число записанных в регистрах 6, 7 импульсов равно рабочему числу импульсов устройства СДЦ.

В предлагаемом устройстве рабочее число импульсов пачки определяет частоту сигнала считывания и величину задержки ЛЧМ сигнала, формируемого ДЛЗ-19. Такая обработка позволяет сделать одинаковыми моменты появления на входах перемножителей 12, 13 считанных с регистров 6, 7 сигналов и ЛЧМ сигналов, а также сделать и одинаковые длительности этих сигналов. Этим достигается устранение рассогласования параметров сигналов на входе перемножителей 12, 13, что приводит к расширению возможностей адаптации устройства по длительности пачки.

В регистре 11 записывается код длительности ЛЧМ сигнала, формируемого ДЛЗ-19. Код длительности ЛЧМ сигнала подается на первый вход блока деления 10, на второй вход которого с выхода регистра 20 подается код рабочего числа импульсов пачки. На выходе блока деления 10 формируется код периода сигнала считывания. Код периода сигнала считывания подается на управляющий вход управляемого делителя частоты 4 и второй вход блока умножения 21. На выходе управляемого делителя частоты 4 устанавливается частота сигнала считывания в соответствии с поступающим кодом. На выходе блока вычитания 16 имеется код разности максимального числа импульсов пачки и рабочего числа импульсов. Код разности подается на первый вход блока умножения 21, на выходе которого формируется код задержки τ3 ЛЧМ сигнала. Код задержки поступает на вход блока управляемой задержки 27. В блоке управляемой задержки 27 производится задержка импульса считывания на величину τз.

В режиме считывания на втором выходе блока синхронизации 22 формируется импульс отрицательной полярности, который открывает коммутаторы 3, 15 по вторым входам. Сигнал считывания с выхода управляемого делителя частоты 4 поступает на входы записи и считывания регистров 6, 7 и вход счетчика 8. Счетчик 8 производит счет периодов сигнала считывания. Код числа периодов сигнала подается на первый вход блока сравнения 14, на второй вход которого с выхода регистра 9 подается код максимального числа импульсов пачки. При равенстве этих кодов на выходе блока сравнения 14 формируется импульс. Этот импульс поступает на вход блока синхронизации 22 и формирует задний фронт импульса считывания. Процесс считывания заканчивается. Импульс блока 14 сбрасывает информацию, записанную в счетчике 8. Задержанный в блоке управляемой задержки 27 импульс считывания открывает ключ 26. Сигнал когерентного гетеродина 2 проходит на вход ДЛЗ-19, на выходе которой формируется ЛЧМ сигнал. ДЛЗ-23 осуществляет разложение во времени спектра выходных сигналов регистров 6, 7. На выходе блока синхронизации 22 формируется импульс строба, который открывает ключ 25. На выходе ключа 25 выделяется полезный сигнал и подавляется помеха.

Все узлы предлагаемого устройства выполнены по известным типовым схемам. Аналоговые сдвиговые регистры 6, 5 выполнены на микросхемах 528 БР1, цифровые элементы устройства реализованы на базе серии 133.

Проведенные расчеты показали, что в предлагаемом устройстве диапазон изменения длительности пачки по сравнению с известным устройством расширен в 3-4 раза.

Таким образом, предлагаемое устройство позволяет получить новый эффект - расширение возможностей адаптации устройства СДЦ по длительности пачки. Это дает возможность в РЛС уменьшить время решения задачи обнаружения целей, сократить энергетические затраты.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 1988 |

|

SU1841042A1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| УЛЬТРАЗВУКОВОЙ МИКРОСКОП | 2005 |

|

RU2270997C1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| Устройство для распознавания бинарных фазоманипулированных сигналов | 1986 |

|

SU1841159A1 |

| Устройство для распознавания бинарных фазоманипулированных сигналов | 1987 |

|

SU1841004A2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| УСТРОЙСТВО ДЛЯ РАЗЛИЧЕНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1987 |

|

SU1841020A2 |

| УСТРОЙСТВО ДЛЯ РАЗЛИЧЕНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1984 |

|

SU1841016A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1991 |

|

SU1841072A1 |

Изобретение относится к приемным устройствам импульсной техники и предназначено для использования в радиолокационных станциях. Достигаемый технический результат - улучшение адаптации. Указанный результат достигается за счет того, что устройство содержит блок квадратурных фазовых детекторов, когерентный гетеродин, два ключа, два аналоговых сдвиговых регистра, два перемножителя, коммутатор, генератор записи и считывания, блок синхронизации, сумматор, квадратурный фазовращатель, две дисперсионные линии задержки, амплитудный детектор, управляемый делитель частоты, счетчик импульсов, блок сравнения, три регистра, второй коммутатор, блок управляемой задержки. Все перечисленные средства соответствующим образом соединены между собой. 3 ил.

Устройство селекции движущихся целей, содержащее блок квадратурных фазовых детекторов, когерентный гетеродин, два ключа, два аналоговых сдвиговых регистра, два перемножителя, коммутатор, генератор записи и считывания, блок синхронизации, сумматор, квадратурный фазорасщепитель, две дисперсионные линии задержки, амплитудный детектор, причем первый вход блока квадратурных фазовых детекторов является сигнальным входом устройства, а его второй вход подключен к выходу когерентного гетеродина и к первому входу второго ключа, информационные входы аналоговых сдвиговых регистров соединены с соответствующими выходами блока квадратурных фазовых детекторов, входы записи и считывания - с выходом коммутатора, а выхода - с первыми выходами перемножителей, первый выход блока синхронизации подключен к входу генератора записи и считывания, а второй и третий - соответственно к управляющему входу коммутатора и ко второму входу первого ключа, первый выход генератора записи и считывания соединен с первым входом коммутатора, выход второго ключа через вторую дисперсионную линию задержки подключен ко входу квадратурного фазорасщепителя, выходы которого соединены со вторыми входами перемножителей, входы сумматора соединены с выходами перемножителей, а выход - через последовательно включенные первую дисперсионную линию задержки и амплитудный детектор к первому входу первого ключа, отличающееся тем, что, с целью улучшения адаптации, в него введены управляемый делитель частоты, счетчик импульсов, блок сравнения, три регистра, второй коммутатор, блоки деления, вычитания, умножения, блок управляемой задержки, причем вход управляемого делителя частоты соединен с генератором считывания и записи, а выход - со вторым входом коммутатора, выход которого подключен к счетному входу счетчика, выходы первого и второго регистров соединены с входами второго коммутатора и блока вычитания, входы блока сравнения подключены к выходам второго коммутатора и счетчика импульсов, а выход - к входам блока синхронизации и к входу сброса счетчика импульсов, входы блока деления соединены с выходами второго и третьего регистров, а выход - с управляющим входом управляемого делителя частоты и со вторым входом блока умножения, выход блока вычитания подключен к первому входу блока умножения, выход которого соединен с управляющим входом блока управляемой задержки, второй выход блока синхронизации через блок управляемой задержки подключен к второму входу второго ключа, а управляющий вход второго коммутатора соединен со вторым выходом блока синхронизации.

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

| Теория, проектирование и применение Фурье-процессоров на поверхностных акустических волнах | |||

| Electronics Letters, 30 October, 1975, 11, №22, стр | |||

| Телескоп | 1920 |

|

SU525A1 |

Авторы

Даты

2015-01-10—Публикация

1981-10-08—Подача