СП

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ магнитной записи цифровой информации | 1990 |

|

SU1737504A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Преобразователь сдвига фазы в код скорости и ускорения | 1986 |

|

SU1358096A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для определения места расположения центра технического обслуживания сети | 1991 |

|

SU1807500A1 |

| Генератор случайных чисел | 1989 |

|

SU1781681A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Устройство для определения весового расхода и контроля качества сыпучего материала | 1982 |

|

SU1089425A1 |

| Устройство для декодирования с исправлением ошибок | 1990 |

|

SU1797165A1 |

| Устройство для определения периодического электрического сигнала | 1989 |

|

SU1781653A1 |

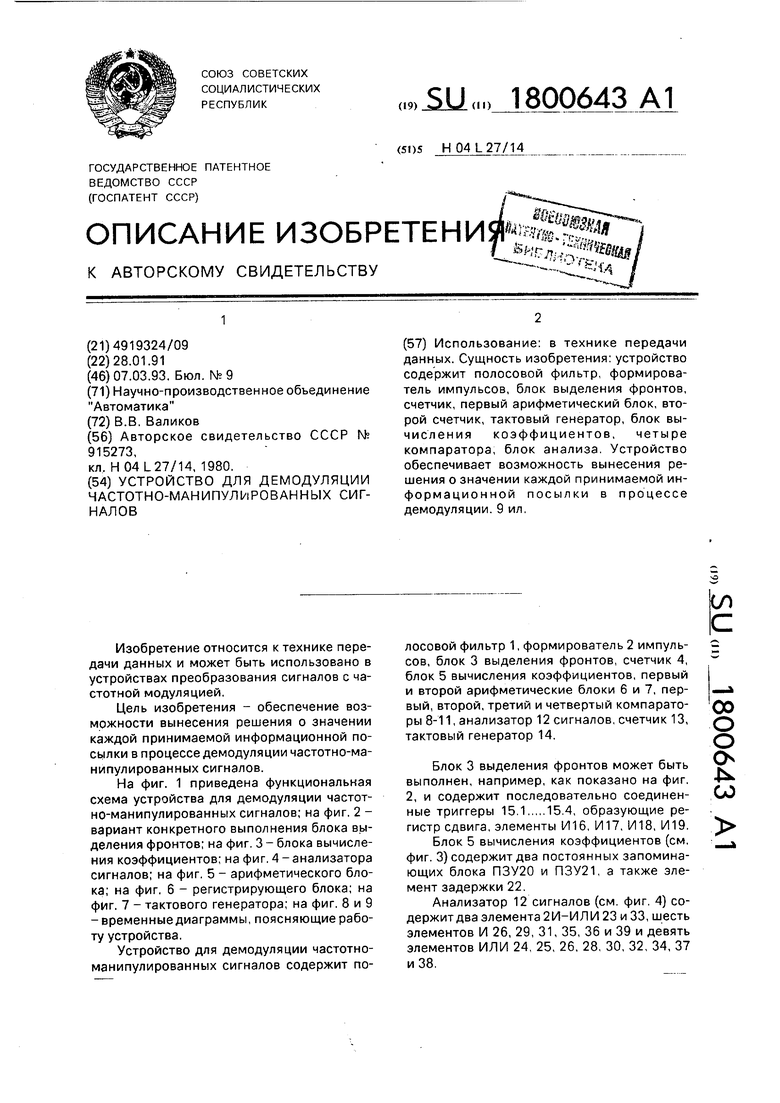

Использование: в технике передачи данных. Сущность изобретения: устройство содержит полосовой фильтр, формирователь импульсов, блок выделения фронтов, счетчик, первый арифметический блок, второй счетчик, тактовый генератор, блок вычисления коэффициентов, четыре компаратора, блок анализа. Устройство обеспечивает возможность вынесения решения о значении каждой принимаемой информационной посылки в процессе демодуляции. 9 ил.

Изобретение относится к технике передачи данных и может быть использовано в устройствах преобразования сигналов с частотной модуляцией.

Цель изобретения - обеспечение возможности вынесения решения о значении каждой принимаемой информационной посылки в процессе демодуляции частотно-ма- нипулированных сигналов.

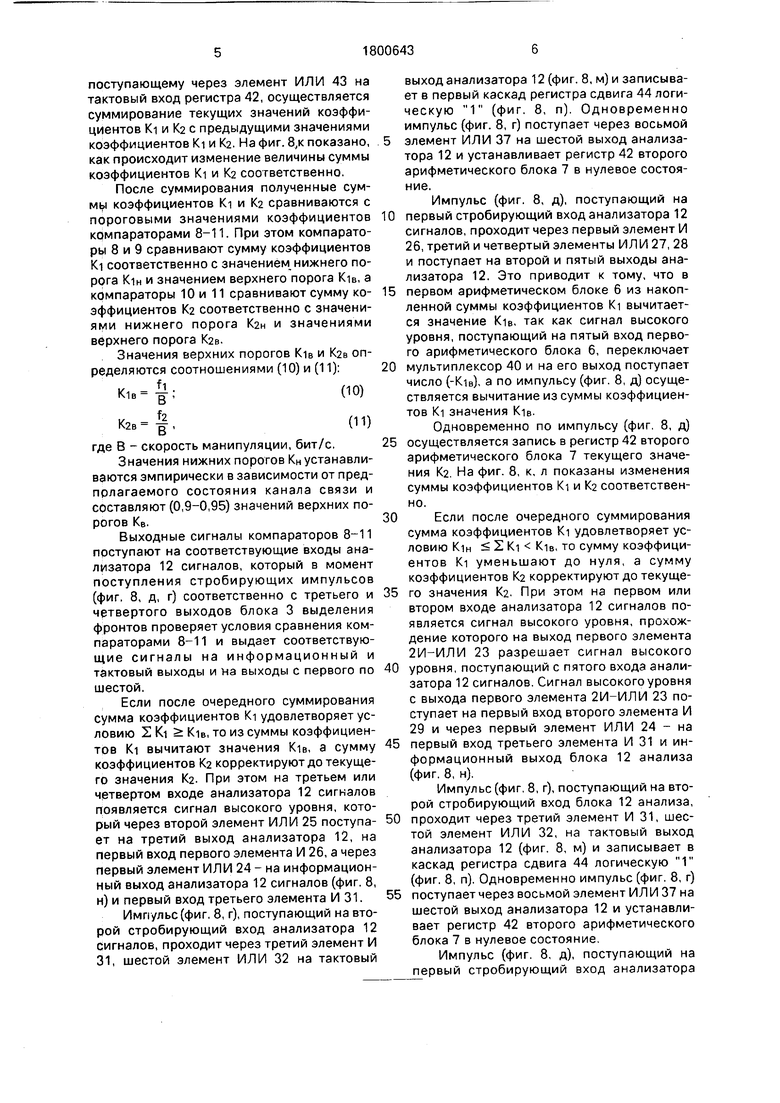

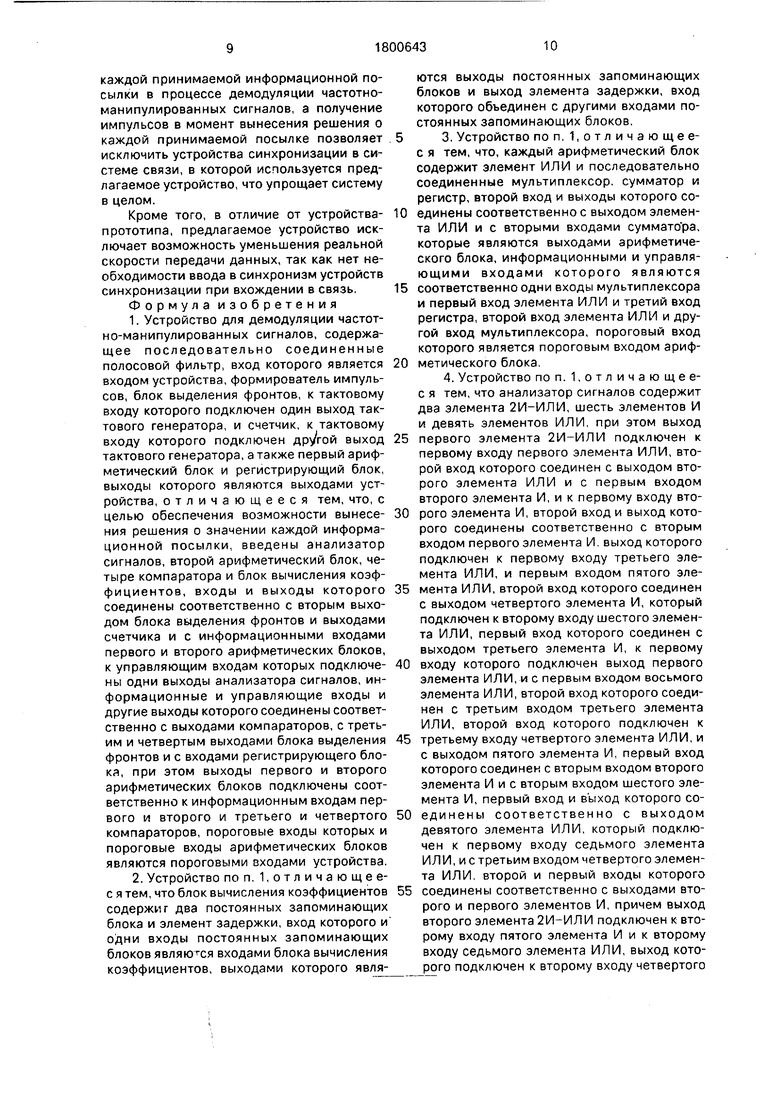

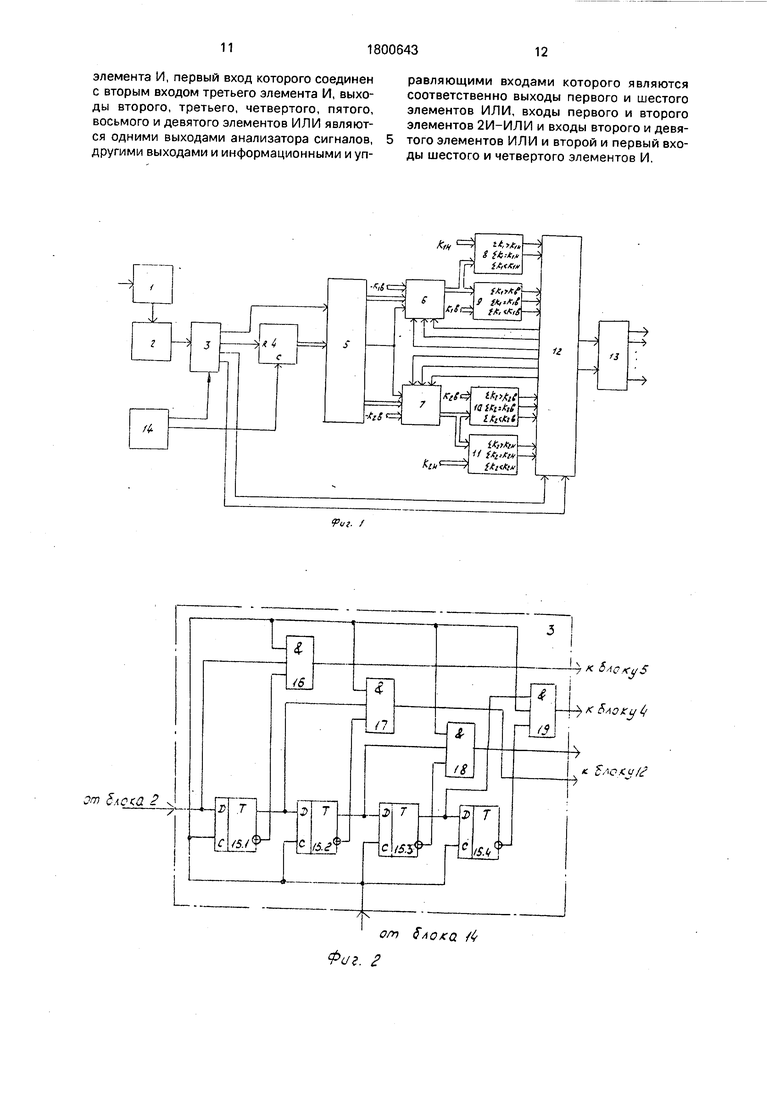

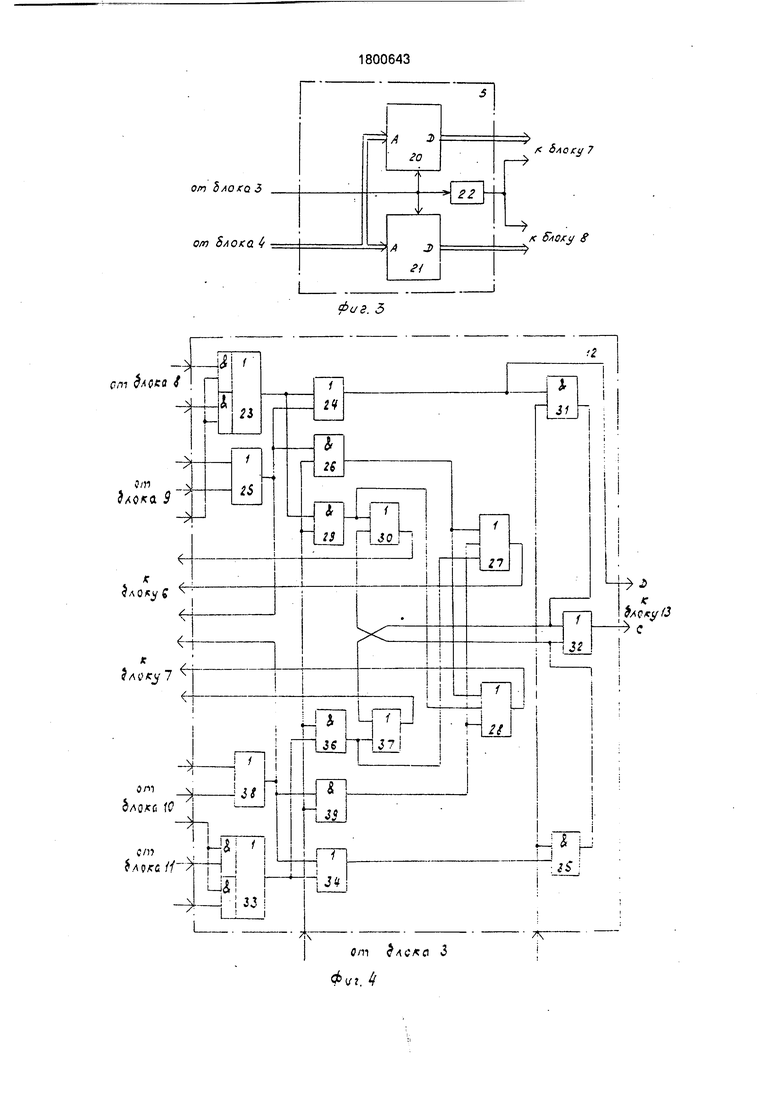

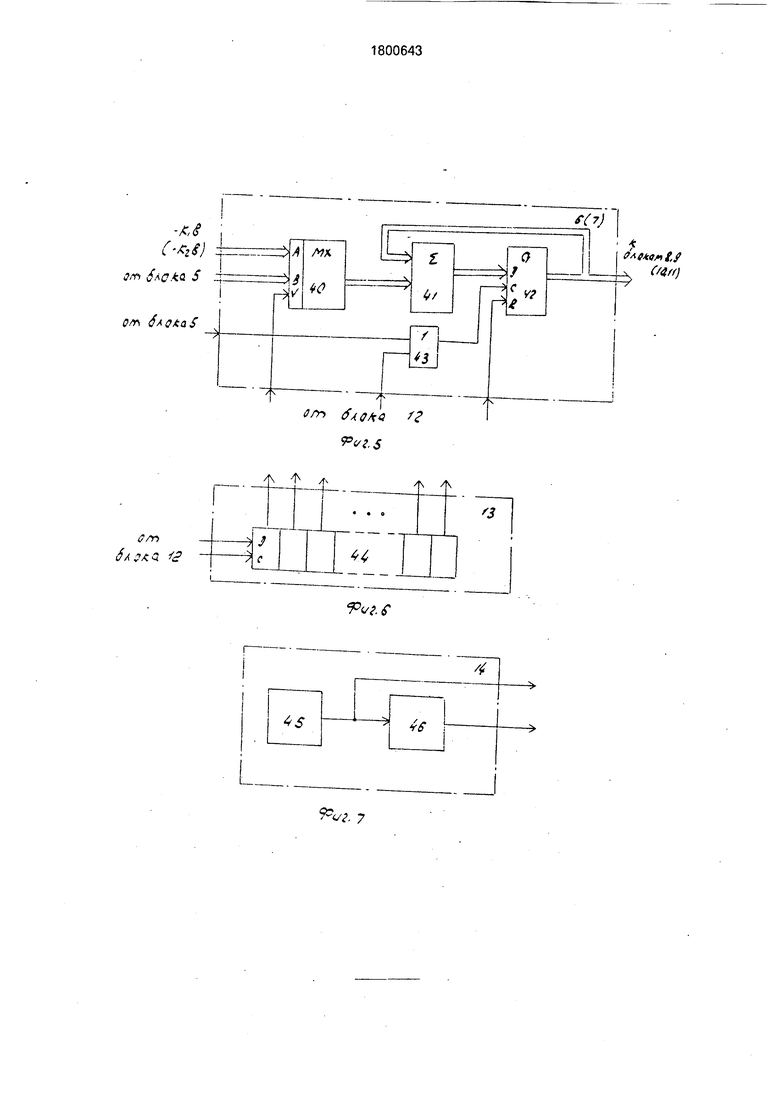

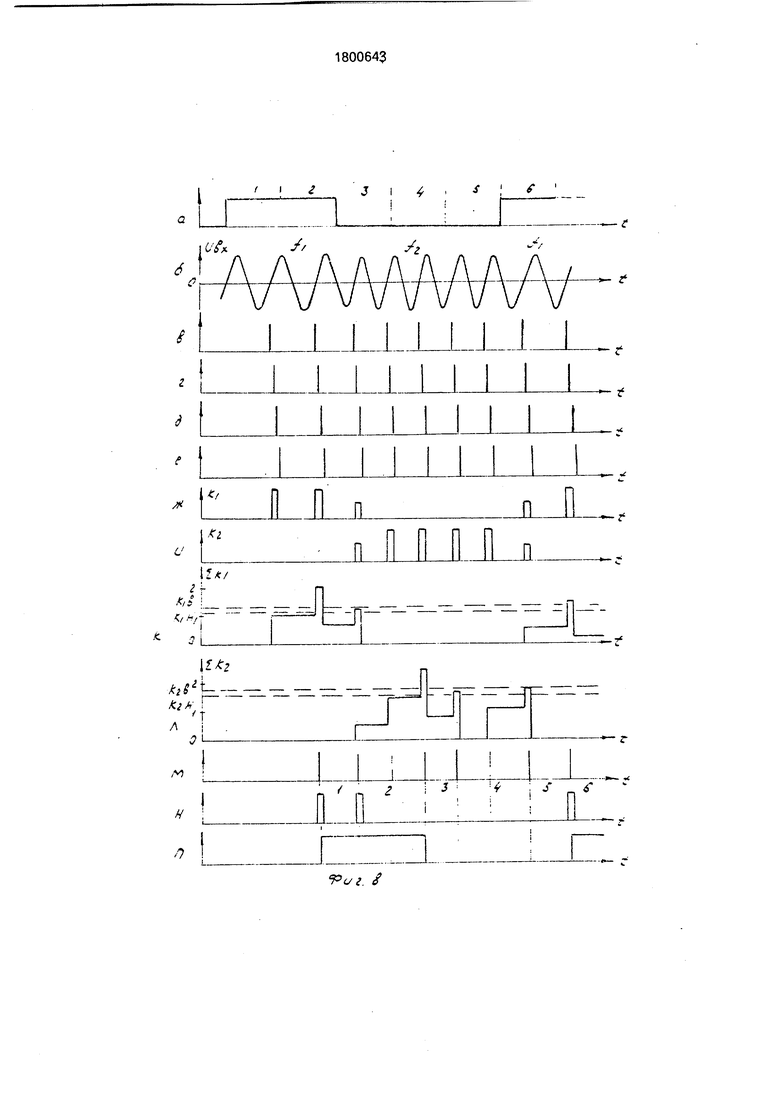

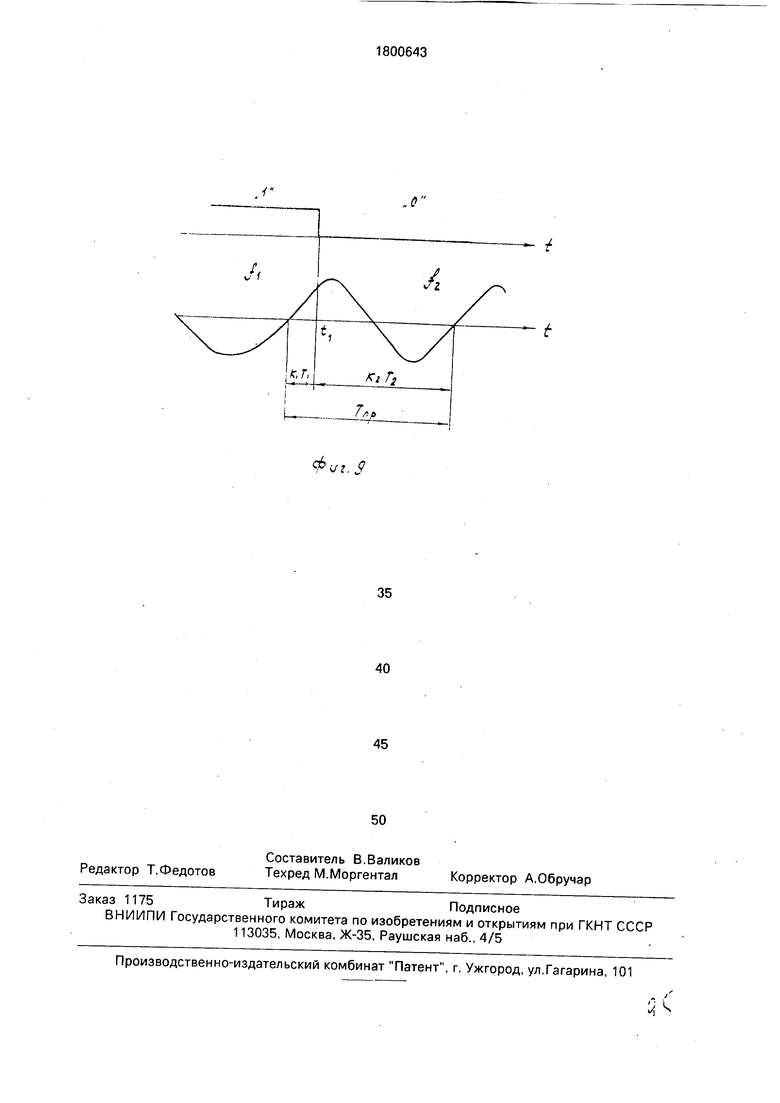

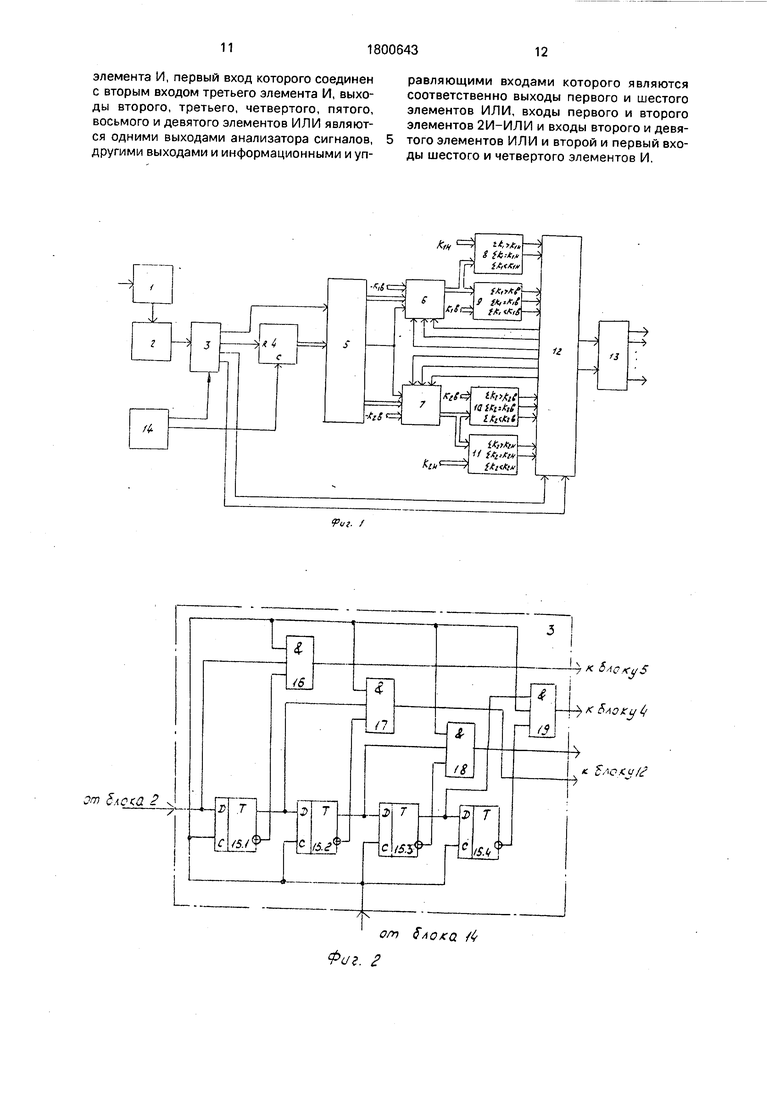

На фиг. 1 приведена функциональная схема устройства для демодуляции частот- но-манипулированных сигналов; на фиг. 2 - вариант конкретного выполнения блока выделения фронтов; на фиг. 3 - блока вычисления коэффициентов; на фиг. 4 - анализатора сигналов; на фиг. 5 - арифметического блока; на фиг, 6 - регистрирующего блока; на фиг. 7 - тактового генератора; на фиг. 8 и 9 -временные диаграммы, поясняющие работу устройства.

Устройство для демодуляции частотно- манипулированных сигналов содержит полосовой фильтр 1, формирователь 2 импульсов, блок 3 выделения фронтов, счетчик 4, блок 5 вычисления коэффициентов, первый и второй арифметические блоки 6 и 7, первый, второй, третий и четвертый компараторы 8-11, анализатор 12 сигналов, счетчик 13, тактовый генератор 14.

Блок 3 выделения фронтов может быть выполнен, например, как показано на фиг. 2, и содержит последовательно соединенные триггеры 15.1.....15.4, образующие регистр сдвига, элементы И16, И17, И18, И19.

Блок 5 вычисления коэффициентов (см, фиг. 3) содержит два постоянных запоминающих блока ПЗУ20 и ПЗУ21, а также элемент задержки 22.

Анализатор 12 сигналов (см. фиг. 4) содержит два элемента 2И-ИЛ И 23 и 33, шесть элементов И 26, 29, 31, 35, 36 и 39 и девять элементов ИЛИ 24, 25, 26, 28. 30, 32, 34, 37 и 38.

00

о о о

N СО

Каждый арифметический блок б (7) (см. фиг. 5) содержит мультиплексор 40, сумматор 41, регистр 42 и элемент ИЛИ 43.

Регистрирующий блок 13 (см. фиг. 6) представляет собой регистр сдвига 44,

Тактовый генератор 14 (см. фиг. 7) содержит последовательно соединенные опорный генератор 45 и делитель 46.

Предлагаемое устройство работает следующим образом.

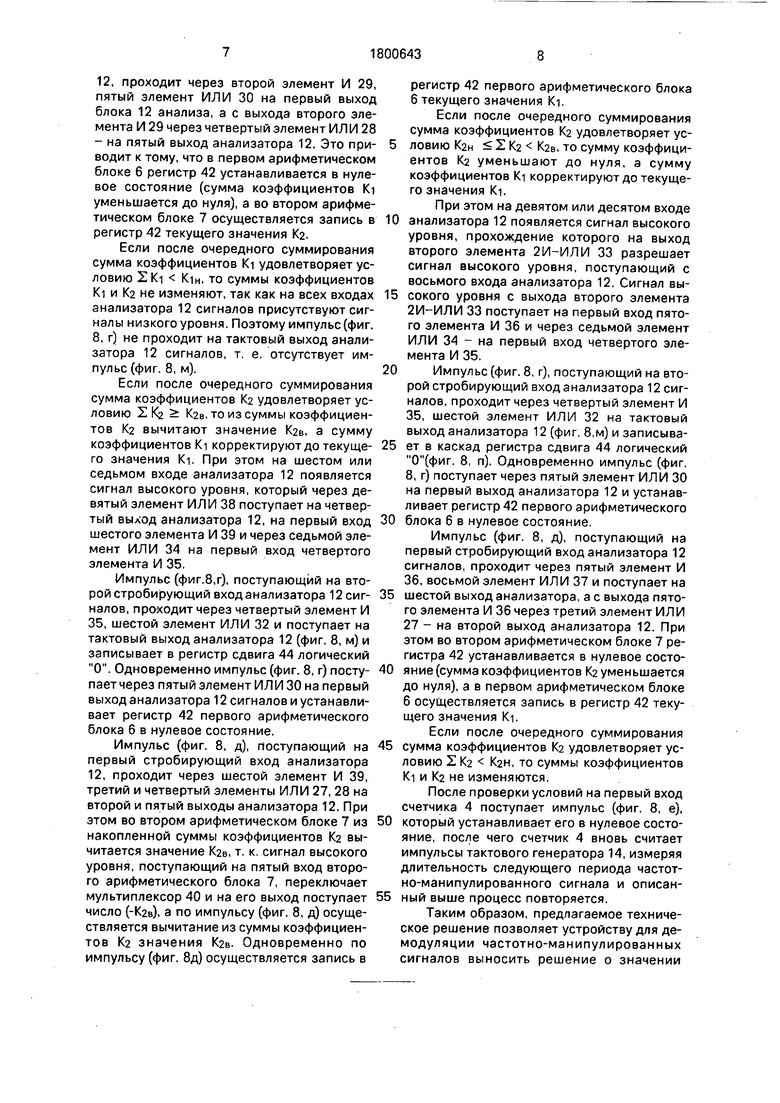

Частотно-манипулированный сигнал, поступающий из канала связи (фиг. 8, б), проходит через полосовой фильтр 1, преобразуется формирователем импульсов 2 в прямоугольные импульсы, которые поступа- ют на вход блока 3 выделения фронтов.

В момент перехода частотно-манипули- рованным сигналом через нулевой уровень блок 3 выделения фронтов формирует на своих выходах из импульсов опорной часто- ты fon, поступающих со второго выхода тактового генератора 14, серии импульсов, показанные на фиг. 8,в, г, д, е. По импульсам, формируемым на втором выходе блока 3 (фиг. 8,в), содержимое счетчика 4 поступает в блок 5 вычисления коэффициентов, а по импульсам, формируемым на первом выходе блока 3 (фиг. 8, е), счетчик 4 обнуляется и снова начинает считать импульсы тактовой частоты fT, поступающие с первого выхода тактового генератора 14. Таким образом осуществляется преобразование периодов частотно-манипулированного сигнала в количество импульсов тактовой частоты fr.

Для нормальной работы устройства не- обходимо выполнить соотношение fon 5: fT, что позволяет формировать импульсы (фиг. 8, в, г, д, е) в блоке 3 выделения фронтов за один период частоты fT.

В общем случае каждый период прини- маемого частотно-манипулированного сигнала ТПр (см. фиг. 9) отождествляют с периодом, в котором происходит смена характеристических частот fi и fa. Тогда, предполагая, что в момент времени ti смены характеристических частот разрыв фазы отсутствует (данное условие обычно выполняется), длительность периода принимаемого сигнала определяется следующим соотношением:

ТПр Кг Ti + К2 Т2,(1) где Ki, К2 - коэффициенты, учитывающие, какая часть периодов Ti и Та характеристических частот fi и fa соответственно прихо- дится на принимаемый период. При этом для коэффициентов Ki и К2 выполняется следующее соотношение:

Ki + Ka 1

5

10

15

20 25 30

35

40 4550

55Аналогичные соотношения (1) и (2) справедливы для полупериодов частотно-манипулированного сигнала.

Предварительно решив совместно уравнения (1) и (2), находят для каждого значения принимаемого периода ТПр значения коэффициентов Кч и Ка по формулам (3) и (4): Тпр - Та

Ki

(3)

3)

4)

Ti - Та .

При условии, что TI Та, коэффициенты Ki и Ка принимают следующие значения:

1) Ki 1, Ка 0 при Тпр Ti;

2) Ki 0, Ка 1 при Тпр Та; 0 Ki 1 npnTa Tnp Ti; 0 Ка 1 при Та ТПр Тц

5) Ki Ка 0 при ТПр Ti или ТПр Та.

Выражая значения периодов Ti, Та, Тпр через количество импульсов N тактовой частоты fT, поступающих на счетчик 4, и подставляя их в формулу (3), получим окончательное выражение для нахождения коэффициентов Ki и Ка:

(5)

fr iDJ

Na fT ; Nnp .()

Ta

(6)

Тпр Ki

K2

fT Nnp - N2 N1 -Na N1 -Nnp

(8)

(9)

N1 -N2

где Ni, Na, Nnp - количество импульсов частоты fr тактового генератора, приходящихся соответственно на период Ti, Та, ТПр.

Вычисленные по формулам (8) и (9) значения коэффициентов Ki и Ка записаны соответственно в первое и второе ПЗУ 20, 21 блока 5 вычисления коэффициентов (фиг. 3).

При поступлении импульса со второго выхода блока 3 выделения фронтов (фиг. 8, в) на блок 5 вычисления коэффициентов значения коэффициентов Кч и Ка, записанные по адресу Nnp, соответствующему длительности принимаемого периода Тпр, в первом и втором ПЗУ 20, 21 считываются (фиг. 8, ж, 8, и) и поступают соответственно на первый и второй арифметические блоки 6 и 7, куда поступает также импульс (фиг. 8„в), задержанный элементом задержки 2. На фиг. 8 эта задержка не отражена из-за ее малой величины.

В первом и втором арифметических блоках 6 и 7 значения коэффициентов Ki и Ка через мультиплексор 40 поступают на вход накапливающего сумматора, образованного сумматором 41 и регистром 42. Одновременно по задержанному импульсу (фиг. 8,в),

поступающему через элемент ИЛИ 43 на тактовый вход регистра 42, осуществляется суммирование текущих значений коэффициентов Ki и К2 с предыдущими значениями коэффициентов Ki и К2. На фиг. 8,к показано, как происходит изменение величины суммы коэффициентов KI и «2 соответственно.

После суммирования полученные суммы коэффициентов Ki и К2 сравниваются с пороговыми значениями коэффициентов компараторами 8-11. При этом компараторы 8 и 9 сравнивают сумму коэффициентов Ki соответственно с значением нижнего порога KiH и значением верхнего порога Ku, a компараторы 10 и 11 сравнивают сумму коэффициентов К2 соответственно с значениями нижнего порога К2н и значениями верхнего порога К2в.

Значения верхних порогов К-|В и К2в определяются соотношениями (10) и (11):

(Ю)

.-§:

,

где В - скорость манипуляции, бит/с.

Значения нижних порогов Кн устанавливаются эмпирически в зависимости от предполагаемого состояния канала связи и составляют (0,9-0,95) значений верхних порогов Кв.

Выходные сигналы компараторов 8-11 поступают на соответствующие входы анализатора 12 сигналов, который в момент поступления стробирующих импульсов (фиг. 8, д, г) соответственно с третьего и четвертого выходов блока 3 выделения фронтов проверяет условия сравнения компараторами 8-11 и выдает соответствующие сигналы на информационный и тактовый выходы и на выходы с первого по шестой.

Если после очередного суммирования сумма коэффициентов Ki удовлетворяет условию 2 Ki K-IB, то из суммы коэффициентов Ki вычитают значения KiB, а сумму коэффициентов К2 корректируют до текущего значения К2. При этом на третьем или четвертом входе анализатора 12 сигналов появляется сигнал высокого уровня, который через второй элемент ИЛИ 25 поступает на третий выход анализатора 12, на первый вход первого элемента И 26, а через первый элемент ИЛИ 24 - на информационный выход анализатора 12 сигналов (фиг. 8, н) и первый вход третьего элемента И 31.

Импульс (фиг. 8, г), поступающий на второй стробирующий вход анализатора 12 Сигналов, проходит через третий элемент И 31, шестой элемент ИЛИ 32 на тактовый

выход анализатора 12 (фиг. 8, м) и записывает в первый каскад регистра сдвига 44 логическую 1 (фиг. 8, п). Одновременно импульс (фиг. 8, г) поступает через восьмой

. 5 элемент ИЛИ 37 на шестой выход анализатора 12 и устанавливает регистр 42 второго арифметического блока 7 в нулевое состояние.

Импульс (фиг. 8, д), поступающий на

10 первый стробирующий вход анализатора 12 сигналов, проходит через первый элемент И 26, третий и четвертый элементы ИЛИ 27, 28 и поступает на второй и пятый выходы анализатора 12. Это приводит к тому, что в

15 первом арифметическом блоке 6 из накопленной суммы коэффициентов Ki вычитается значение KiB, так как сигнал высокого уровня, поступающий на пятый вход первого арифметического блока 6, переключает

20 мультиплексор 40 и на его выход поступает число (-Ктв), а по импульсу (фиг. 8, д) осуществляется вычитание из суммы коэффициентов Ki значения К-|В.

Одновременно по импульсу (фиг. 8, д)

25 осуществляется запись в регистр 42 второго арифметического блока 7 текущего значения К2. На фиг. 8, к, л показаны изменения суммы коэффициентов Ki и К2 соответственно.

30 Если после очередного суммирования сумма коэффициентов Ki удовлетворяет условию KIH S 2 Ki KiB, то сумму коэффициентов Ki уменьшают до нуля, а сумму коэффициентов «2 корректируют до текуще35 го значения К2. При этом на первом или втором входе анализатора 12 сигналов появляется сигнал высокого уровня, прохождение которого на выход первого элемента 2И-ИЛИ 23 разрешает сигнал высокого

40 уровня, поступающий с пятого входа анализатора 12 сигналов. Сигнал высокого уровня с выхода первого элемента 2И-ИЛИ 23 поступает на первый вход второго элемента И 29 и через первый элемент ИЛИ 24 - на

45 первый вход третьего элемента И 31 и информационный выход блока 12 анализа (фиг. 8, н).

Импульс (фиг. 8, г), поступающий на второй стробирующий вход блока 12 анализа,

50 проходит через третий элемент И 31, шестой элемент ИЛИ 32, на тактовый выход анализатора 12 (фиг. 8, м) и записывает в каскад регистра сдвига 44 логическую 1 (фиг. 8, п). Одновременно импульс (фиг. 8, г)

55 поступает через восьмой элемент ИЛИ 37 на шестой выход анализатора 12 и устанавливает регистр 42 второго арифметического блока 7 в нулевое состояние.

Импульс (фиг. 8, д), поступающий на первый стробирующий вход анализатора

12, проходит через второй элемент И 29, пятый элемент ИЛИ 30 на первый выход блока 12 анализа, а с выхода второго элемента И 29 через четвертый элемент ИЛИ 28 - на пятый выход анализатора 12. Это при- водит к тому, что в первом арифметическом блоке 6 регистр 42 устанавливается в нулевое состояние (сумма коэффициентов Ki уменьшается до нуля), а во втором арифметическом блоке 7 осуществляется запись в регистр 42 текущего значения К2.

Если после очередного суммирования сумма коэффициентов Кт удовлетворяет условию SKi KiH, то суммы коэффициентов Ki и «2 не изменяют, так как на всех входах анализатора 12 сигналов присутствуют сигналы низкого уровня. Поэтому импульс (фиг. 8, г) не проходит на тактовый выход анализатора 12 сигналов, т. е. отсутствует импульс (фиг. 8, м).

Если после очередного суммирования сумма коэффициентов К.2 удовлетворяет условию Z К2в, то из суммы коэффициентов «2 вычитают значение «2в, а сумму коэффициентов Ki корректируют до текуще- го значения KL При этом на шестом или седьмом входе анализатора 12 появляется сигнал высокого уровня, который через девятый элемент ИЛИ 38 поступает на четвертый выход анализатора 12, на первый вход шестого элемента И 39 и через седьмой элемент ИЛИ 34 на первый вход четвертого элемента И 35.

Импульс (фиг.8,г), поступающий на второй стробирующий вход анализатора 12 сиг- налов, проходит через четвертый элемент И 35, шестой элемент ИЛИ 32 и поступает на тактовый выход анализатора 12 (фиг. 8, м) и записывает в регистр сдвига 44 логический О. Одновременно импульс (фиг. 8, г) посту- пает через пятый элемент ИЛИ 30 на первый выход анализатора 12 сигналов и устанавливает регистр 42 первого арифметического блока б в нулевое состояние.

Импульс (фиг. 8, д), поступающий на первый стробирующий вход анализатора 12, проходит через шестой элемент И 39, третий и четвертый элементы ИЛИ 27, 28 на второй и пятый выходы анализатора 12. При этом во втором арифметическом блоке 7 из накопленной суммы коэффициентов К2 вычитается значение К28, т. к, сигнал высокого уровня, поступающий на пятый вход второго арифметического блока 7, переключает мультиплексор 40 и на его выход поступает число (-К2в), а по импульсу (фиг. 8, д) осуществляется вычитание из суммы коэффициентов «2 значения К2в. Одновременно по импульсу (фиг, 8д) осуществляется запись в

регистр 42 первого арифметического блока б текущего значения KL

Если после очередного суммирования сумма коэффициентов К2 удовлетворяет условию К2н 2 К2 К2в, то сумму коэффициентов К2 уменьшают до нуля, а сумму коэффициентов KI корректируют до текущего значения KL

При этом на девятом или десятом входе анализатора 12 появляется сигнал высокого уровня, прохождение которого на выход второго элемента 2И-ИЛИ 33 разрешает сигнал высокого уровня, поступающий с восьмого входа анализатора 12. Сигнал высокого уровня с выхода второго элемента 2И-ИЛИ 33 поступает на первый вход пятого элемента И 36 и через седьмой элемент ИЛИ 34 - на первый вход четвертого элемента И 35.

Импульс (фиг. 8, г), поступающий на второй стробирующий вход анализатора 12 сигналов, проходит через четвертый элемент И 35, шестой элемент ИЛИ 32 на тактовый выход анализатора 12 (фиг. 8,м) и записывает в каскад регистра сдвига 44 логический 0(фиг. 8, п). Одновременно импульс (фиг. 8, г) поступает через пятый элемент ИЛИ 30 на первый выход анализатора 12 и устанавливает регистр 42 первого арифметического блока 6 в нулевое состояние,

Импульс (фиг. 8, д), поступающий на первый стробирующий вход анализатора 12 сигналов, проходит через пятый элемент И 36, восьмой элемент ИЛИ 37 и поступает на шестой выход анализатора, а с выхода пятого элемента И 36 через третий элемент ИЛИ 27 - на второй выход анализатора 12. При этом во втором арифметическом блоке 7 регистра 42 устанавливается в нулевое состояние (сумма коэффициентов К2 уменьшается до нуля), а в первом арифметическом блоке 6 осуществляется запись в регистр 42 текущего значения KL

Если после очередного суммирования сумма коэффициентов К2 удовлетворяет условию 2 К2 К2Н, то суммы коэффициентов KI и К2 не изменяются.

После проверки условий на первый вход счетчика 4 поступает импульс (фиг. 8, е), который устанавливает его в нулевое состояние, после чего счетчик 4 вновь считает импульсы тактового генератора 14, измеряя длительность следующего периода частот- но-манипулированного сигнала и описанный выше процесс повторяется.

Таким образом, предлагаемое техническое решение позволяет устройству для демодуляции частотно-манипулированных сигналов выносить решение о значении

каждой принимаемой информационной посылки в процессе демодуляции частотно- манипулированных сигналов, а получение импульсов в момент вынесения решения о каждой принимаемой посылке позволяет исключить устройства синхронизации в системе связи, в которой используется предлагаемое устройство, что упрощает систему в целом.

Кроме того, в отличие от устройства- прототипа, предлагаемое устройство исключает возможность уменьшения реальной скорости передачи данных, так как нет необходимости ввода в синхронизм устройств синхронизации при вхождении в связь.

Формула изобретения

5 соответственно одни входы мультиплексора и первый вход элемента ИЛИ и третий вход регистра, второй вход элемента ИЛИ и другой вход мультиплексора, пороговый вход которого является пороговым входом ариф0 метического блока.

5 первого элемента 2И-ИЛИ подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ и с первым входом второго элемента И, и к первому входу вто0 рого элемента И, второй вход и выход которого соединены соответственно с вторым входом первого элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, и первым входом пятого эле5 мента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, который подключен к второму входу шестого элемента ИЛИ, первый вход которого соединен с выходом третьего элемента И, к первому

0 входу которого подключен выход первого элемента ИЛИ, и с первым входом восьмого элемента ИЛИ, второй вход которого соединен с третьим входом третьего элемента ИЛИ, второй вход которого подключен к

5 третьему входу четвертого элемента ИЛИ, и с выходом пятого элемента И, первый вход которого соединен с вторым входом второго элемента И и с вторым входом шестого элемента И, первый вход и выход которого со0 единены соответственно с выходом девятого элемента ИЛИ, который подключен к первому входу седьмого элемента ИЛИ, и с третьим входом четвертого элемента ИЛИ, второй и первый входы которого

5 соединены соответственно с выходами второго и первого элементов И, причем выход второго элемента 2И-ИЛИ подключен к второму входу пятого элемента И и к второму входу седьмого элемента ИЛИ, выход которого подключен к второму входу четвертого

элемента И, первый вход которого соединен с вторым входом третьего элемента И, выходы второго, третьего, четвертого, пятого,

равляющими входами которого являются соответственно выходы первого и шестого элементов ИЛИ, входы первого и второго

восьмого и девятого элементов ИЛИ являют-элементов 2И-ИЛИ и входы второго и девяся одними выходами анализатора сигналов,5 того элементов ИЛИ и второй и первый входругими выходами и информационными и уп-ды шестого и четвертого элементов И.

от 2

----7

Фиг. 2

равляющими входами которого являются соответственно выходы первого и шестого элементов ИЛИ, входы первого и второго

элементов 2И-ИЛИ и входы второго и девяФиг. Ц

/РУ0УЈ W0

Ј WOyp we

CW0081

L 1. Li J 1

L

.1

/x

/

JLI

i

j Е-ЗГ--- L

2 i J :

I

/v ;

, i

Риг. /

1

л

II

L,

л.

Г

t

2 i J : i

Фиг. 3

| Авторское свидетельство СССР № 915273, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-03-07—Публикация

1991-01-28—Подача