В настоящее время в связи с интенсивным введением вычислительных средств в состав систем управления(СУ) высокоманевренными объектами авиационной и ракетно-космической техники и особенно в космические аппараты, длительное время работающие при воздействии дестабилизирующих факторов космического пространства, возникла задача создания новых малогабаритных устройств для получения навигационной информации с датчиков (акселерометров и датчиков угловых скоростей).

В идеальном случае в центральную управляющую бортовую вычислительную систему информация должна поступать в цифровом виде, содержащем пространственные координаты центра масс, угловые скорости и углы ориентации объекта управления в пространстве.

В связи с этим все большее распространение получают бескарданные инерциальные системы (БИНС), в состав которых вводят специализированные вычислительные устройства (СВУ), обеспечивающие формирование упомянутой выше системы координат в математическом виде путем непрерывной обработки информации аналоговых чувствительных элементов.

Особенностью этих СВУ является обеспечение быстрого (практически непрерывного) пересчета входной информации датчиков в инерциальную систему координат, что позволяет использовать БИНС вместо сложной и недостаточно надежной гиростабилизированной платформы. Основными вычислительными задачами СВУ являются тригонометрические и матричные вычисления (расчет направляющих углов).

Учитывая необходимость установки БИНС на борту объекта от БИНС и соответственно его СВУ, требуются минимально возможные габаритно-массовые характеристики и энергопотребление. Эти ограничения повлекли широкое внедрение в состав бортовых вычислительных устройств больших и сверхбольших интегральных микросхем (БИС и СБИС) микропроцессоров (МП) и запоминающих устройств (ЗУ), изготавливаемых в основном по КМОП технологии. Это позволяет получить хорошие приборные характеристики, но выдвигает проблему обеспечения работоспособности устройства при длительной работе в условиях воздействия дестабилизирующих факторов космического пространства.

Известны вычислительные устройства, реализованные на основе МП типа 8085 (См. Й.Янсен «Курс цифровой электроники, Т4 / микрокомпьютеры», с.190-195, рис.4.2 и 4.5), устройства содержат микропроцессор и подключенные к нему ЗУ разного типа (постоянные и оперативные).

Реализация такого типа вычислителей позволяет получить небольшие габариты устройств при приемлемом энергопотреблении.

Однако особенность их структуры, а именно последовательное обращение по общим связям к памяти программ и данных не позволяет получить высокую производительность, требуемую от СВУ БИНС, особенно в части вычислений тригонометрических функций и матричных преобразований, в основе которых лежат вычисления типа: АВ+ВС+АС и т.д., т.е. сумма произведений.

Реализация задач пересчета систем координат с вычислением большого числа тригонометрических функций на указанных выше устройствах на основе МП 8085 не удовлетворяет требованиям, предъявляемым к ВУ БИНС.

Известны решения, направленные на повышение производительности микропроцессорных вычислителей путем введения дополнительных блоков, вычисляющих функции, подключаемые к МП через процессор обмена (См. А.А.Мячев «Мини- и микроЭВМ систем обработки информации» Москва, Энергоатомидат, 1991 г. стр.47-49). Данное решение может быть принято за прототип. Вычисление на специальном аппаратурном расширителе (АР) отдельных функций, например Фурье, как предлагается в известном решении, существенно сокращает время вычисления выделенных функций, но производительность микроЭВМ при этом увеличивается незначительно, так как взаимодействие с АР осуществляется через устройство ввода-вывода (процессор обмена, имеющий ограниченную пропускную способность).

С целью повышения производительности ВУ целесообразно реализовать прямую связь МП с АР.

Предлагается вычислительное устройство БИНС, содержащее микропроцессор с подключенными к нему процессором обмена, блоками запоминающих устройств и модуль арифметического расширения (MAP), который подключен к шинам микропроцессора аналогично блокам ЗУ.

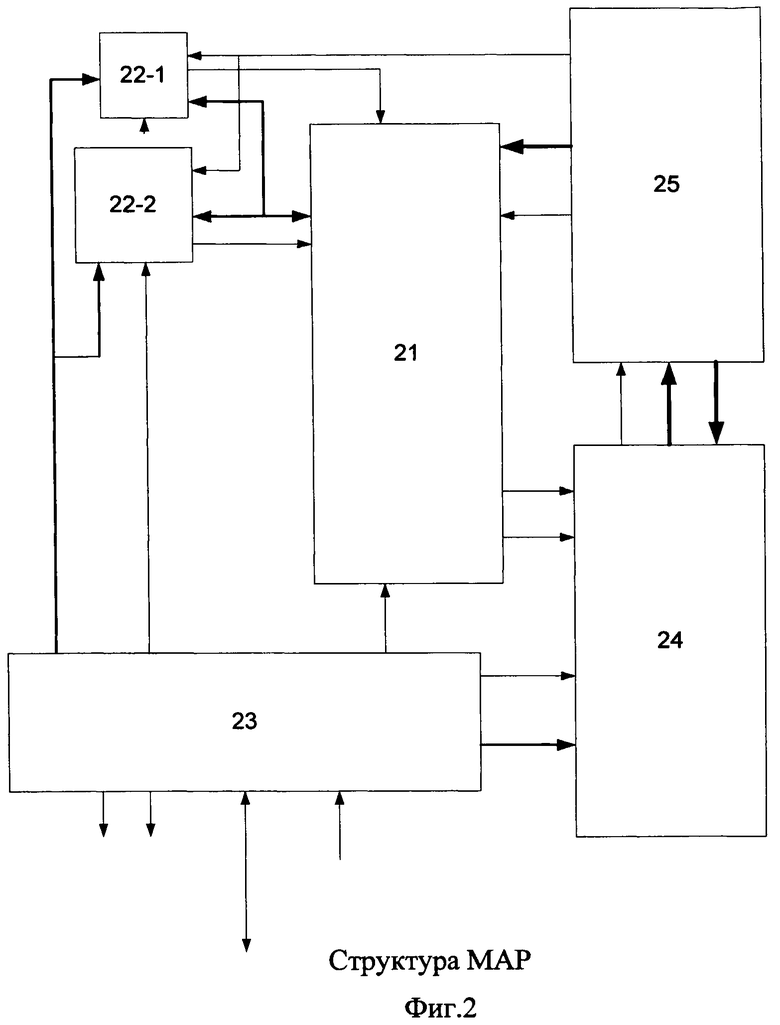

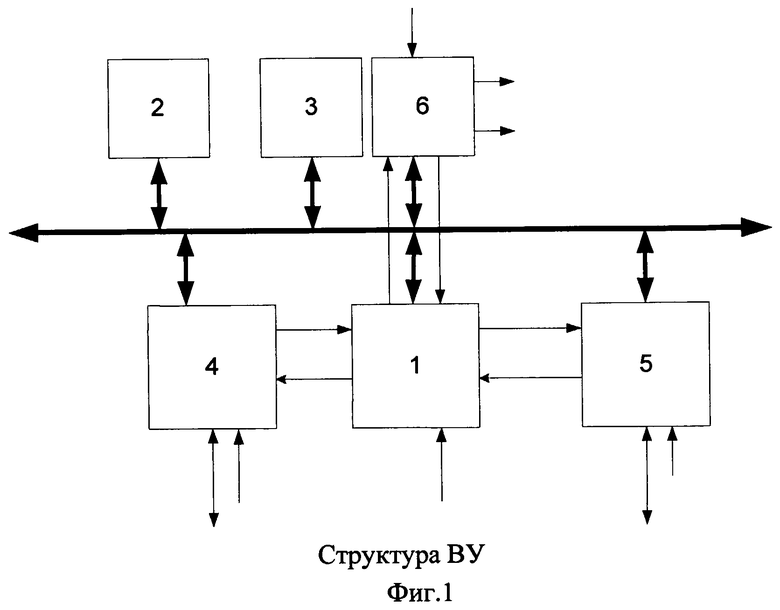

Структура предлагаемого ВУ приведена на чертеже (Фиг.1), где цифрой 1 обозначен микропроцессор (МП), цифрой 2 обозначен модуль оперативного запоминающего устройства (ОЗУ). Цифрой 3 обозначен модуль постоянного запоминающего устройства (ПЗУ), цифрами 4 и 5 обозначены первый и второй процессоры обмена, цифрой 6 обозначен аппаратурный модуль арифметического расширения (МАР). Все эти модули подключены к шинам микропроцессора. Кроме того выход прерывания МП подключен к соответствующему входу MAP, выход прерывания которого подключен к соответствующему входу МП. Управляющий вход MAP является одноименным входом устройства. А его первый и второй частотные выходы подключены соответственно к частотным входам МП и модулей обмена. Двунаправленные входы-выходы процессоров обмена являются входами -выходами вычислительного устройства для связи с датчиками и подсистемой верхнего уровня соответственно.

Структура MAP приведена на чертеже (Фиг.2), где цифрой 21 обозначен арифметический процессор (АП) с умножителем, в качестве которого может быть использован микропроцессор на основе БИС серии 1825 (1825 ВС3 И 1825 ВР), цифрой 22-1 и 22-2 обозначены первый и второй накопитель локального оперативного запоминающего устройства (ЛОЗУ), цифрой 23 обозначен блок связи (БС), цифрой 24 обозначен формирователь адреса микропрограмм (ФАМ), а цифрой 25 обозначено микропрограммное постоянное запоминающее устройство (МПЗУ). АП имеет двунаправленную связь с каждым из накопителей ЛОЗ, а также индивидуальные входы от накопителей. Двунаправленные входы - выходы БС являются входами-выходами MAP, подключенными к МП, а первая и вторая группа адресных выходов БС подключены к адресным входам соответственно ЛОЗУ и ФАМ. Управляющий вход БС является входом MAP и устройства в целом, а первый и второй частотные выходы блока являются выходами MAP. Первая и вторая группа синхронизирующих выходов БС подключены с синхровходам соответственно АП и ФАМ, подключенного информационными входами и выходами к соответствующим выходам и входам МПЗУ, управляющий вход которого подключен к одноименному выходу ФАМ, а управляющие выходы МПЗУ подключены к одноименным входам АП и ЛОЗУ, подключенного информационными и адресными шинами к БС, управляющий вход которого является управляющим входом MAP. Кроме того выходы признаков АП подключены к одноименным входам ФАМ, а первый и второй выходы ЛОЗУ подключены к первому и второму входам АП.

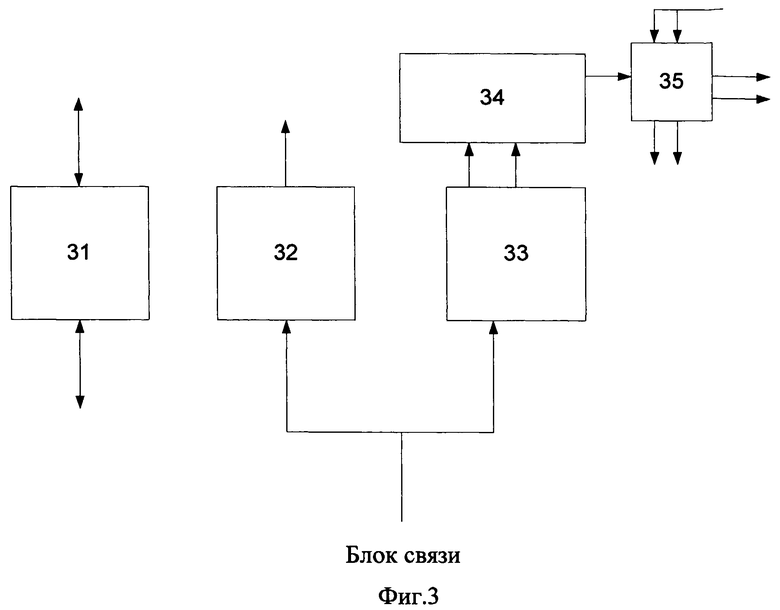

Структура блока связи приведена на чертеже (Фиг.3), где цифрой 31 обозначен регистр данных, цифрами 32 и 33 обозначены соответственно младший и старший регистры адреса, цифрой 34 обозначен дешифратор, а цифрой 35 - формирователь синхроимпульсов, синхронизирующие первый и второй частотные выходы которого являются выходами блока. Управляющие входы являются входом блока, а запускающий вход формирователя подключен к выходу дешифратора, подключенного входами к выходам старшего регистра адреса, входы которого совместно с входами младшего регистра адреса являются входом блока, при этом выходы младшего регистра адреса, информационные шины и входы-выходы регистра данных являются соответствующими входами и выходами блока.

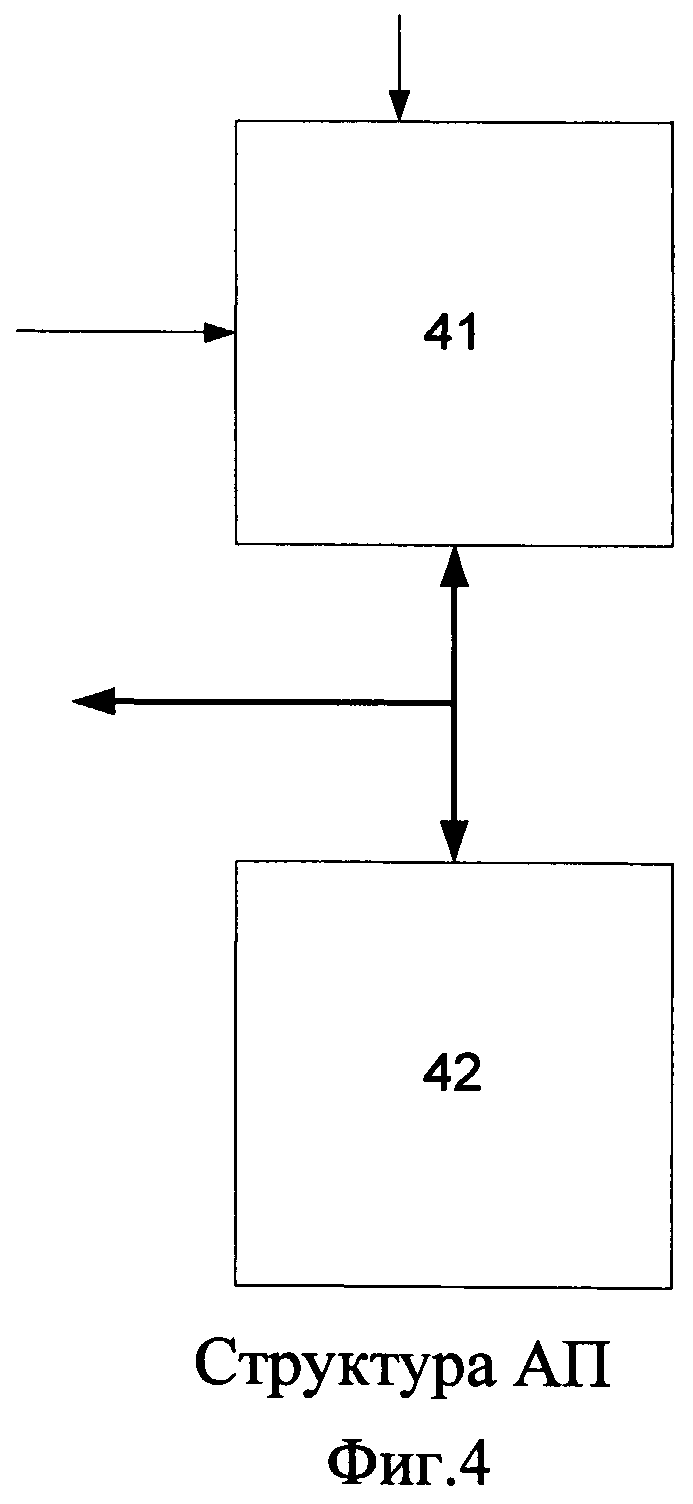

Состав АП приведен на чертеже (Фиг.4), где цифрами 41 и 42 обозначены соответственно умножитель и арифметико-логическое устройство (сумматор), связанные между собой двунаправленной связью. При этом умножитель имеет два входа, являющиеся входами АП, подключенными к ЛОЗУ.

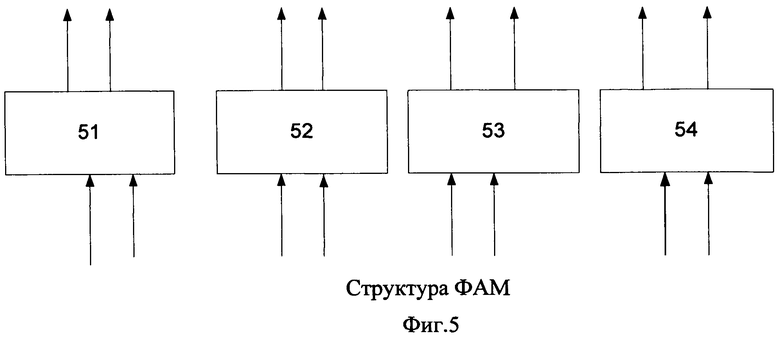

Структура формирователя адреса микрокоманд (ФАМ) приведена на чертеже (Фиг.5), где цифрой 51 обозначен регистр смещения, цифрой 52 обозначен регистр кода операции, цифрой 53 обозначен регистр признаков и цифрой 54 обозначен счетчик адреса.

Входы регистра кода операции и информационный и счетный входы счетчика являются входами формирователя, подключенными к выходу блока связи. Входы регистра признаков являются входами формирователя, подключенными к выходам АП. Выходы регистров и счетчика образуют адрес МПЗУ и являются выходами формирователя.

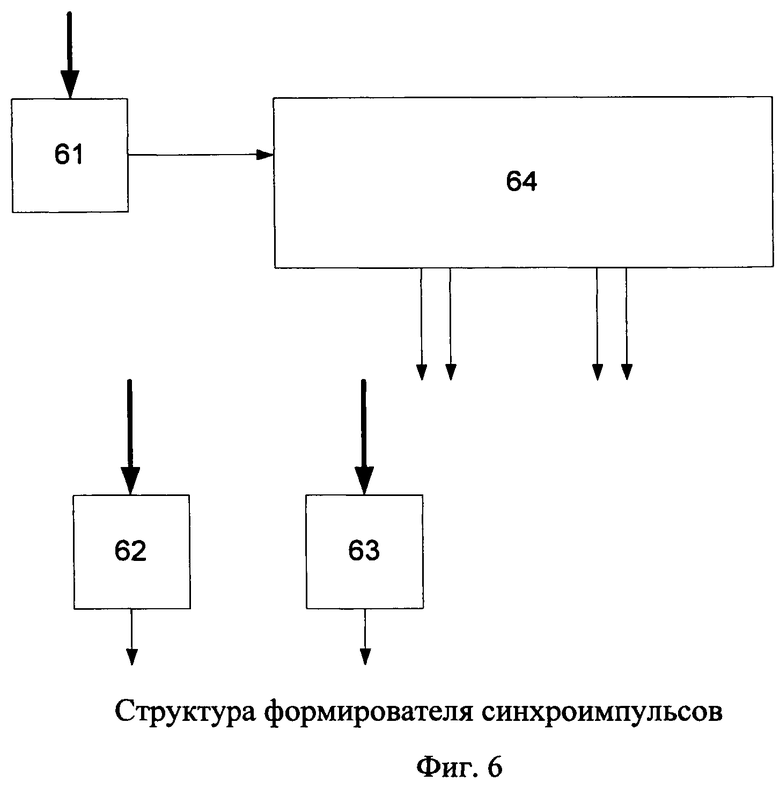

Структура формирователя синхроимпульсов приведена на чертеже (Фиг.6), где цифрами 61, 62, 63 обозначены соответственно основной, первый и второй задающие генераторы частоты, а цифрой 64 обозначен узел формирования синхроимпульсов, выходы которого являются синхронизирующими выходами формирователя, а выходы первого и второго генераторов являются первым и вторым частотным выходами формирователя, управляющий вход которого является входом первого и второго задающих генераторов.

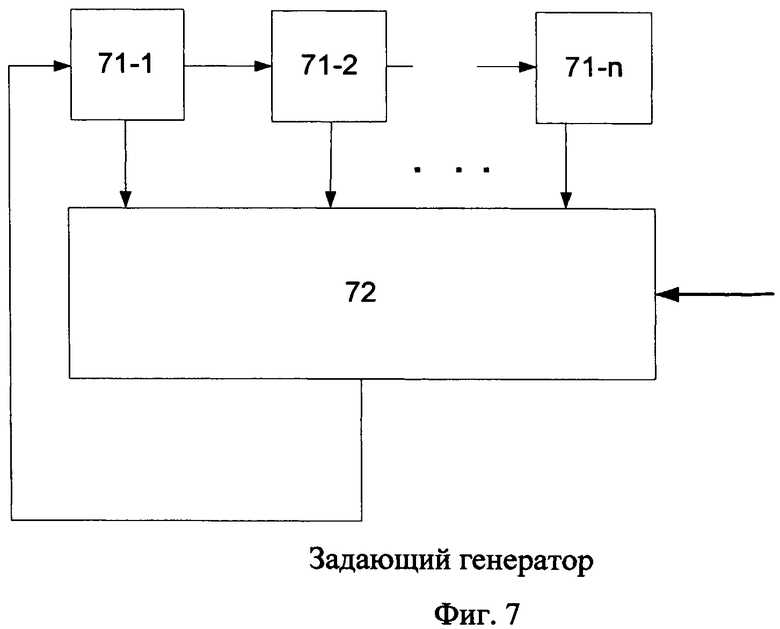

Схема генератора частоты приведена на чертеже (Фиг.7), где цифрами от 71-1 до 71-n обозначены n последовательно соединенных инверторов, подключенных к входу мультиплексора 72, выход которого подключен к входу первого инвертора, а вход является управляющим входом генератора.

Структура узла формирования синхроимпульсов (СИ) приведена на чертеже (Фиг.8), где цифрами 81-1 и 81-2 обозначены младшая и старшая секции сдвигающего регистра, цифрой 83 обозначен элемент И, цифрой 84 обозначен триггер привязки, цифрами от 85-1 до 85-n обозначены триггеры-формирователи, управляющий вход триггера привязки является одноименным входом узла, а синхронизирующий вход подключен к первому выходу младшей секции сдвигающего регистра, вход которой является входом узла, подключенным к основному генератору частоты, второй выход секции подключен ко входу элемента И, выход которого подключен ко входу второй секции сдвигающего регистра, четные и нечетные выходы которой являются соответственно запускающими и сбрасывающими входами триггеров-формирователей, выходы которых являются выходами узла формирования.

Устройство работает следующим образом:

МП по своей программе, размещенной в ПЗУЗ, выполняет вычисления.

Если требуется вычислить тригонометрическую функцию или провести операции с матрицами, МП проводит запись аргумента по определенному адресу ЛОЗУ MAP, затем делает посылку по фиксированному адресу в MAP. В коде адреса кроме адреса модуля содержится и код операции, подлежащей выполнению. При действии с матрицами вначале в ЛОЗУ MAP записываются компоненты матриц по определенным заранее адресам, а потом делается посылка по фиксированному адресу MAP с кодом операции.

Получив посылку по фиксированному адресу, блок связи 23 проводит дешифрацию в блоке 34, который запускает формирователь синхроимпульсов 35. С началом поступления синхроимпульсов в регистр кода операции и счетчик ФАМ из БС заносятся начальные значения, начинается выборка микрокоманд и выполнение заданной операции с записью результатов в определенные адреса ЛОЗУ MAP и АП отключается от шин ЛОЗУ. По окончанию записи микропрограммно формируется сигнал прерывания, поступающий в МП, который производит чтение результата из ЛОЗУ MAP и продолжает работу по своей программе с обращением к MAP при необходимости вычисления функций или действий с матрицами.

Дополнительно предусмотрено управление быстродействием устройства путем перестройки частот задающих генераторов по командам центральной бортовой вычислительной системы или командной радиолинии.

Перестройка быстродействия производится для отслеживания изменения параметров БИС во времени или из-за действия ионизирующего излучения космического пространства. Кроме того на отдельных наиболее загруженных по вычислениям участках возможно плановое повышение быстродействия. Возможное максимальное быстродействие для каждого интервала работы определяется по результатам тестовых проверок отдельных компонентов устройства и устанавливается индивидуально для каждого компонента, для чего в состав формирователя синхроимпульсов введены несколько задающих генераторов, для каждого из которых в общем управляющем слове отведена своя часть кода.

Все эти решения обеспечивают максимальную производительность вычислительного устройства на протяжении всего времени работы инерциальной системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 2011 |

|

RU2452125C1 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2011 |

|

RU2444052C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| БЕСПЛАТФОРМЕННАЯ ИНЕРЦИАЛЬНАЯ НАВИГАЦИОННАЯ СИСТЕМА | 2013 |

|

RU2563333C2 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

| СИСТЕМА АСТРОНАВИГАЦИИ | 2013 |

|

RU2548927C1 |

| АДАПТИВНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2477882C2 |

Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных средств для систем управления высокоманевренными объектами авиационной или ракетно-космической техники. Технический результат - повышение производительности вычислительного устройства. Вычислительное устройство содержит микропроцессор, оперативное, постоянное запоминающие устройства и первый процессор обмена, подключенные к шинам микропроцессора, причем к шинам процессора подключены второй процессор обмена и модуль арифметического расширения, управляющий вход которого является входом устройства, вход и выход прерывания подключены соответственно к выходу и входу микропроцессора, а первый и второй частотные выходы подключены соответственно к входам микропроцессора и входам процессоров обмена, входы-выходы которых являются входами-выходами устройства. 7 з.п. ф-лы, 8 ил.

1. Вычислительное устройство, содержащее микропроцессор, оперативное, постоянное запоминающие устройства и первый процессор обмена, подключенные к шинам микропроцессора,

отличающееся тем, что дополнительно к шинам процессора подключены второй процессор обмена и модуль арифметического расширения, управляющий вход которого является входом устройства, вход и выход прерывания подключены соответственно к выходу и входу микропроцессора, а первый и второй частотные выходы подключены соответственно к входам микропроцессора и входам процессоров обмена, входы-выходы которых являются входами-выходами устройства.

2. Вычислительное устройство по п.1, отличающееся тем, что модуль арифметического расширения содержит арифметический процессор с умножителем, связанный информационно-адресными и дополнительными шинами с локальным запоминающим устройством, блок связи, формирователь адреса микропрограмм и микропрограммное запоминающее устройство, подключенное управляющими выходами к арифметическому процессору и локальному запоминающему устройству, а управляющим и первым адресным входом и выходом - к формирователю адреса, входы признаков которого подключены к арифметическому процессору, а синхронизирующие и вторые адресные входы - к блоку связи, который синхронизирующими выходами подключен к арифметическому процессору, адресными и информационными шинами подключен к локальному запоминающему устройству, а его управляющий вход, двунаправленные входы-выходы, первый и второй частотные выходы являются соответствующими входом, входом-выходом и выходами модуля.

3. Вычислительное устройство по п.2, отличающееся тем, что блок связи содержит регистр данных, информационные шины и входы-выходы которого являются одноименными шинами и входами-выходами блока, младший и старший регистры адреса, входы которых являются входом блока, причем выход младшего регистра является выходом блока, а выход старшего подключен к дешифратору, подключенного выходом к формирователю синхроимпульсов, управляющие входы которого являются входом блока, а синхронизирующие, первый и второй частотные выходы являются одноименными выходами блока.

4. Вычислительное устройство по п.2, отличающееся тем, что арифметический процессор содержит умножитель и арифметико-логическое устройство, связанные между собой двунаправленной шиной, а входы умножителя являются входами арифметического процессора.

5. Вычислительное устройство по п.2, отличающееся тем, что формирователь адреса микропрограмм содержит регистры смешения, кода операции, признаков и счетчик, входы и выходы которых являются входами и выходами формирователя.

6. Вычислительное устройство по п.3, отличающееся тем, что формирователь синхроимпульсов содержит основной, первый и второй задающие генераторы, входы которых являются управляющим входом формирователя, а выходы первого и второго генераторов являются соответственно первым и вторым частотными выходами формирователя, а выход основного генератора подключен к входу узла формирования синхроимпульсов, выходы которого являются выходами формирователя.

7. Вычислительное устройство по п.5, отличающееся тем, что задающий генератор содержит n последовательно соединенных инверторов, подключенных выходами к мультиплексору, вход которого является управляющим входом генератора, а выход подключен к входу первого инвертора.

8. Вычислительное устройство по п.5, отличающееся тем, что узел формирования синхроимпульсов содержит первую и вторую секции сдвигового регистра, при этом вход первой секции является входом узла, дополнительный выход подключен к синхронизирующему входу триггера привязки, вход которого является управляющим входом узла, а выход подключен к первому входу элемента И, у которого первый вход подключен к выходу первой секции, второй вход подключен к выходу триггера привязки, а выход подключен к входу второй секции, четные и нечетные выходы которой подключены к запускающим и сбрасывающим входам n триггеров-формирователей, выходы которых являются выходами узла.

| СХЕМА ОПТИЧЕСКОЙ СИСТЕМЫ ДЛЯ УНИВЕРСАЛЬНОГО ВЫЧИСЛИТЕЛЬНОГО УСТРОЙСТВА | 2004 |

|

RU2386161C2 |

| УПРАВЛЯЮЩАЯ ЭВМ | 2005 |

|

RU2316807C2 |

| ЕР 0525375 В1, 28.11.2001. | |||

Авторы

Даты

2012-12-10—Публикация

2011-07-06—Подача