Системы управления подвижными объектами как авиационной, так и ракетно-космической техники в качестве одного из основных звеньев включают подсистему инерциальной навигации, которая традиционно создавалась на основе гироскопической платформы. Однако ограниченный диапазон изменения угловых положений объекта практически исключает ее использование для высокоманевренных объектов. В связи с этим в последнее время все большее распространение получают бескарданные инерциальные системы (БИНС), в которых отсутствуют механические гироскопы, задающие базовую ориентацию инерциальной системы координат. В БИНС инерциальная система координат рассчитывается математически бортовыми вычислительными устройствами по информации, поступающей с датчиков угловых скоростей, в качестве которых используют или кольцевые лазерные датчики, или волоконно-оптические гироскопы. Независимо от типа датчика требуется высокоскоростная обработка информации об угловых скоростях и ее пересчет в инерциальную систему координат. В основе этих преобразований лежат матричные вычисления, где в качестве элементов матриц используются тригонометрические функции типа sinx и cosx. Heсмотря на существенный прогресс в области создания бортовых цифровых вычислительных машин (БЦВМ) их производительности оказывается недостаточно для решения задач БИНС, так как программное вычисление тригонометрических функций занимает существенное время (несколько милисекунд). В связи с этим возникает необходимость введения в состав БЦВМ или дополнительно к ней узкоспециализированных вычислителей, ориентированных на решение задачи БИНС, и в первую очередь на быстрое вычисление тригонометрических функций. Рядом специалистов в последнее время для вычисления функций одной или нескольких переменных предлагается использовать нейронные сети. Данное направление представляется достаточно перспективным для модернизации БЦВМ с целью ускорения, решения задач БИНС. Общеизвестно, что тригонометрические функции sinx и cosx могут быть представлены полиномом, представляющим сумму членов различных степеней переменной x с соответствующими коэффициентами. Для быстрой реализации вычислений в этом случае применимы нейронные сети, в которых необходимо реализовать быстрое суммирование и умножение. По нейронным вычислителям известны предложения (См. статью А.Н.Горбань «Обобщенная апроксимационная теорема и вычислительные возможности нейронных сетей» / Сибирский журнал вычислительной математики 1998, Т1 №1, стр.12-24), где на рисунках (рис.1 - рис.4) приведены примеры построения компонентов нейронных сетей на основе сумматоров с набором весовых коэффициентов на входе. Однако отсутствие в их составе аппаратурных умножителей и средств задания коэффициентов для «обучения» сети, что является обязательным при настройке вычисления конкретной функции, не позволяет использовать их для создания специализированных вычислителей БИНС. Некоторые решения по компонентам нейронных сетей приведены в другом источнике (См. Л.Н.Ясинецкий «Введение в искусственный интеллект». Учебн. пособие для ВУЗов, 2 издание. «Академия», где на стр.29 приведено описание нейрона Мак-Каллона, Питтса на базе нескольких компонентов, содержащих сумматор произведений переменной и коэффициентов, элементы И, ИЛИ, НЕ). Однако отсутствие умножителей и средств задания коэффициентов для обучения также не позволяет использовать эти решения для выполнения поставленной задачи: быстрого вычисления тригонометрических функций.

Для систем управления космическими аппаратами с длительным временем работы существует также задача нейтрализации отказов, вызванных естественным старением аппаратуры и потоком тяжелых заряженных частиц.

В связи с этим при использовании цифровых вычислительных устройств в системах управления также требуется нейтрализации отказов как катастрофических, вызванных естественным старением аппаратуры и потоком тяжелых заряженных частиц, так и параметрических изменений из-за дозовых эффектов параметров интегральных микросхем, на основе которых создаются бортовые вычислительные устройства. Все это требует применения новых решений в части построения бортовых вычислительных устройств, ориентированных на использование в системе управления БИНС. Для решения поставленных проблем предлагается использовать ориентированный на решение задач БИНС НЕЙРОПРОЦЕССОР (далее по тексту Процессор), состав которого приведен на фигуре 1.

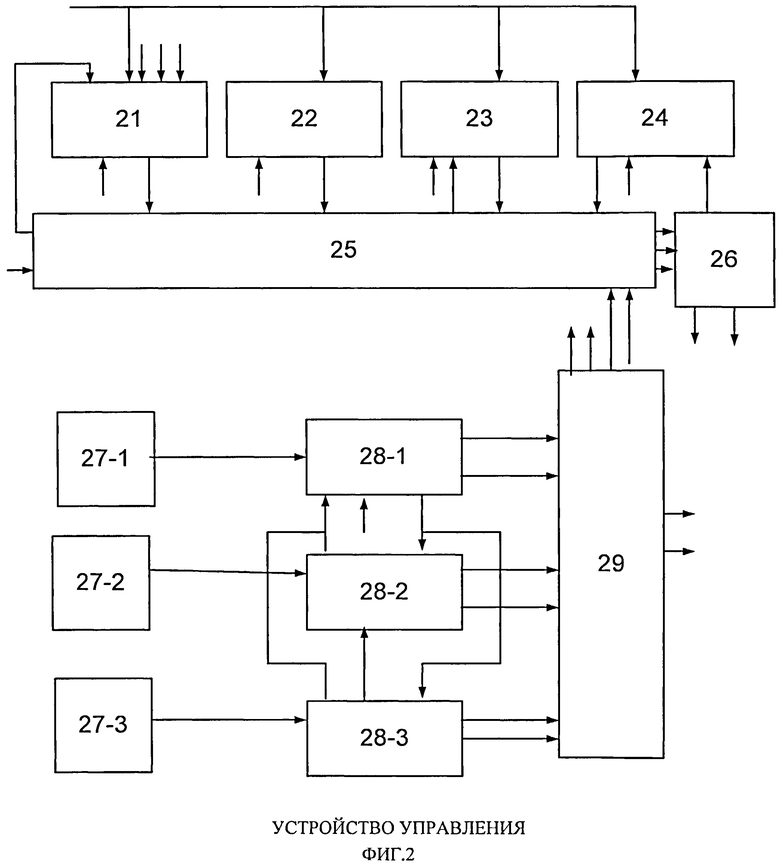

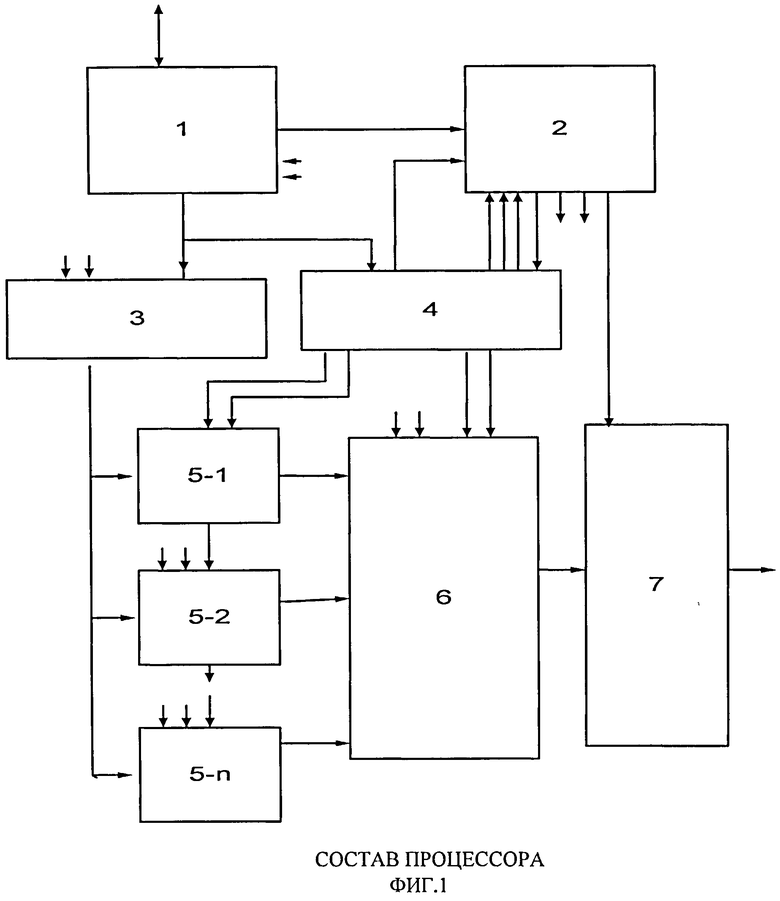

В состав процессора входят блок связи (БС) 1, связанный двунаправленной линией с БЦВМ или процессором верхнего уровня при размещении нейропроцессора в составе БЦВМ, микропрограммное устройство управления (УУ) 2, буферный регистр (БР) 3 для хранения аргумента, запоминающее устройство (ЗУ) 4 для хранения коэффициентов обучения (настройки) процессора, n последовательно включенных умножителей, обозначенных цифрами от 5-1 до 5-n, сумматор 6 и выходной регистр 7 для записи значения вычисленной функции, выход которого является выходом процессора. Первый выход БС подключен к УУ, второй - к БР и ЗУ. Выход БР подключен к первым входам всех умножителей, ко вторым входам которых, начиная со второго, подключен выход переноса предыдущего умножителя. Управляющие и синхронизирующие выходы УУ подключены соответственно к управляющим и синхронизирующим входам остальных блоков. При этом контрольные выходы ЗУ подключены к входам смещения УУ. Выходы ЗУ подключены к настроечным входам умножителей и сумматора, к входам которого подключены основные выходы умножителей. Выход сумматора подключен к выходному регистру, выход которого является выходом процессора. Устройство управления содержит регистр смешения 21, входы которого являются входами смещения устройства, а также регистры кода операций 22, базы адреса 23 и счетчик 24. Установочные входы регистров и счетчика, а также вход накопителя 25 являются входом устройства, подключенным к БС, а адресные входы накопителя являются выходами регистров и счетчика, адресный выход накопителя подключен к входу регистра базы адреса. Выходы накопителя подключены к буферным элементам 26, выходы которых являются выходами устройства. Дополнительный выход буферного элемента подключен к счетному входу счетчика.

Кроме того, УУ (См. фиг.2) содержит три канала синхронизатора, в каждом из которых содержится три генератора импульсов (27-1, 27-2 и 27-3), управляющие входы которых являются входом устройства, а выходы подключены к своим формирователям (28-1, 28-2 и 28-3). Фазирующий выход каждого из формирователей подключен к одноименным входам двух других, а синхровыходы формирователей подключены к входам мажоритарных элементов 29, выходы которых являются синхронизирующими выходами устройства, а дополнительные выходы подключены к стробирующим входам регистров и счетчика.

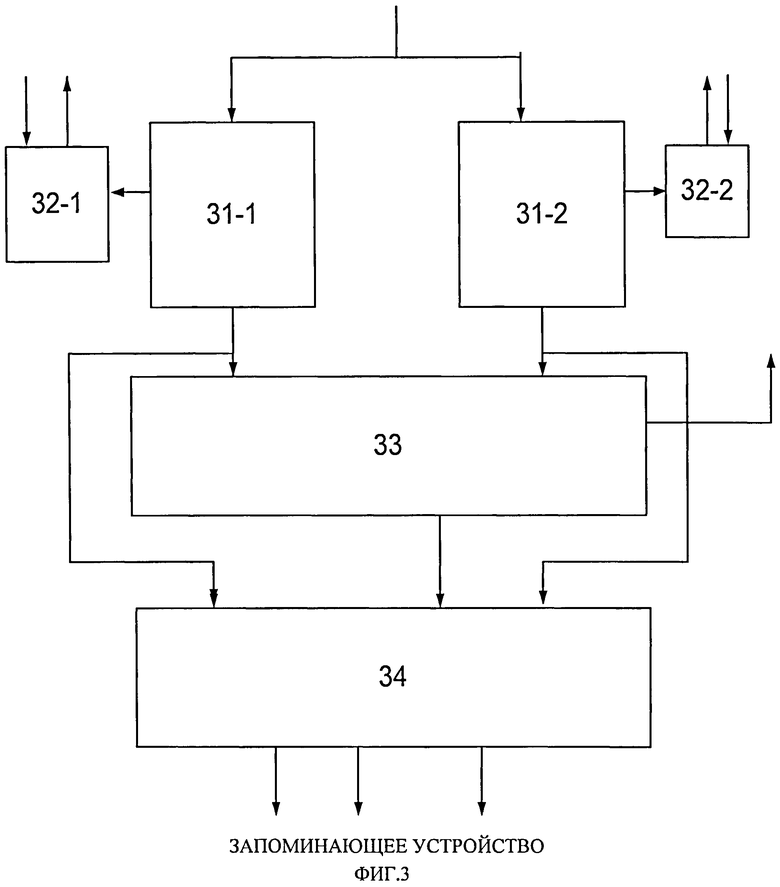

Запоминающее устройство(См. фиг.3) содержит первый 31-1 и второй 31-2 накопители, контрольные выходы которых подключены соответственно к первому 32-1 и второму 32-2 сумматорам, а выходы накопителей подключены к входам схемы сравнения 33, первый выход которой является первым контрольным выходом ЗУ, а второй выход подключен к управляющему входу переключателя накопителей 34, выход которого является выходом ЗУ, а входы накопителей - его входом. Выходы первого и второго сумматоров являются соответственно вторым и третьим контрольными выходами ЗУ, а их управляющие входы - входом ЗУ.

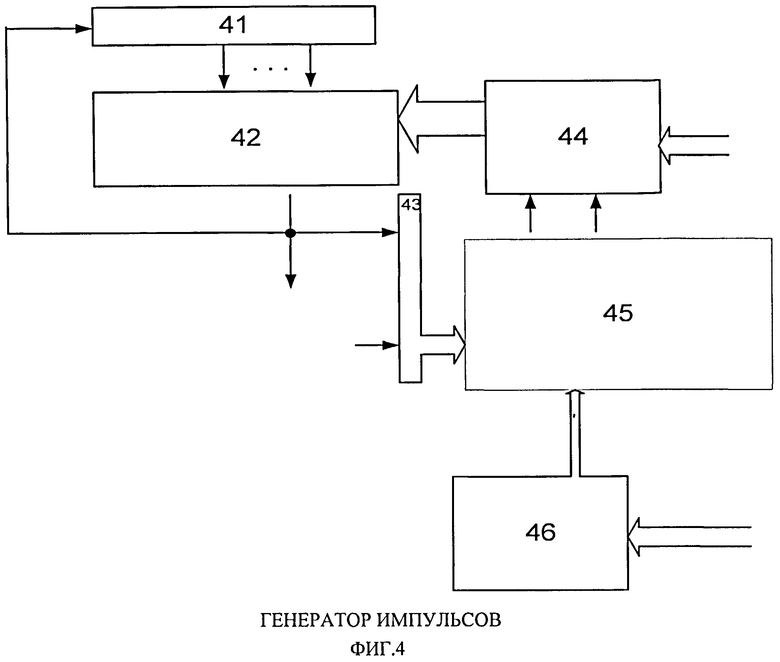

Генератор импульсов (См. фиг.4) содержит n включенных последовательно инверторов 41, выходы которых подключены к входам мультиплексора 42, выход которого является выходом генератора и подключен к входам первого инвертора и счетчика частоты 43, выход которого подключен к первому входу схемы сравнения 45, к второму входу которой подключен выход регистра кода частоты 46, а инкрементный и декрементный выходы схемы сравнения подключены в одноименным входам счетчика кода частоты 44, выход которого подключен к управляющему входу мультиплексора, а вход этого счетчика и вход регистра кода частоты являются управляющим входом генератора.

На фигуре 5 приведена структура формирователя. Он содержит элемент И 51, первый вход которого является входом формирователя, подключенным к генератору импульсов. Выход элемента подключен к входам счетчика 52 и сдвигового регистра 53. Выходы счетчика подключены к входам дешифратора 54, выход которого подключен к запускающему входу триггера останова 55, выход которого является фазирующим выходом формирователя и подключен к второму входу элемента И и первому входу мажоритарного элемента 57, выход которого подключен к входу триггера пуска 56, выход которого подключен к сбрасывающему входу триггера останова, а второй и третий входы мажоритарного элемента подключены к выходам триггеров привязки 58, стробирующий вход которых объединен с первым входом элемента И, а входы триггеров являются фазирующими входами формирователя. Кроме того выходы нечетных и четных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам n триггеров формирователей (от 59-1 до 59-n) выходы которых являются синхронизирующими выходами формирователя.

Процессор работает следующим образом.

После включения питания в устройстве управления начинают работать задающие генераторы и формирователи и через несколько (3-4) периодов высокой частоты на выход поступают сфазированные, прошедшие мажоритар, синхроимпульсы. В соответствии с кодами, записанными в регистры 21-23 и счетчик 24, начальными значениями адреса из накопителя 25 начинают выбираться коды микрокоманд, которые после буферных элементов 26 начинают поступать на блоки процессора, а одновременно с ними из формирователей 28, пройдя мажоритар 29, в блоки начинают поступать синхроимпульсы.

В запоминающем устройстве 4 записаны весовые коэффициенты для задания весов входов каждого слоя нейропреобразователей для разных функций. После получения в блок связи значения аргумента и типа функции происходит перезапись по микропрограммным сигналам, начинающим поступать из накопителя 25, значения аргумента в буферный регистр 3 и кода операции в регистр 22 устройства управления, а также остальных начальных значений в остальные регистры и счетчик для формирования первого адреса выборки микрокоманд из накопителя 25, дальнейшие адреса формируются как комбинация кодов, записанных в текущей микрокоманде и поступающих в регистр базы адреса и регистр смещения 21 совместно с внешними сигналами, обеспечивающими переход на ветки микропрограммы по условиям, которыми, в частности, являются контрольные сигналы запоминающего устройства 4.

В первом умножителе 5-1 производится умножение аргумента самого на себя, т.е. появляется значение х2, на втором умножителе происходит умножение полученного значения на аргумент, т.е. появляется третья степень аргумента х3.

Далее происходит получение следующих степеней аргумента в соответствии с требуемой точностью. Полученные значения поступают на входы сумматора 6, на настроечные входы которого поступают значения весовых коэффициентов из запоминающего устройства 4.

В результате на выходе сумматора появляется значение вычисленной функции, которое может быть считано из выходного регистра 7. Такое построение обеспечивает достаточно быстрое вычисление функции, так как времена определяются только задержками комбинационных элементов умножителя и сумматора, которые при их реализации в виде БИС достаточно малы, так, например, при использовании в качестве умножителя БИС 1825 ВР5, а в качестве сумматора БИС 1825 ВСЗ функция sinx вычисляется за 2 мкс против нескольких миллисекунд при вычислении по программе бортовой вычислительной машины, что обеспечивает требуемую скорость решения задач БИНС. Кроме того, введение резервирования накопителей ЗУ с контролем их исправности схемой сравнения 33 и определением места отказа с помощью контрольного суммирования массивов коэффициентов сумматорами 32-1 и 32-2 с последующим выбором исправного накопителя по микропрограмме в устройстве управления и подключении к выходу сигналов исправного накопителя позволяет нейтрализовать определенные отказы катастрофического характера в одном из основных узлов нейропроцессора - его запоминающем устройстве коэффициентов. А наличие связи этого ЗУ через блок связи 1 с внешней подсистемой позволяет проводить настройку («обучение») процессора вычисления различных функций, что может быть сделано как на заводе-изготовителе аппаратуры, так и в процессе работы по программе бортовой вычислительной машины, а наличие контроля с отключением накопителя с искаженными коэффициентами исключает «переобучение» нейропроцессора. Для сохранения работоспособности процессора и, более того, подбора оптимального для текущего состояния цифровых элементов быстродействия в блоке управления реализован режим перестройки частоты, для чего введено управление задающими генераторами заданием кодов требуемой частоты в счетчик кода частоты 45 и регистр кода частоты 4. Поддержание требуемого номинала, выбранного, например, на основе проведения тестовых проверок, происходит автоматически изменением значения счетчика 45 по сигналам схемы сравнения, сравнивающей текущее значение частоты, определяемое счетчиком 44, со значением заданным в регистр 47. Таким образом, предложенные решения позволяют не только существенно, примерно на порядок, сократить время вычисления функций, но и проводить изменение вида вычисляемых функций «обучением» процессора путем записи нужных массивов коэффициентов в запоминающее устройство 4. Но и заметно повысить устойчивость работы процессора не только при возникновении катастрофических отказов, вызванных, например, искажением информации в запоминающем устройстве попаданием тяжелых заряженных частиц, а также расширить область сохранения оптимальной работоспособности (быстродействия) при изменении параметров элементов (транзисторов) БИС, вызванных дозовыми эффектами из-за действия ионизирующих излучений как естественных, так и искусственных. Все это делает применение предлагаемого процессора предпочтительным по сравнению с известными решениями.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| БЕСПЛАТФОРМЕННАЯ ИНЕРЦИАЛЬНАЯ НАВИГАЦИОННАЯ СИСТЕМА | 2013 |

|

RU2563333C2 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО БИНС | 2011 |

|

RU2469376C1 |

| Нейропроцессор (NPU) | 2024 |

|

RU2825124C1 |

| СИСТЕМА АСТРОНАВИГАЦИИ | 2013 |

|

RU2548927C1 |

| ТЕХНОЛОГИЧЕСКАЯ УВМ | 2013 |

|

RU2563139C2 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2520350C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных средств для систем управления высокоманевренными объектами авиационной и ракетно-космической техники, где требуется быстрое вычисление функций, например тригонометрических, используемых в матричных преобразованиях при решении задач формирования инерциальной системы координат по информации датчиков угловых скоростей, а также при решении задачи сохранения работоспособности вычислителей при изменениях параметров элементов БИС из-за действия ионизирующих излучений естественного или искусственного происхождения. Техническим результатом является уменьшение отказов интегральных микросхем. Устройство содержит блок связи с бортовой ЭВМ или управляющей подсистемой верхнего уровня, устройство управления, буферный регистр, запоминающее устройство, умножители, сумматор, выходной регистр. 4 з.п. ф-лы, 5 ил.

1. Нейропроцессор, содержащий сумматор, отличающийся тем, что в его состав дополнительно введены блок связи, вход-выход которого является входом-выходом процессора, первый выход подключен к устройству управления, а второй - к входам буферного регистра и запоминающего устройства, управляющие и синхронизирующие выходы которого подключены к остальным блокам процессора, а выход буферного регистра подключен к первым входам n последовательно включенных умножителей, у которых, начиная со второго, вторые входы подключены к выходу переноса предыдущего умножителя, а выходы умножителей подключены к входам сумматора, выход которого подключен к выходному регистру, выход которого является выходом процессора, причем управляющий вход запоминающего устройства подключен к одноименному выходу устройства управления, а первая и вторая группы настроечных выходов запоминающего устройства подключены соответственно к одноименным входам умножителей и сумматора, а первый, второй и третий контрольные выходы запоминающего устройства подключены к входам смещения устройства управления.

2. Нейропроцессор по п.1, отличающийся тем, что устройство управления содержит регистры смещения, кода операций, базы и счетчик, установочные входы которых являются входом устройства, а выходы подключены к адресным входам накопителя, вход которого является входом устройства, адресный выход подключен к входу регистра базы, входы смещения регистра смещения являются одноименными входами устройства, а выходы накопителя подключены к входам буферных элементов, выходы которых являются управляющими выходами устройства, а их дополнительный выход подключен к счетному входу счетчика, при этом устройство содержит три задающих генератора, управляющий вход которых является входом устройства, а выходы подключены к своим формирователям, фазирующий выход каждого из которых подключен к фазирующим входам двух других формирователей, а синхронизирующие выходы подключены к мажоритарным элементам, выходы которых являются синхронизирующими выходами устройства, а дополнительные выходы подключены к синхронизирующим входам регистров, накопителя и счетчика.

3. Нейропроцессор по п.1, отличающийся тем, что запоминающее устройство содержит первый и второй накопители, входы которых являются входом устройства, а их выходы подключены к входам переключателя накопителей и входам схемы сравнения, сигнальный выход которой является первым контрольным выходом устройства, а управляющий выход подключен к управляющему входу переключателя, выходы которого являются выходами устройства, причем дополнительные выходы первого и второго накопителей подключены к входам одноименных сумматоров, управляющие входы которых являются одноименными входами устройства, а их выходы являются соответственно вторым и третьим контрольными выходами устройства.

4. Нейропроцессор по п.2, отличающийся тем, что генератор импульсов содержит n последовательно включенных инверторов, выходы которых подключены к входам мультиплексора, выход которого является выходом генератора и подключен к входу первого инвертора и входу счетчика частоты, выход которого подключен к первому входу схемы сравнения, к второму входу которой подключен выход регистра кода частоты, а инкрементный и декрементный выходы схемы сравнения подключены к одноименным входам счетчика кода частоты, выход которого подключен к управляющему входу мультиплексора, а входы счетчика кода частоты и регистра кода частоты являются управляющим входом генератора.

5. Нейропроцессор по п.2, отличающийся тем, что формирователь содержит элемент И, первый вход которого является входом формирователя, а выход подключен к входам сдвигового регистра и счетчика, выходы которого подключены к входу дешифратора, выход которого подключен к запускающему входу триггера останова, выход которого является выходом формирователя и подключен к второму входу элемента И и первому входу мажоритарного элемента, выход которого подключен к входу триггера пуска, выход которого подключен к сбрасывающему входу триггера останова, а второй и третий входы мажоритарного элемента подключены к выходам триггеров привязки, стробирующий вход которых объединен с первым входом элемента И, а входы являются фазирующими входами формирователя, причем выходы нечетных и четных разрядов сдвигового регистра подключены к запускающим и сбрасывающим входам триггеров-формирователей, выходы которых являются синхронизирующими выходами формирователя.

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ВЫЧИСЛЕНИЯ ПРЯМЫХ ТРИГОНОМЕТРИЧЕСКИХ ФУНКЦИЙ | 2004 |

|

RU2326427C2 |

| US 5278945 A, 11.01.1994 | |||

| DE 4219060 A1, 05.11.1992. | |||

Авторы

Даты

2013-01-20—Публикация

2011-10-28—Подача