Изобретение относится к преобразовательной технике и может быть использовано для управления ключевыми элементами инвертора с синусоидально-модулированным выходным напряжением.

Цель изобретения-увеличение КПД за счет улучшения качества модуляции путем уменьшения содержания неосновных гармоник в выходном напряжении инвертора при формировании импульсов заполнения с постоянной длительностью периода и содержанием целого числа периодов этих импульсов в каждом отрезке аппроксимации, при этом длительность импульсов заполнения формируется равной произведению численного значения входного кода и ступенчато аппроксимированного значения синуса угла (фазы) выходного напряжения.

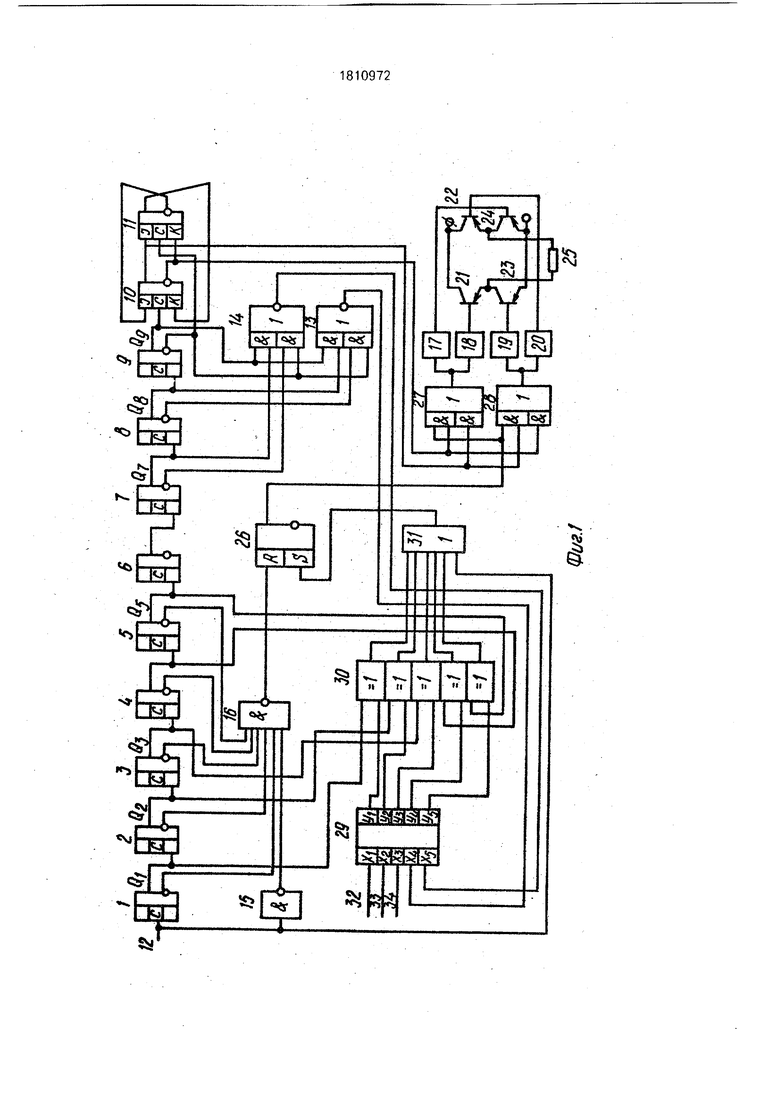

Указанная цель достигается тем, что в устройство (фиг. 1), содержащее делитель частоты на триггерах 1-11, при этом девять младших разрядов на триггерах 1-9 представляют последовательный счетчик, два старших разряда на триггерах 10 и 11 включены по схеме регистра с перекрестными связями, входную шина делителя частоты 12 для подачи тактового сигнала, первый формирователь кодов на элементах 13 и 14 типа 2-2И-ИЛИ-НЕ, входы первого формирователя соединены с выходами седьмого, восьмого и девятого разрядов делителя частоты, этот формирователь кодов реализует функции Ai(Ui3) Qa Оэ + Ов Оэ:

A2(U14) О7709 Гб бэ,(1)

элементы НЕ 15,6И-НЕ-16, усилители 17-20, выходы которых управляют работой инвертора на транзисторах 21-24, в диагональ которого включена нагрузка 25, RS-триггер 26, второй формирователь на элементах 27 и 28 типа 2И-И-ИЛИ, входы второго формирователя соединены с выходами десятого разряда делителя частоты и выходом RS-триггера

00

о ю VI ю

26, этот формирователь кодов реализует функции

U27 Q26 Ою+ Qio;

U28 Q26 -Qio+ Ою.(2) выходы второго формирователя соединены. со входами усилителей 17-20, вход первого триггера делителя частоты и вход элемента НЕ 15 соединены со входной шиной тактовой частоты 12, введено постоянное запоминающее устройство ПЗУ 29, компаратор кода 30 на пяти элементах ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент б ИЛИ 31, при этом инверсные выходы пяти младших разрядов делителя частоты и выход элемента НЕ 15 соединены со входами элемента 6И-НЕ16, выход которого соединен со входом R RS- триггера 26, коды управления по трем шинам 32-34 и выходы формирователя кодов на элементах 13 и 14 соединены соответственно с пятью входами ПЗУ 29, выходы пяти младших разрядов делителя частоты и выходы ПЗУ соединены поразрядно со входами компаратора кодов 30, пять выходов компаратора кодов и входная шина тактовой частоты 12 соединены со входами элемента 6 ИЛИ 31, выход которого соединены со входом SRS-триггера 26.

Заявителю не известно применение существенных признаков, отличающих объект от прототипа, по тому же назначению, что и в заявляемом объекте.

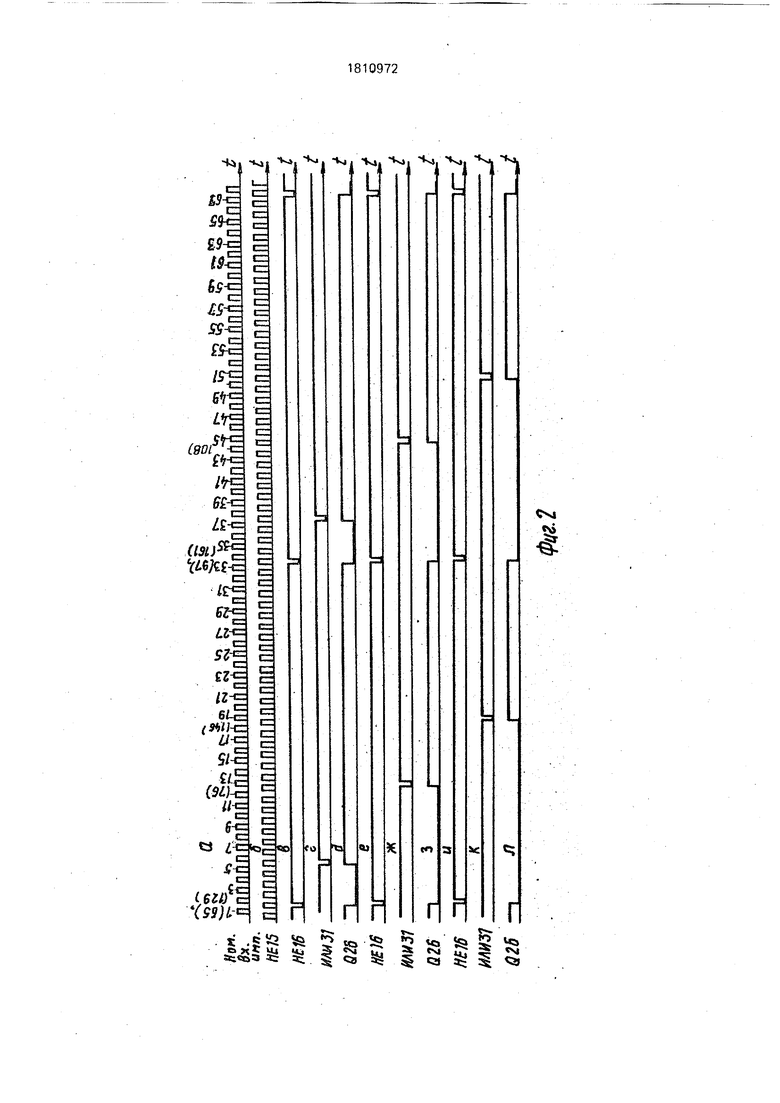

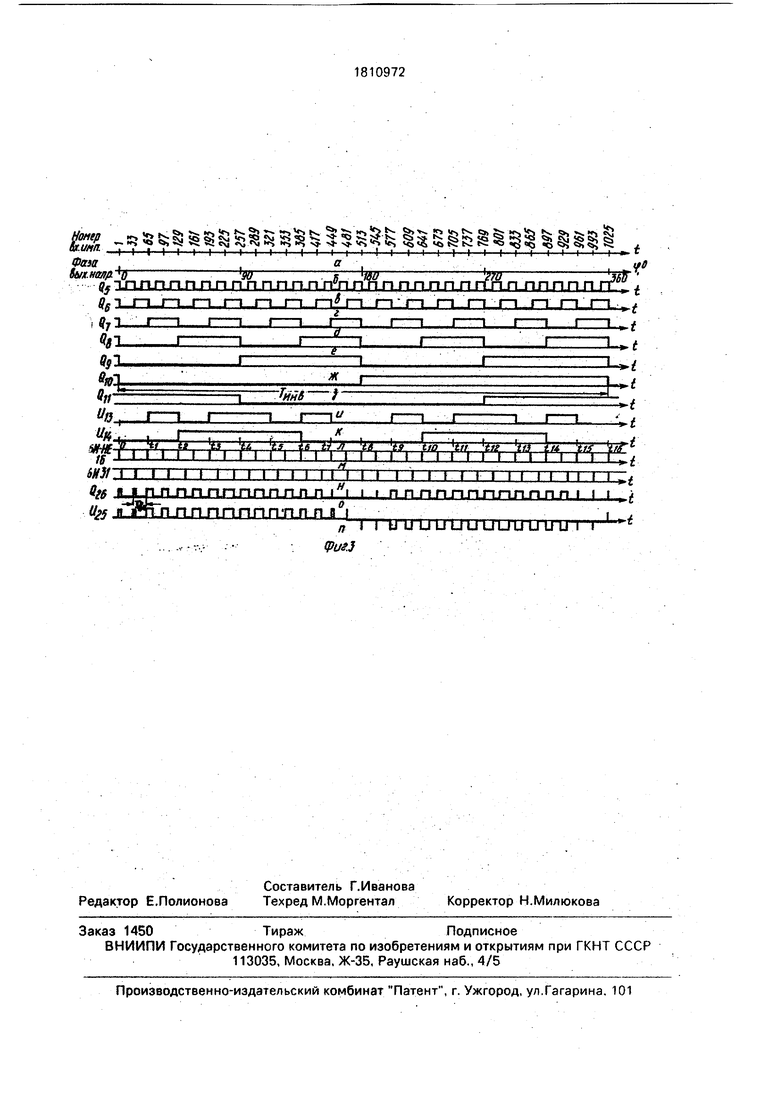

На фиг. 1 приведена принципиальная схема устройства; на фиг. 2 - эпюры напряжений, характеризующие работу схемы фиг, 1 на отдельных участках; на фиг. 3 - основные эпюры напряжений, характеризующие работу схемы фиг. 1 при формировании полного периода выходного напряжения.

Рассмотрим характеристики вход-выход основных элементов, примененных в схеме по фиг. 1,

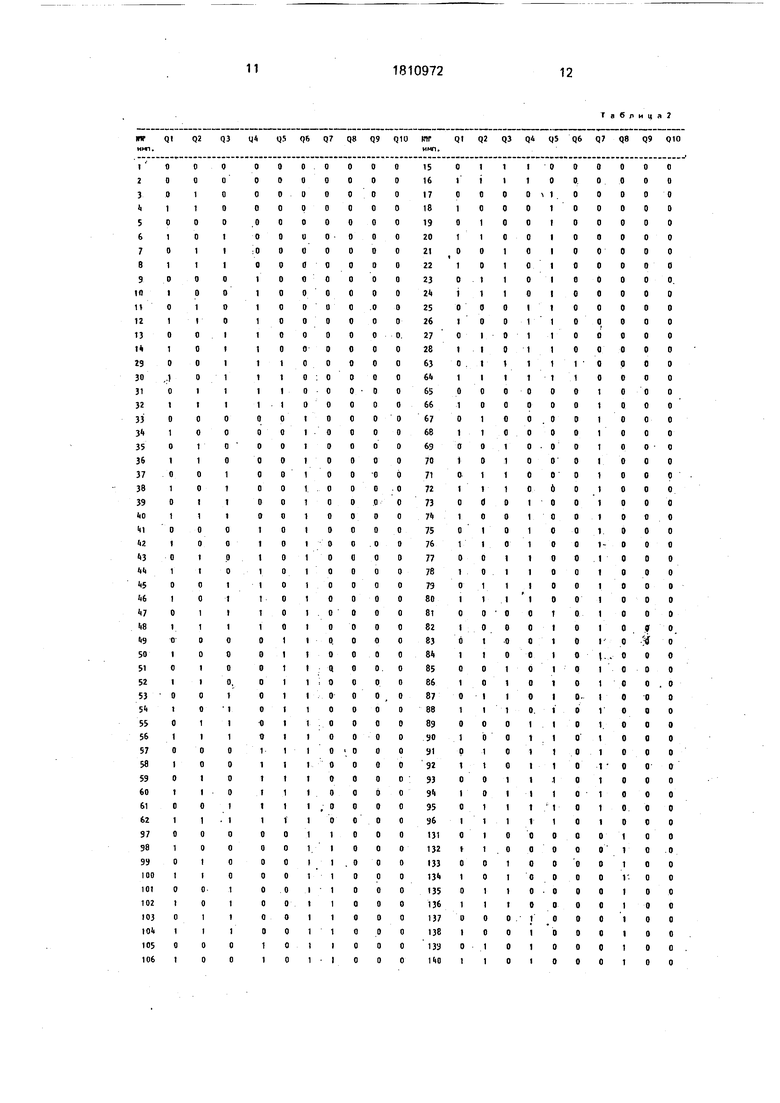

Логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ используется для сравнения кодов двух импульсных последовательностей. При равенстве потенциалов сравниваемых кодов на выходе элемента формируется О, при неравенстве потенциалов - 1, согласно таблице истинности (табл. 1).

В компараторе кода 30, выполненном на 5 элементах ИСКЛЮЧАЮЩЕЕ ИЛИ и дополненном схемой ИЛИ, при неравенстве 5 разрядов кодов на выходе элемента ИЛИ будет формироваться 1 и только при равенстве кодов всех пяти разрядов на выходе элемента ИЛИ сформируется потенциал О.

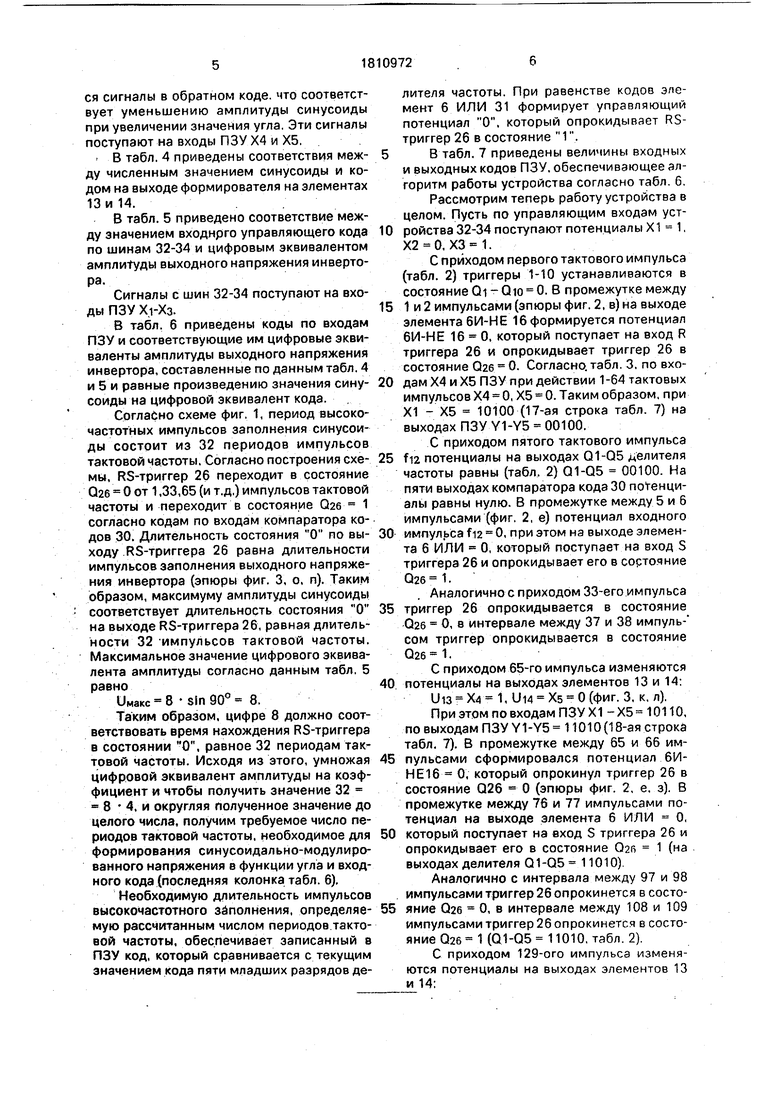

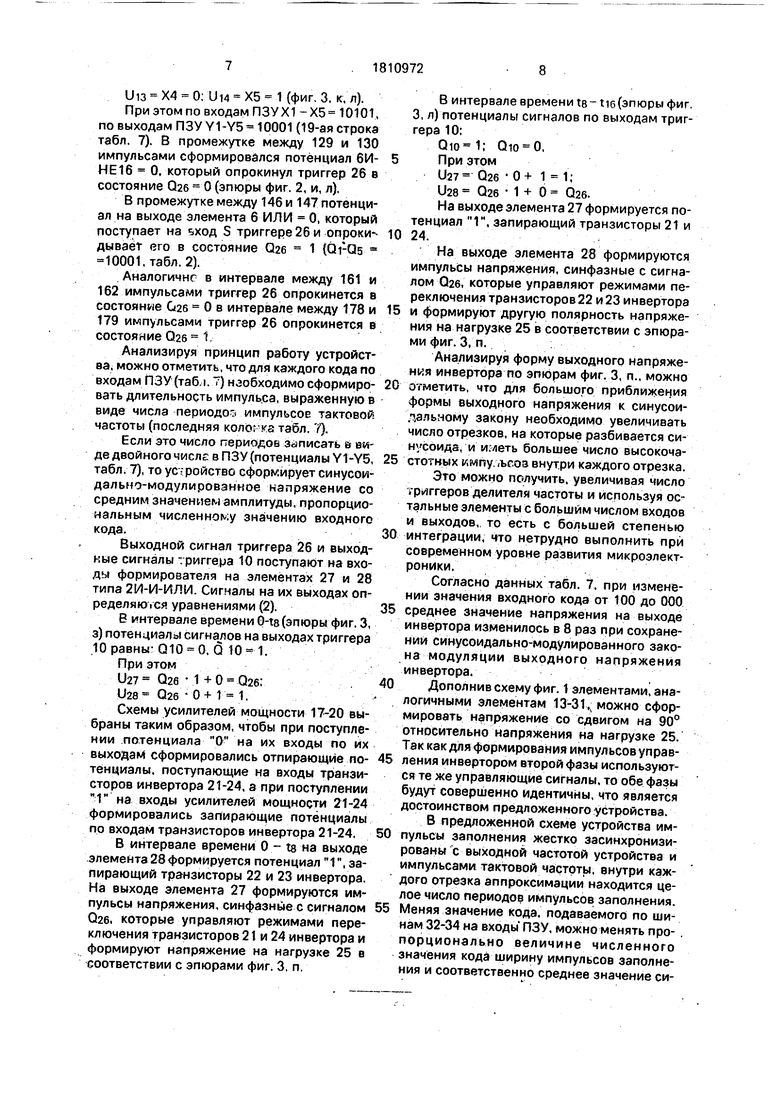

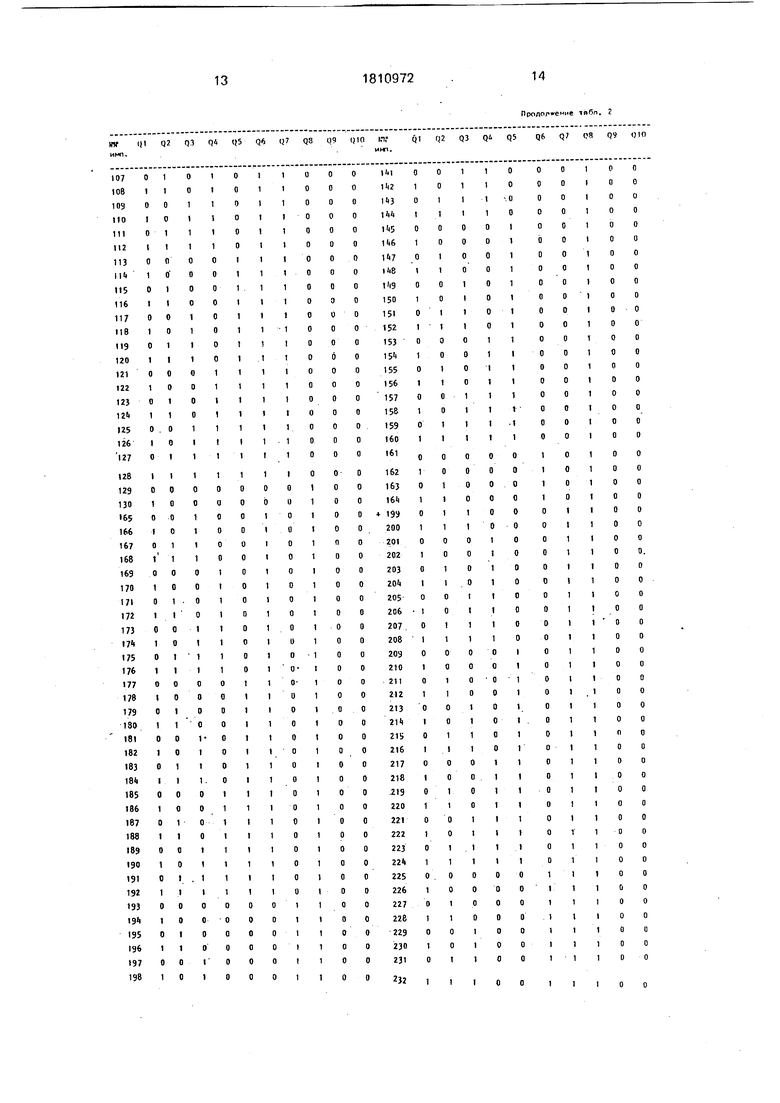

В табл. 2 приведены потенциалы на выходах некоторых элементов схемы по мере

поступления входной последовательности импульсов по шине 12.

Анализ данных табл. 2 показывает, что пять младших разрядов делителя частоты

через каждые 32 импульса тактовой частоты повторяют свое состояние.

В схеме на фиг. 1 длительность периода выходной частоты пятого разряда делителя выбрана равной длительности периода импульсов высокочастотного заполнения, а длительность периода выходной частоты десятого разряда выбрана равной длительности периода выходного напряжения инвертора. На фиг. 3 приведены эпюры напряжений на элементах схемы фиг. 1 за .период выходного напряжения. Из эпюр следует, что период выходного напряжения

инвертора равен

Т- пЮ . -г инв.-2 .Тт,

инв. I такт. 1024 Ттакт.(3) 0 - Ю24 периодам тактовой частоты, период импульсов высокочастотного заполнения равен ..-

Тв.ч. - 25Ттакт 32 Ттакт.(4)

- 32 периодам тактовой частоты. В За период выходного напряжения инвертора формируются

п-Ьаа- -.м /- (5)

1 В.Ч,

0

32

- 32 высокочастотных импульсов заполнения.

Период выходного напряжения инвертора поделен на 4 интервала: (0-90)°, (90- 180)°, (180-270)°, (270-360)° (фиг. 3, б).

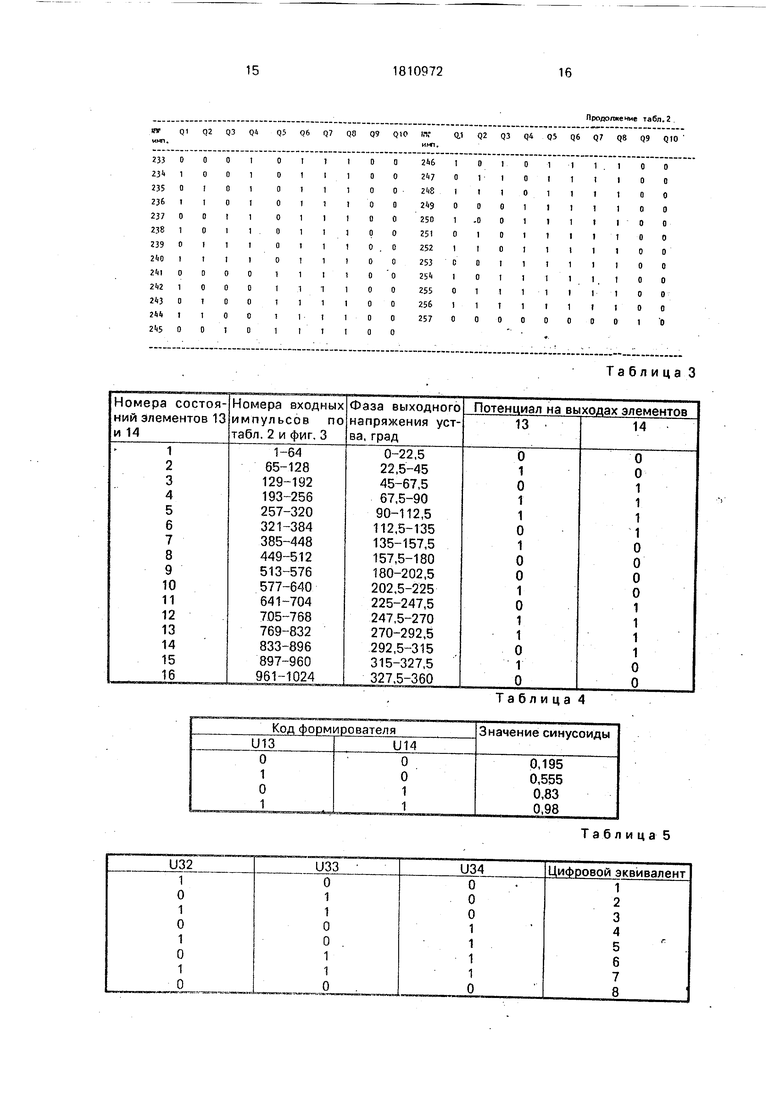

Каждый интервал поделен на отрезки, 5 вмещающие 1 /4 интервала, или 22,5°. При кусочно-линейной аппроксимации синусоиды принимаем, что внутри каждого отрезка 22,5° значение синусоиды постоянно и равно среднему значению синусоиды зя .дан- 0 ный отрезок угла. При таком подходе за 90° абсолютное значение синусоиды меняется 4 раза:

1 значение -(0-22,5)° 0,195,

2 значение - (22,5-45)° 0,555, 5 3 значение - (45-67 J5)° - 0,83,(6) 4 значение - (67,5-90)° 0,98. Формирователь кодов на элементах 13 и 14 формирует 4 значения кода в течение 90°. Эти элементы реализуют функции (1), 0 значения которых в зависимости от текущего значения угла приведены на фиг. 3,-к, л. В табл, 3 приведены изменения потенциалов на выходах элементов 13 и 14 за период выходного напряжения устройства, 5 Анализируя данные табл. 3. можно отметить, что в интервалах в прямом коде, что соответствует нарастанию амплитуды синусоиды при увеличении значения угла, а в интервалах (90-180)°, (270-360)° формируются сигналы в обратном коде, что соответствует уменьшению амплитуды синусоиды при увеличении значения угла. Эти сигналы поступают на входы ПЗУ Х4 и Х5.

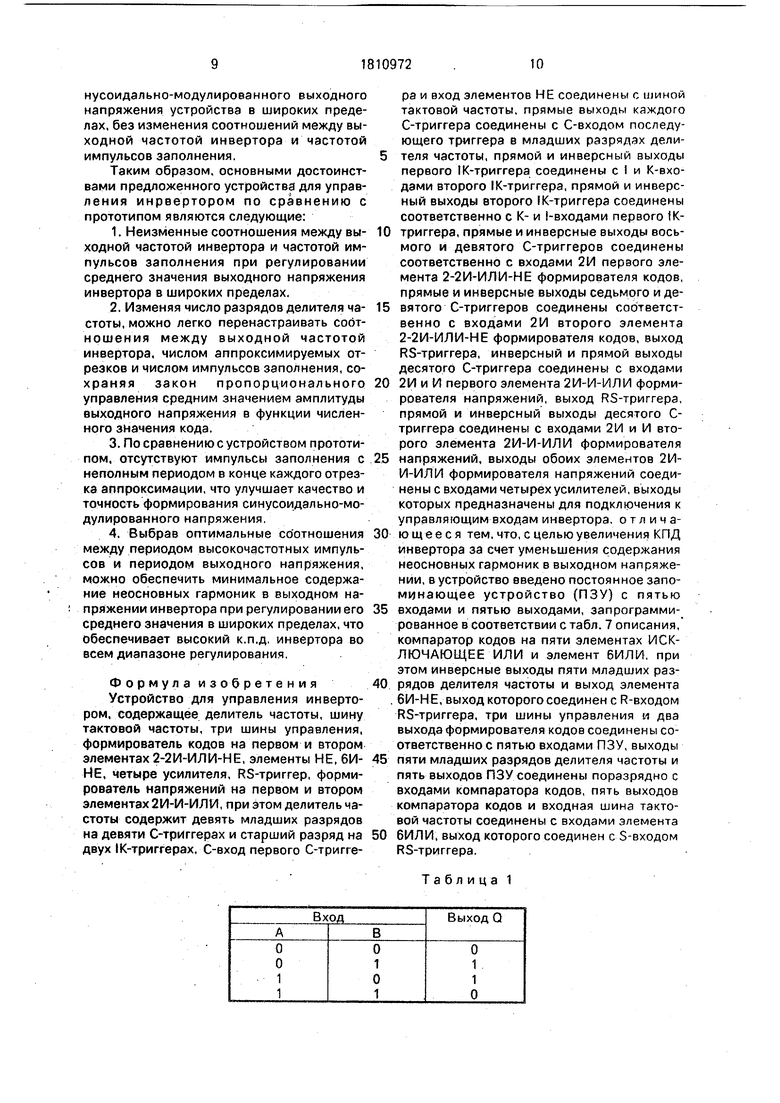

В табл. 4 приведены соответствия между численным значением синусоиды и кодом на выходе формирователя на элементах 13 и 14.

В табл. 5 приведено соответствие между значением входнрго управляющего кода по шинам 32-34 и цифровым эквивалентом амплитуды выходного напряжения инвертора.

Сигналы с шин 32-34 поступают на входы ПЗУ Xi-Хз.

В табл. 6 приведены коды по входам ПЗУ и соответствующие им цифровые эквиваленты амплитуды выходного напряжения инвертора, составленные по данным табл. 4 и 5 и равные произведению значения синусоиды на цифровой эквивалент кода.

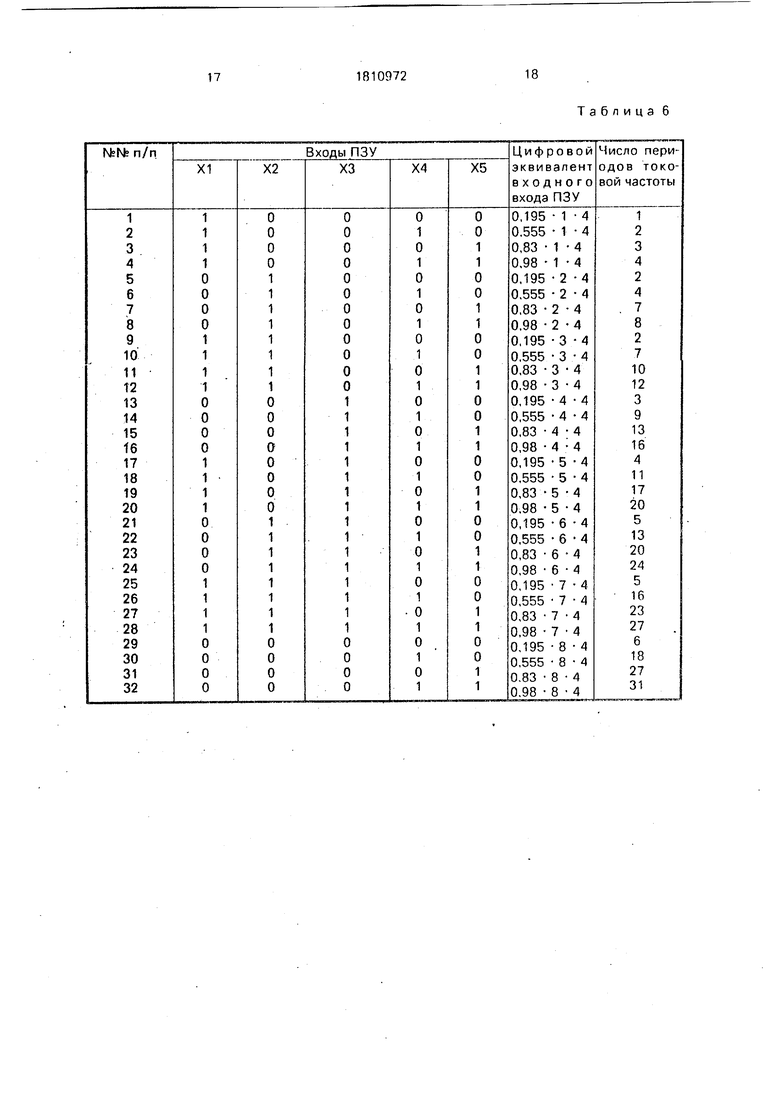

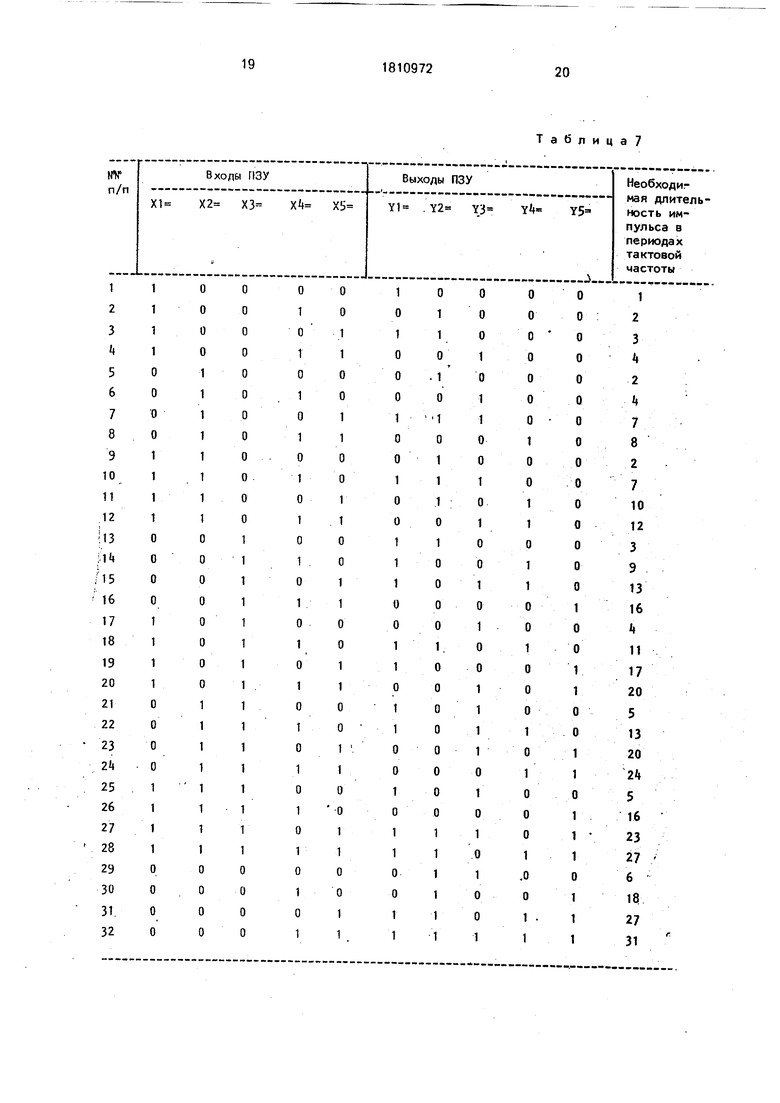

Согласно схеме фиг. 1, период высокочастотных импульсов заполнения синусоиды состоит из 32 периодов импульсов тактовой частоты. Согласно построения схемы, RS-триггер 26 переходит в состояние Q26 0 от 1,33,65 (и т.д.) импульсов тактовой частоты и переходит в состояние 026 1 согласно кодам по входам компаратора кодов 30. Длительность состояния О по выходу RS-триггера 26 равна длительности импульсов заполнения выходного напряжения инвертора (эпюры фиг. 3, о, п). Таким образом, максимуму амплитуды синусоиды соответствует длительность состояния О на выходе RS-триггера 26, равная длительности 32 -импульсов тактовой частоты. Максимальное значение цифрового эквивалента амплитуды согласно данным табл. 5 равно

Умакс 8 sin 90° 8.

Таким образом, цифре 8 должно соответствовать время нахождения RS-триггера в состоянии О, равное 32 периодам тактовой частоты. Исходя из этого, умножая цифровой эквивалент амплитуды на коэффициент и чтобы получить значение 32 8 4, и округляя полученное значение до целого числа, получим требуемое число периодов тактовой частоты, необходимое для формирования синусоидально-модулированного напряжения в функции угла и входного кода (последняя колонка табл. 6).

Необходимую длительность импульсов высокочастотного заполнения, определяемую рассчитанным числом периодов тактовой частоты, обеспечивает записанный в ПЗУ код, который сравнивается с текущим значением кода пяти младших разрядов делителя частоты. При равенстве кодов элемент 6 ИЛИ 31 формирует управляющий потенциал О, который опрокидывает RS- триггер 26 в состояние 1. 5В табл. 7 приведены величины входных и выходных кодов ПЗУ, обеспечивающее алгоритм работы устройства согласно табл. G. Рассмотрим теперь работу устройства в целом. Пусть по управляющим входам уст0 ройства 32-34 поступают потенциалы Х1 1, Х2 0, .

С приходом первого тактового импульса (табл. 2) триггеры 1-10 устанавливаются в состояние СИ-Qю 0. В промежутке между

5 1 и 2 импульсами (эпюры фиг. 2, в) на выходе элемента 6И-НЕ Сформируется потенциал 6И-НЕ 16 0, который поступает на вход R триггера 26 и опрокидывает триггер 26 в состояние Qze 0. Согласно, табл. 3, по вхо0 дамХ4иХ5ПЗУ при действии 1-64 тактовых импульсов Х4 О, Х5 0. Таким образом, при XI - Х5 10100 (17-ая строка табл. 7) на выходах ПЗУ Y1-Y5 - 00100.

С приходом пятого тактового импульса

5 fiz потенциалы на выходах Q1-Q5 .целителя частоты равны (табл. 2) Q1-Q5 00100. На пяти выходах компаратора кода 30 потенциалы равны нулю. В промежутке между 5 и 6 импульсами (фиг. 2, е) потенциал входного

0 импульса fiz 0, при этом на выходе элемента 6 ИЛИ 0, который поступает на вход S триггера 26 и опрокидывает его в состояние .

Аналогично с приходом 33-его импульса

5 триггер 26 опрокидывается в состояние Q26 0, в интервале между 37 и 38 импуль- сом триггер опрокидывается в состояние

.

С приходом 65-го импульса изменяются 0 потенциалы на выходах элементов 13 и 14:

и13 ,и14 Х5 0(фиг. 3, к. л).

При этом по входам ПЗУ Х1 - Х5 10110, по выходам ПЗУ Y1-Y5 11010 (18-ая строки табл, 7). В промежутке между 65 и 66 им- 5 пульсами сформировался потенциал 6И- НЕ16 0, который опрокинул триггер 26 в состояние Q26 0 (эпюры фиг. 2, е, з). В промежутке между 76 и 77 импульсами потенциал на выходе элемента б ИЛИ О, 0 который поступает на вход S триггера 26 и опрокидывает его в состояние Q2fi 1 (на выходах делителя Q1-Q5 11010).

Аналогично с интервала между 97 и 98 импульсами триггер 26 опрокинется в состо- 5 яние Q26 0, в интервале между 108 и 109 импульсами триггер 26 опрокинется в состояние 026 1 (Q1-Q5 11010, табл. 2).

С приходом 129-ого импульса изменяются потенциалы на выходах элементов 13 и 14:

U13 Х4 0: U14 Х5 1 (фиг. 3, к. л).

При этом по входам ПЗУ Х1-Х5 10101, по выходам ПЗУ Y1-Y5 10001 (19-ая строка табл. 7). В промежутке между 129 и 130 импульсами сформировался потенциал 6И- НЕ16 0, который опрокинул триггер 26 в состояние 026 0 (эпюры фиг. 2, и, л).

В промежутке между 146 и 147 потенциал на выходе элемента 6 ИЛИ 0, который поступает на ход S триггере 26 и опрокидывает его в состояние Q26 1 {Qi:Q5 10001. табл. 2).

Аналогично в интервале между 161 и 162 импульсами триггер 26 опрокинется в состояние G26 0 в интервале между 178 и 179 импульсами триггер 26 опрокинется в состояние 026 1.

Анализируя принцип работу устройства, можно отметить, что для каждого кода по входам ПЗУ (табл. 7) нэобходимо сформировать длительность импульса, выраженную в виде числа периодов импульсов тактовой частоты (последняя колонка табл. 7).

Если это число периодов записать & виде двойного ЧИСЛЕ в ПЗУ (потенциалы Y1-Y5, табл. 7), то устройство сформирует синусов дально-модулировзнное напряжение со средним значением амплитуды, пропорциональным численному значению входного кода.

Выходной сигнал триггера 26 и выходные сигналы триггера 10 поступают на входы формирователя на элементах 27 и 28 типа 2И-И-ИЛИ. Сигналы на их выходах определяются уравнениями (2).

В интервале времени 0-te (эпюры фиг. 3, з) потенциалы сигналов на выходах триггера 10 равны-Q10 0. Q 10 - 1.

При этом

U27 Q26 1 +0 Q26:

U28 026 0 + 1 1.

Схемы усилителей мощности 17-20 выбраны таким образом, чтобы при поступлении потенциала О на их входы по их выходам сформировались отпирающие потенциалы, поступающие на входы транзисторов инвертора 21-24, а при поступлении Г на входы усилителей мощности 21-24 формировались запирающие потенциалы по входам транзисторов инвертора 21-24.

В интервале времени 0 te на выходе .элемента 28 формируется потенциал 1, запирающий транзисторы 22 и 23 инвертора. На выходе элемента 27 формируются импульсы напряжения, синфазные с сигналом Q26, которые управляют режимами переключения транзисторов 21 и 24 инвертора и формируют напряжение на нагрузке 25 в соответствии с эпюрами фиг. 3, п.

В интервале времени te-ti6 (эпюры фиг. 3, л) потенциалы сигналов по выходам триггера 10:

Ою 1; Ою 0, При этом

U27 Q26 -0+ 1 1;

U28 Q26 1 + 0 Q26.

На выходе элемента 27 формируется потенциал Г, запирающий транзисторы 21 и

24.

На выходе элемента 28 формируются импульсы напряжения, синфазные с сигналом Q26, которые управляют режимами переключения транзисторов 22 и 23 инвертора

и формируют другую полярность напряжения на нагрузке 25 в соответствии с эпюрами фиг. 3, п.:.-..

Анализируя форму выходного напряжения инвертора по эпюрам фиг. 3, п., можно

отметить, что для большого приближения формы выходного напряжения к синусоидальному закону необходимо увеличивать число отрезков, на которые разбивается синусоида, и и.меть большее число высокочастотных кмпу.ъсоз внутри каждого отрезка. Это можно получить, увеличивая число триггеров делителя частоты и используя остальные элементы с большим числом входов и выходов,, то есть с большей степенью

интеграции, что нетрудно выполнить при современном уровне развития микроэлектроники..

Согласно данных табл. 7. при изменении значения входного кода от 100 до 000

среднее значение напряжения на выходе инвертора изменилось в 8 раз при сохранений синусоидально-модулированного закона модуляции выходного напряжения инвертора.

Дополнив схему фиг. 1 элементами аналогичными элементам 13-31Л можно сформировать напряжение со сдвигом на 90° относительно напряжения на нагрузке 25. Так как для формирования импульсов управления инвертором второй фазы используются те же управляющие сигналы, то обе фазы будут совершенно идентичны, что является достоинством предложенного устройства. В предложенной схеме устройства импульсы заполнения жестко засинхронизи- рованы с выходной частотой устройства и импульсами тактовой частоты, внутри каждого отрезка аппроксимации находится целое число периодов импульсов заполнения.

Меняя значение кода, подаваемого по шинам 32-34 на входы ПЗУ, можно менять про- порционально величине численного значения кода ширину импульсов заполнения и соответственно среднее значение синусоидально-модулированного выходного напряжения устройства в широких пределах, без изменения соотношений между выходной частотой инвертора и частотой импульсов заполнения.

Таким образом, основными достоинствами предложенного устройства для управления инрвертором по сравнению с прототипом являются следующие:

1. Неизменные соотношения между выходной частотой инвертора и частотой импульсов заполнения при регулировании среднего значения выходного напряжения инвертора в широких пределах.

2. Изменяя число разрядов делителя частоты, можно легко перенастраивать соотношения между выходной частотой инвертора, числом аппроксимируемых отрезков и числом импульсов заполнения, сохраняя закон пропорционального управления средним значением амплитуды выходного напряжения в функции численного значения кода.

3. По сравнению с устройством прототипом, отсутствуют импульсы заполнения с неполным периодом в конце каждого отрезка аппроксимации, что улучшает качество и точность формирования синусоидально-модулированного напряжения.

4. Выбрав оптимальные соотношения между периодом высокочастотных импульсов и периодом выходного напряжения, можно обеспечить минимальное содержание неосновных гармоник в выходном напряжении инвертора при регулировании его среднего значения в широких пределах, что обеспечивает высокий к.п.д. инвертора во всем диапазоне регулирования.

Формула изобретения Устройство для управления инвертором, содержащее делитель частоты, шину тактовой частоты, три шины управления, формирователь кодов на первом и втором элементах 2-2И-ИЛИ-НЕ, элементы НЕ, 6И- НЕ, четыре усилителя, RS-триггер, формирователь напряжений на первом и втором элементах 2И-И-ИЛИ, при этом делитель частоты содержит девять младших разрядов на девяти С-тритгерах и старший разряд на двух IK-триггерах, С-вход первого С-триггера и вход элементов НЕ соединены с шиной тактовой частоты, прямые выходы каждого С-триггера соединены с ОБХОДОМ последующего триггера в младших разрядах делителя частоты, прямой и инверсный выходы первого IK-триггера соединены с I и К-вхо- дэми второго IK-триггера, прямой и инверсный выходы второго IK-триггера соединены соответственно с К- и 1-входами первого Жтриггера, прямые и инверсные выходы восьмого и девятого С-триггеров соединены соответственно с входами 2И первого элемента 2-2И-ИЛИ-НЕ формирователя кодов, прямые и инверсные выходы седьмого и девятого С-триггеров соединены соответственно с входами 2И второго элемента 2-2И-ИЛИ-НЕ формирователя кодов, выход RS-триггера, инверсный и прямой выходы десятого С-триггера соединены с входами

2И и И первого элемента 2И-И-ИЛИ формирователя напряжений, выход RS-триггера, прямой и инверсный выходы десятого С- триггера соединены с входами 2И и И второго элемента 2И-И-ИЛИ формирователя

напряжений, выходы обоих элементов 2И- И-ИЛИ формирователя напряжений соединены с входами четырех усилителей, выходы которых предназначены для подключения к управляющим входам инвертора, отличающ ее с я тем, что, с целью увеличения КПД инвертора за счет уменьшения содержания неосновных гармоник в выходном напряжении, в устройство введено постоянное запоминающее устройство (ПЗУ) с пятью

входами и пятью выходами, запрограммированное в соответствии с табл. 7 описания, компаратор кодов на пяти элементах ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент 6ИЛИ, при этом инверсные выходы пяти младших разрядов делителя частоты и выход элемента . 6И-НЕ, выход которого соединен с R-входом RS-триггера, три шины управления и два выхода формирователя кодов соединены соответственно с пятью входами ПЗУ, выходы

пяти младших разрядов делителя частоты и пять выходов ПЗУ соединены поразрядно с входами компаратора кодов, пять выходов компаратора кодов и входная шина тактовой частоты соединены с входами элемента

6ИЛИ, выход которого соединен с S-входом RS-триггера.

Таблица 1

Таблица

Продолжение табл. 2

Таблица 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления инвертором | 1987 |

|

SU1617584A1 |

| Широтно-импульсный модулятор | 1989 |

|

SU1677857A1 |

| Устройство для настройки и поверки импульсной электроразведочной аппаратуры | 1984 |

|

SU1241177A1 |

| Устройство для управления многоканальным электроприводом тренажера | 1984 |

|

SU1180846A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1984 |

|

SU1233283A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Цифровой генератор функций | 1986 |

|

SU1388842A1 |

| Многофазный импульсный стабилизатор | 1984 |

|

SU1196830A1 |

| Электропривод постоянного тока | 1990 |

|

SU1741247A1 |

| Устройство для управления электродвигателем переменного тока | 1984 |

|

SU1457141A1 |

В устройстве для управления инвертором в выходном направлении инвертора ив каждом отрезке аппроксимации содержится целое число периодов импульсов заполнения, при этом длительность импульсов заполнения формируется равной произведению численного значения входного кода и ступенчато аппроксимированного значения синуса угла. Операции умножения и формирования осуществляются с использованием ПЗУ и компаратора кода. 3 ил., 7 табл.

Таблица 4

Таблица 5

Таблица 6

Таблица

| Шило В.Л | |||

| Популярные цифровые микросхемы | |||

| Справочник, Челябинск, Металлургия, 1989 | |||

| Микросхемы и их применение | |||

| Справочное пособие - М.: Радио и связь, 1983. |

Авторы

Даты

1993-04-23—Публикация

1989-08-16—Подача