Изобретение отнфсится к вычислительной технике, особенно к специгш зированным вычислителям, и предназн чено для вычисления коэффициентов р да Фурье вида: AV - ITS Х(И)61П0, rr-Q „ а ки . ViT.J.. Наиболее близким по технической сущности к предлагаемому является устройство, содержащее три сумматор вычитателя, два сдвиговых регистра, регистр, блок элементов И и блок эл ментов ИЛИ, генератор тактовых импульсов, два сдвигателя, два тригге ра, два элемента задержки, три ёдемента ИЛИ и три элемента И, соедине ные определенным образом ij, Это устройство предназначено для вычисления значений (Аункции вида; X-K RgCOSe i V--K Ro5in0, где RQ - модуль начального векто (начальный код в первом сумматоре-вычитатале); k,- - коэффициент увеличения модуля-вектора после (-го шага итерации; R выбирается из условия точности получе- ния соотношения (3), но негодится для непосредственного определения функций (1) и. (2) . Целью изобретения является расширение функциональных возйожностей устройства: обеспечение помимо вычисления значений синусно-косинусных функций возможности вычисления коэффициентов рядаФурье. Это достигается тем, что в устройство, содержащее генератор тактовых импульсов, регистр, три сумматора-вычитателя, сумматор, блоки элементов И, ИЛИ, элементы задержки, сдвигатели и два регистра сдвига, причем выходы первого регистра подключены к соответствующим входам первого и второго сдвигателей и к входу третьего сумматора-вычитателя, младшие входы которого подключены к соответствующим выходам первого регистра сдвига через первый блок элементов ИЛИ, нулевой выход знакового разря- да третьего сумматора-вычитателя подключен к суммирующему входу третьего сумматора-вычитателя, суммиоующему входу первого сумматора-вычитателя и вычитающему входу второго сумматора вычитателя, выходы которого подключены к соответствующим входам первого -регистра, выходы которого подключены к соответствующим входам первого сдвигателя, выходы первого сумматора-вычитателя подключены к соответствукхцим входам второго сдвгателя, выходы которого подключены к соответствующим входам второго сумматора-вычитателя, суммирующий вход которого подключен к вычитающему входу и единичному выходу знакового разряда третьего -сумматоравычитател и вычитающему входу первого сумматора-вычитателя, первый вход установки в ноль которого подключен к выходу первого элемента И, первый вход которого подключен к сташему выходу первого регистра сдвига и к первому входу второго элемента ИЛИ, выход которого подключен к первым управляющим входам первого и второго сдвигателей, а второй вход - ко второму выходу первого регистра сдвига, сдвигающий вход которого подключен к выходу второго элемента згщержки, вход которого объединен со вторым входом первого элемента И, управляющим входом третьего суг матора вычитателя, первым входом второго элмента И и четвертым выходом второго регистра сдвига, третий выход которого подключен к управляющему входу первого сумматора-вычитателя, второй выход подключен к управляющему входу второго сумматора-вычитателя, а первый выход - к управляющему входу регистра, вход установки в ноль которого подключен к входам установки в ноль второго сумматора-вычитателя, второго регистра сдвига и первого регистра сдвига, последний выход которого подключен к управляющим входам первого и второго сдвигателей, вторые управляющие входы которого объединены с инЛормационным входом .. третьего разряда третьего сумматоравычитателя, введены два сумматора,две кнопки,два ключа,счетчик, преобразователь аналог-код и буферный регистр причем выходы третьего сумматора подключены ко входам первого блока элементов И, а управляющий вход подключен к управлякщему входу буферного , выходу ВТОРОГО элемента И, первому входу первого элемента ИЛИ и входу первого элемента задержки, выхвд которого подключен к управляющему входу второго блока элементов И, выходы которого подключены к первой группе входов второго блока элементов ИЛИ, вторая группа входов которого подключена к выходам первого сдвигателя, а выходы ко входам первого сумматора-вычигЕателя, выход второй кнопки подключен к входам установки в ноль второго регистра

сдвига, счетчика, первого сумматоравычитателя, третьего сум-матора, преобразователя аналог-код, буферного регистра , второго и первого cyiviMaTOров и первому входу третьего элемента ИЛИ,информационные входы второго и первого сумматоров подключены к соответствующим информационным выходам второго и первого сумматороввычитателей соответственно, а управляющие входы, подключены к выходу третьего элемента И, первый вход которого подключен к третьему выходу второго регистра сдвига, второй вход подключен ко втором входу второго элемента И, выход которого подключен к первому входу первого элемента ИЛИ выход которо-го подключен к выходу установки единицы первого регистра сдвига, а второй вход - подключен к выходу первой кнопки, входу установки единицы второго регистра сдвига, второму входу четвертого элемента ИЛИ, единичному входу триггера, единичный выход которого подключен I к первому входу четвертого элемЪнта И, а нулевой вход - к выходу третьего элемента ИЛИ, второй вход которого пoдкJтачeн к выходу первого ключа, первый и второй входы которого подключены к первому и второму выходам счетчика соответственно, вход которого подключен к выходу младше,го разряда первого регистра сдвига, выход генератора импульсов подключен ко BTopof входу четвертого элемента И, выход которого подключен к сдвгающему входу второго регистра сдвига, третий выход которого подключен к первому входу четвертого элемента ИЛИ, выход которого подключен к у правлягсщему входу преобразователя аналог-код, выход которого через второй ключ подключен к информационным входам буферного регистра, выходы которого подключены к информационным входам второго блока элементов И.

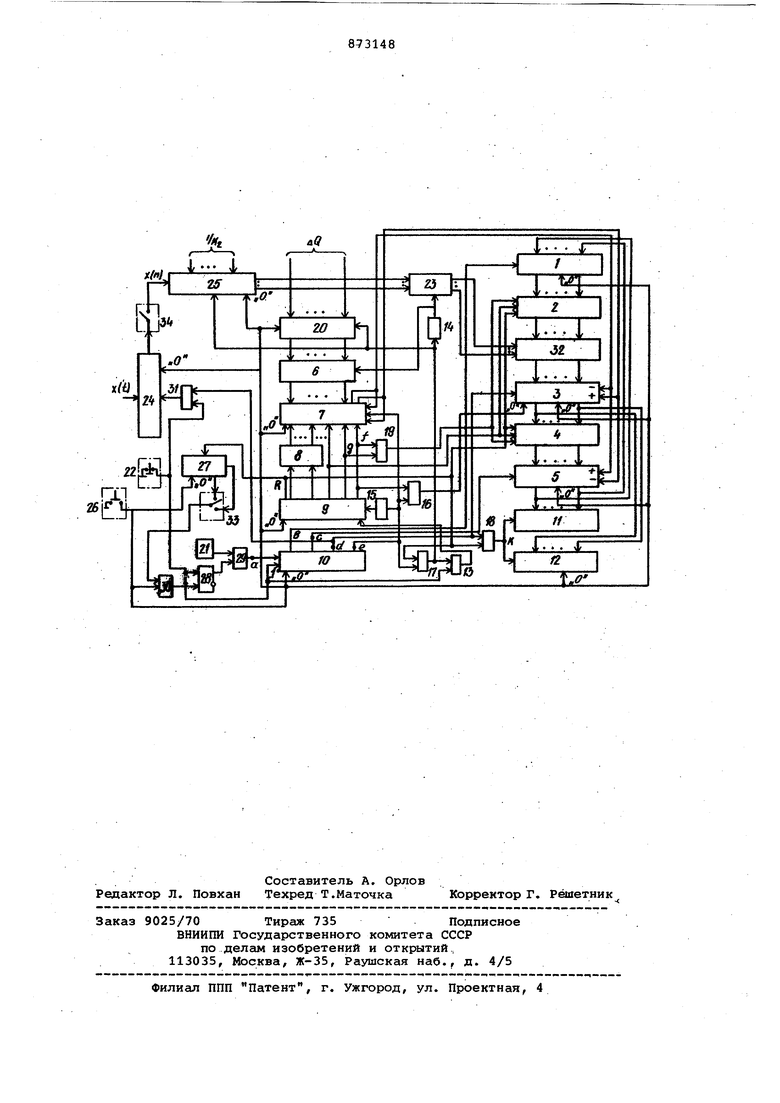

На чертеже изображена структурная схема цифрового гармонического анализатора.

Схема цифрового гармонического анализатора содержит регистр 1, перв сдвигатель 2, первый сумматор-вычитатель 3, второй сдвигатель 4, второ сумматор-вычитатель 5, первый блок б элементов И, третий сумматор-вычитатель 7, первый блок 8 элементов ИЛИ, первый регистр 9 сдвига, второй регистр 10 сдвига, второй сумматор 11, первый сумматор 12, первый элемент ИЛИ 13, первый элемент 14 задержки, второй элемент 15 задержки, первый элемент И 16, второй элемент И 17, третий элемент И 18, второй электнт ИЛИ 19,третий сумматор 20, генератор 21 тактовых импульсов, первую кнопку 22, второй блок 23 элементов 1, преобразователь 24 аналогкод, буферный регистр 25, вторую кнопку 26, счетчик 27, триггер 28, четвертый элемент И 29, третий элемент ИЛИ 30, четвертый элемент ИЛИ 31, второй блок 32 элементов ИЛИ, первый .ключ 33, второй ключ 34. Анализатор работает следугацим образом. . При нажатии кнопки 26 устройство устанавливается в нулевое начальное состояние. При этом в нулевое поло - жение устанавливаются преобразовател 24, буферный регистр 25, счетчик 27 через третий элемент ИЛИ 30, триггер 28, третий сумматор 20, третий сумматор-вычитатель 7, первый регистр сдвига, второй регистр 10 сдвига, регистр 1,первый сумматор-вычитател 3, второй сумматор-вычитатель 5, вто рой сумматор 11 и первый сумматор 1 Генератор 21 тактовых импульсов пос тоянно вырабатывает последовательно тактовых импульсов, которая поступает на второй вход четвертого элемента И 29. На установочные входы третьего сумматора 20 подается код приращения Л© аргумента функций синуса и косинуса. Причем Л0 опредё ляется из условия Д0-.-, где k - . номер гармоники; N - количество точек дискретизации сигнала x(t); N и k выбираются априорно. На информационный вход преобразователя 24 подключен входной сигнал x(t). Пои нажатии кнопки 22 триггер 28 переводит ся в единичное состояние. Сигнал, возникающий на единичном выходе триг гера 28 открывает элемент И 29, на ег выходе возникают импульсы тактовой частоты. Этот же сигнал с выхода кнопки 22 через четвертый элемент ИЛИ 31 запускает преобразователь 24 в котором формируется коп первого разряда кодового эквивалента дискрет ной величины х{п) входного сигнала x(t) при . В то же время сигнал с выхода кнопки 22 устанавливает через первый элемент ИЛИ 13.в.регистре 9 сдвига код ft 0,10.,.Q (разрядность регистра 9 равна R, выбирается из условия точности задания угла 0 ). Нз этих же соображений выбираются разрядности сумматора 20 третьего сумматора-вычитателя 7, регистра 1, первого и второго сумматоров-вычитателей 3 и 5. При этом так же устанавливается код 10000 в регистре 10. На этом заканчивается начальный шаг вычислений. При вычислении коэффициентов ряда Фурье ключ 34.3aMKHVT, а ключ 33 обеспечивает замыкание цепи второй выход счетчик 26 - второй вход третьего элемента 30. . Следующий после начального шага вычислений подготовительный этап предназначен для Формирования нулевого кодового эквивалента входной величины х(п) при п 0. Для рассмотрения этого шага достаточно указать что каждый сигнал, поступающий на вход регистра сдвига 10, осуществляет изменение кода, который хранится в нем. Начальный код 10000, затем 01000, далее 00100, 00010, 00001, потом опять 10000, ОЮОб, и т.д. Каждый раз код 00010 формирует на третьем выходе регистра 10 сигнал, который поступает через элемент ИГЧ 31 на вход преобразователя 24, который формирует поразрядно код х(о). Каждый раз код 00001 формирует на червертом выходе регистра 10 сигнал, который сдвигает код в регистре 9. Начальное состояние }3 0,100...О, затем Р,- 0,010.. .0,,.,. ,PR 0,0. .01. Изменения состояний регистров 9 и 10 во время выполнения подготовительного шага состояния регистра 1, сумматоров-вычитателей 3,5,7 и сумматоров 11, 12, 20 не меняются, так как в них суммируются (вычитаются) нулевые колы. С получением комбинации f5) 0,0...01 на регистре 9 и 00001, на регистре 10 заканчивается подготовительный шаг вычислений. При этом сигнал с выхода элемента 17 устанавливает в .регистре 10 код /3, 0,10.. О через элемент 13 осуществляет операцию суммирования в сумматоре 20 (в сумматоре находился нулевой код, а f, , теперь код Уд переписывает код X(О) из преобразователя 24 в регистр 25. Этот же-сигнал, задержанный на элементе задержки 14, устанавливает через блок 6 код &о в сумматор-вьиитатель 7 и через блоки 23 и 32 код Х(0) в сумматор-вычитатель 3. Первый шаг итерации осуществляется следующим образом. В регистр 10 записывается код 01000. В то же время на первом выходе регистра 10 появляется сигнал соответствующий единичному уровню, который осуществляет подачу кода из второго сумматора-вычитателя 5 в регистр 1. Осуществляется микрооперация If 5 ,т.е. содержи иому регистра 1 присваивается значение сумматора-вычитателя 5. Далее тактовый импульс осуществляет сдвиг информации в регистре 10, где оказывается код 00100, который формирует сигнал единичного уровня на втором выходе регистра 10. Этот сигнал поступает на вход сумматора-вычитателя 5 , осуществляя тем самым микрооперацию 5 . Знак кода, переписываемого из сумматора-вычитателя 3 в сумматор-вычитатель 5, определяется знаковым разрядом сумматоравычитателя 7. После прихода следующего тактового импульса в регистре 1 устанавливается код 00010 и возбуждается тре-. тий выход. Сигнал с третьего выхода егистра 10 осуществляет суммирование предыдущего числа в сумматоревычитателе 3с кодом, хранящимся- в регистре 1, т.е. выполняется микрооперация . Очередной тактовый импульс устанавливает в регистре 10 код 00001. Сигнал с единичного уровня с четвертого выхода осуществляет суммирование (с учетом знаков) 0о и , содержимого регистра 9 С т.е. Р 0,10... О ). Этот же сигнал, проходя через открытый элемент И 16, устанавливает сумматор-вычитатель 3 в нулевое состояние (). На этом фактически заканчивается пятый (последний) такт первого шага итеративного процесса. Каждый шаг (начиная с первого шага итерации) выполняется за пять тактов. Для удобства в каждом шаге выделяется нулевой, первый, второй, третий и четвертый импульсы. Это соответствует следующим кодам в регистре 10 - 10000, 01000, 00100, 00010, 00001, которые циклически повторяются. Регистр 10 представляет собой кольцевой регистр сдвига.

Второй шаг начинается с приходом нового импульса, который устанавливает в регистре 10 код 10000. В то же время сигнал с выхода элемен а задержки 15 осуществляет в регистре 9 микрооперацию (т.е. устанавливает код Р2 0,01...о;,, код 01000 в регистре 10 осуществляет передачу со держимого второго сумматора-вычитателя 5 в регистр 1 ( 1 5 . Далее код 00100 осуществляет суммирование кодов, храня1зихся в сумматорах вычитателях 5 и 3, т.е. выполняется микрооперация . Следукидий импульс обеспечивает выполнение микроопераций 3 t l7-2. Очередной импульс обеспечивает выполнение алгебраического суммирования содержимого сумматора-вычитателя 7 с кодом, хранящимся в регистре 9, т.е. Третий и последующие шаги итерации аналогичны второму. При этом на каждом R-OM шаге циклически повторяются следующие микрооперации: 9 , . - первый импульс; 5 3 2 второй импульс f третий импульс; четвертый импульс.

По окончании R-ro шага итерации в регистре 9 формируется код 0,00..., а в регистре 10-0001, что соответствует появлению единичных сигналов на и 4-ом выходах регистров 9 и 10 роответственно, которые открывают элемент И-17. С выхода И 17 сигнал разрешает работу элемента ИЛИ 13. Весь процесс повторяется сначала. При этом необходимо учесть то, что в третий сумматор-вычитатель 7 заносится теперь код (

при ), в первый сумматор-вычитатель 3 заносится код сигнала в точке . Результаты вычислений Функдни заносятся в сумматоры 11 и -12 после срабатывания элемента И 18.

Этот процесс повторяется до тех пор, пока не будут исследованы все (N-1) точек (сигнал переполнения счетчика 27j| . Нормирование значений коэффициентов осуществляется в суммагорах 11 и 12 путем соответствующего выбора их разрядности и положения запятой. При этом необходимо, чтобы , тогда в сумматорах 11 и 12 получаются значения коэффициентов ряда Фурье А и В|, рассчитанные по формулам:

);

(n)coseТаким образом, предложенное устройство обладает тем существенным преимуществом, что благодаря введению новых блоков и связей достигается расширение функциональных возможностей известного устройства: предложенное устройство позволяет не только вычислять значения синуса и косинуса, но и получать коэффициенты ряда Фурье.

Кроме того, по сравнению с известными анализаторами в предложенном устройстве повышено быстродействие за счет совмещения по времени и аппаратуре выполнения операций получения значений гармонических функций с умножением последних на значения входного сигнала. Все это позволяет расширить область применения подобных устройств.

Формула изобретения

Цифровой гармонический анализатор содержащий генератор тактовых импульсов, регистр, три сумматора-вычитателя, сумматор, блоки элементов И, ИЛИ, элементы задержки, сдвигатели и два регистра сдвига, причем выходы первого регистра сдвига подключены к соответствующим входам первого и второго сдвигателей и к входу третьего сумматора-вычитателя, младшие входы которого подключены к соответствующим выходам первого регистра сдвига через первый блок элементов ИЛИ, нулевой выход знакового разряда третьего сумматора-вычитателя подключен к суммирукщему входу третьего сумматора-вычитателя,суммирующему входу первого сумматора-вычитателя и вычитающему входу второго сумматора-1зычитателя, выходы которого подключены к соответствующим входам первого регистра сдвига,выходы которого подключены к соответствующим входам первого..сдвигателя,выходы первого сумматора-вычитателя подключены к соответствующим входам второго сдвигателя выходы которого подключены к соответ ствующим входам второго сумматоравычитателя, суммирующий вход которого подключен к вычитающему входу и единичному выходу знакового разряда третьего сумматора-вычитателя и вычитающему входу первого сумматора-вычитателя, первый вход установки в ноль которого подключен к выходу первого элемента И, первый вход которого подключен к старядему выходу первого регистра сдвига и к первому входу второго элемента ИЛИ, выход которого подключен к первым управляющим входам первого и второго сдвигателей, а второй входко второму выходу первого регистра сдвига сдвигающий вход которого подключен к выходу второго элемента задержки, вход которого объединен со вторым входом первого элемента И управляющим входом третьего сумматора-вычитателя,первым входом второго элемента И и четвертым выходом второ регистра сдвига, третий выход которо го подключен к управляющему входу первого сумматора вычитателя второй выход подключен к управляющему входу второго сумматора-вычитателя, а первый выход - к управляющему входу регистра, вход установки в ноль которого подключен к входам установки в ноль второго сумматора-вычитателя второго регистра сдвига и первого регистра сдвига, последний выход ко торого подключен к управляющим входам первого и второго сдвигателей, вторые управляющие входы которого объединены с информационным входом третьего разряда третьего сумматоравычитателя ,о тл и ч ающий ся тем, что,.с целью расширения функциональных возможностей, в.него введены два сумматора, две кнопки, два ключа, счетчик, преобразователь аналог-код и буферный регистр, причем выходы третьего сумматора подключены ко входс1м первого блока элементов И а управляющий вход подключен к управ ляющему входу буферного регистра, выходу второго элемента И,первому входу первого элемента ИЛИ и входу первого элемента задержки, выход которого подключен к Управляющему входу второго блока элементов И выходы которого подключены к первой группе входов второго блока элементов ИЛИ, .вторая группа входов кото.рого подключена к выходам первого сдвигателя, а выходы ко входам первого сумматора-вычитателя, выход второй кнопки подключен к входам установки в ноль второго регистра сдвига, счетчика, пеового сумматора-вычитателя, третьего сумматора преобразователе аналог-код, буферного регистра, второго и первого сумматоров и первому входу третьего элемента ИЛИ, информационные входы второго и первого сумматоров подключены к соответствующим информационным выходам второго и первого сумматоров-вычитателей соответственно, а управляющие входы подключены к выходу третьего элемента И, первый вход которого подключен к третьему выходу второго регистра Сдвига,второй вход подключен ко второму входу второго элемента И, выходкоторого подключен к.первому входу первого элемента ИЛИ, йыход которого подключен к выходу установки единицы первого регистра сдвига, а второй вход - подключен к выходу первой кнопки, входу установки единицы второго регистра сдвига, второму входу четвертого элемента ИЛИ, единичному входу триггера, единичный выход которого подключен к первому входу четвертого элемента И, а нулевой вход - к выходу третьего элемента ИЛИ, второй вход которого подключен к выходу первого ключа, первый и второй входы которого подключены к первому и второму выходам счетчика соответственно, вход которого подключен к выходу младшего разряда первого регистра сдвига, выход генератора импульсов подключен ко второму входу четвертого элемента И, выход которого подключен к сдвигающему входу второго регистра сдвига, третий выход которюго подключен к первому входу четвертого элемента ИЛИ, выход которого подключён к управляющему входу преобразователя аналогкод, выхоц которого через второй ключ подключен к информационным входам буферного регистра, выхода которого подключены к информационным входам второго блока элементов И. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по Зс1явке 2636100/24,f кл. е 06 F 15/34, 1978.

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления синусно- косинусных функций | 1978 |

|

SU750495A1 |

| Вычислительное устройство | 1983 |

|

SU1167605A1 |

| Цифровое устройство для вычисления синусно-косинусных функций | 1980 |

|

SU868753A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для вычисления элементарных функций по алгоритму Волдера | 1982 |

|

SU1068933A1 |

| Линейный аппроксиматор | 1983 |

|

SU1157548A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

Авторы

Даты

1981-10-15—Публикация

1979-12-06—Подача