(21)4145842/24-24

(22)12.11.86

(46) 15.04.88. Бюл. № 14

(72) В.И.Балабай, В.М.Мачульский

и Б.А.Смирнов

(53)681.3(088.8)

(56)Авторское свидетельство СССР № 1038948, кл. G 06 F 15/20, 1981.

Авторское свидетельство СССР № 1164726, кл. G 06 F 15/20, 1983.

I

(54)УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ДЕЯТЕЛЬНОСТИ ОПЕРАТОРОВ СИСТЕМ ЧЕЛОВЕК - МАШИНА

(57)Изобретение относится к вычислительной технике, в частности к устройствам для моделирования деятельности операторов систем человек - машина. Цель изобретения - расширение функциональных возможностей устройства за счет моделирования групповой деятельности операторов. Для достижения цели устройство содержит регистры памяти, блок элементов задержки, элементы ИЛИ, схемы сравнения, блоки элементов И, элемент запрета, триггеры, группу регистров памяти, группу схем сравнения, группы, элементов ИЛИ, группу элементов И, накапливающий сумматор, элемент И, генератор тактовых импульсов, счетчик импульсов и группу блоков моделирования действий оператора, каждый иэ которых содержит регистр памяти, датчик случайных чисел, генератор равномерно распределенных чисел, схему сравнения, накапливающий сумма- g тор, счетчик выполненных операций. Устройство позволяет в результате моделирования количественно оценить качество деятельности группы операторов. 3 Ш1.

(Л

Изобретение относится к вычислительной технике, в частности к устройствам для моделирования деятельности олераторов систем человек - машина.

Целью изобретения является расширение функциональных возможностей устройства за счет моделирования грулповой деятельности операторов.

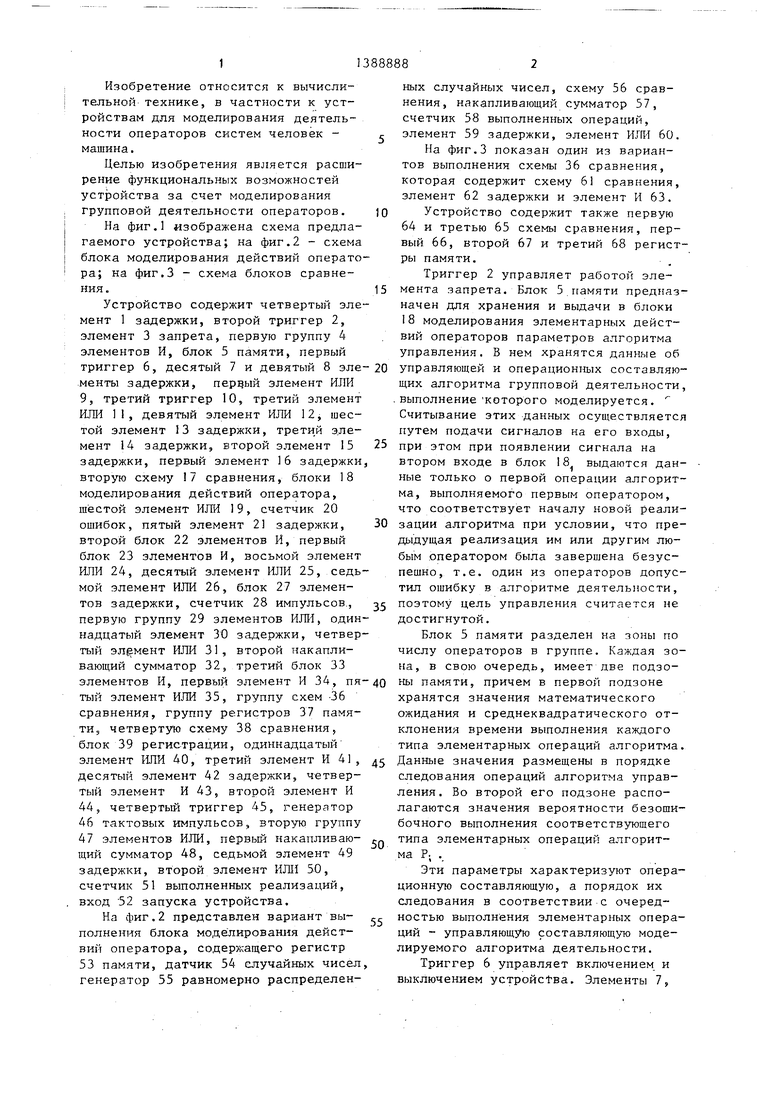

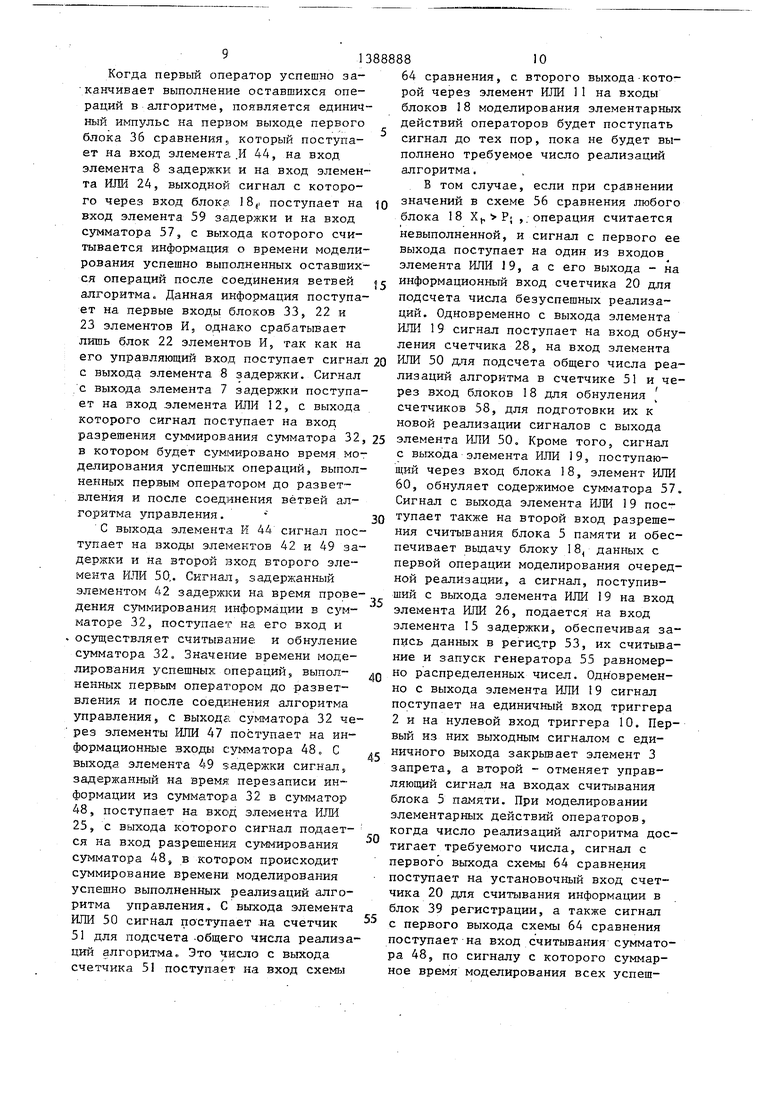

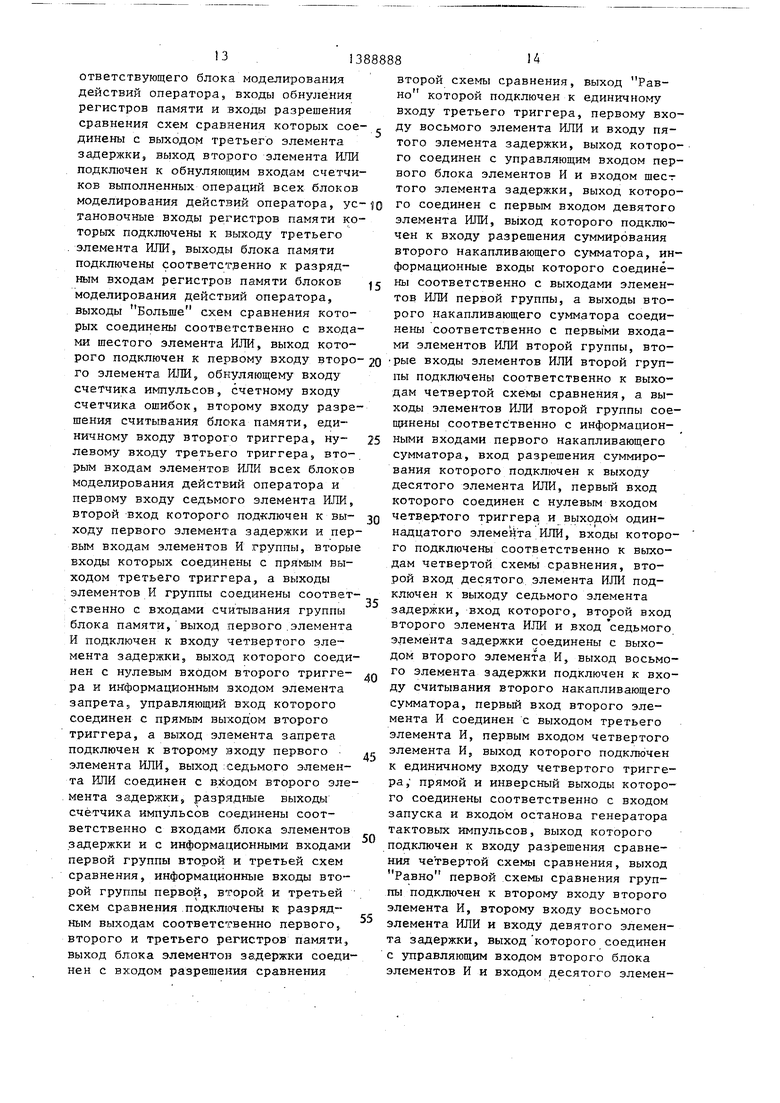

На фиг.1 изображена схема предлагаемого устройства; на фиг.2 - схема блока моделирования действий оператора; на фиг.З - схема блоков сравнения.

Устройство содержит четвертый элемент 1 задержки, второй триггер 2, элемент 3 запрета, первую группу 4 элементов И, блок 5 памяти, первый триггер 6, десятый 7 и девятый 8 эле -менты задержки, перчый элемент ИЛИ 9, третий триггер 10, третий элемент ИЛИ 11, девятый элемент ИЛИ 12, шестой элемент 13 за,держки, третий элемент 14 задержки, второй элемент 15 задержки, первый элемент 16 задержки вторую схему 17 сравнения, блоки 18 моделирования действий оператора, шестой элемент ИЛИ 9, счетчик 20 ошибок, пятый элемент 21 задержки, второй блок 22 элементов И, первый блок 23 элементов И, восьмой элемент ИЛИ 24, десятый элемент ИЛИ 25, седьмой элемент ИЛИ 26, блок 27 элементов задержки, счетчик 28 импульсов,, первую группу 29 элементов ИЛИ, одиннадцатый элемент 30 задержки, четвертый элемент ИЛИ 31, второй накапливающий сумматор 32, третий блок 33 элементов И, первый элемент И 34, пя тый элемент ИЛИ 35, группу схем -36 сравнения, группу регистров 37 памяти, четвертую схему 38 сравнения, блок 39 регистрации, одиннадцатый элемент ИЛИ 40, третий элемент И 41, десятый элемент 42 задержки, четвертый элемент И 43, второй элемент И 44, четвертый триггер 45, генератор

46тактовых импульсов, вторую группу

47элементов ИЛИ, первьш накапливаю- щий сумматор 48, седьмой элемент 49 задержки, второй элемент ИЛИ 50, счетчик 51 выполненных реализаций, вход 52 запуска устройства.

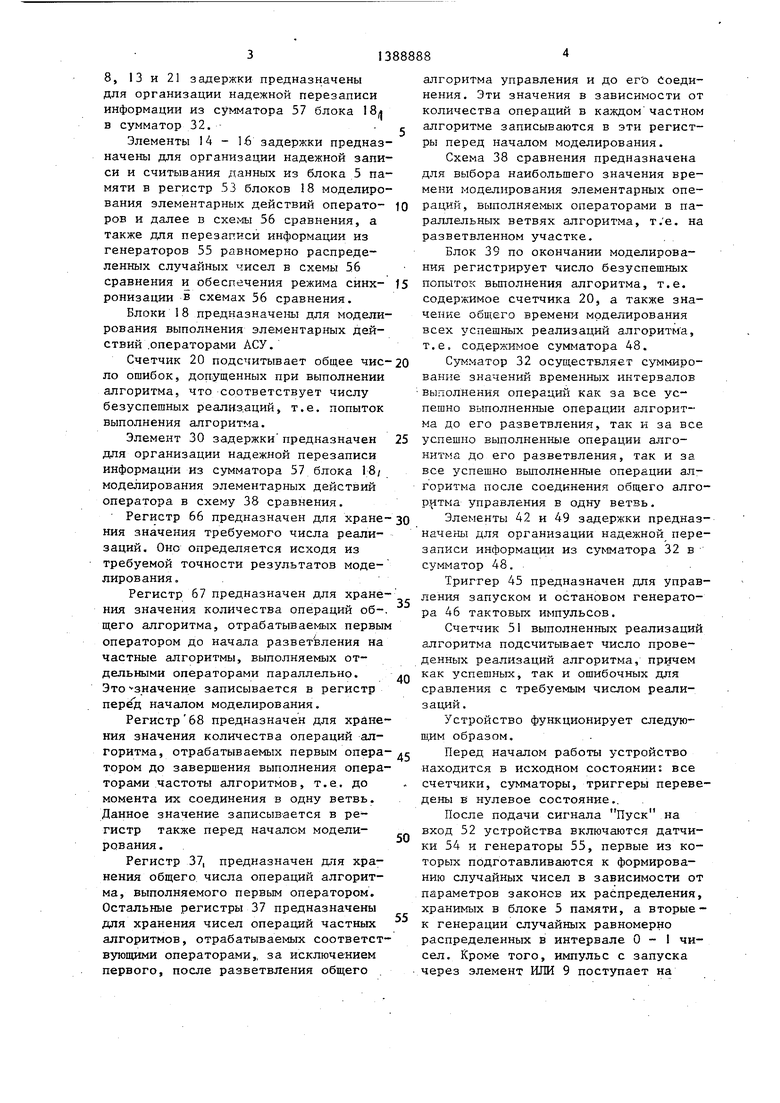

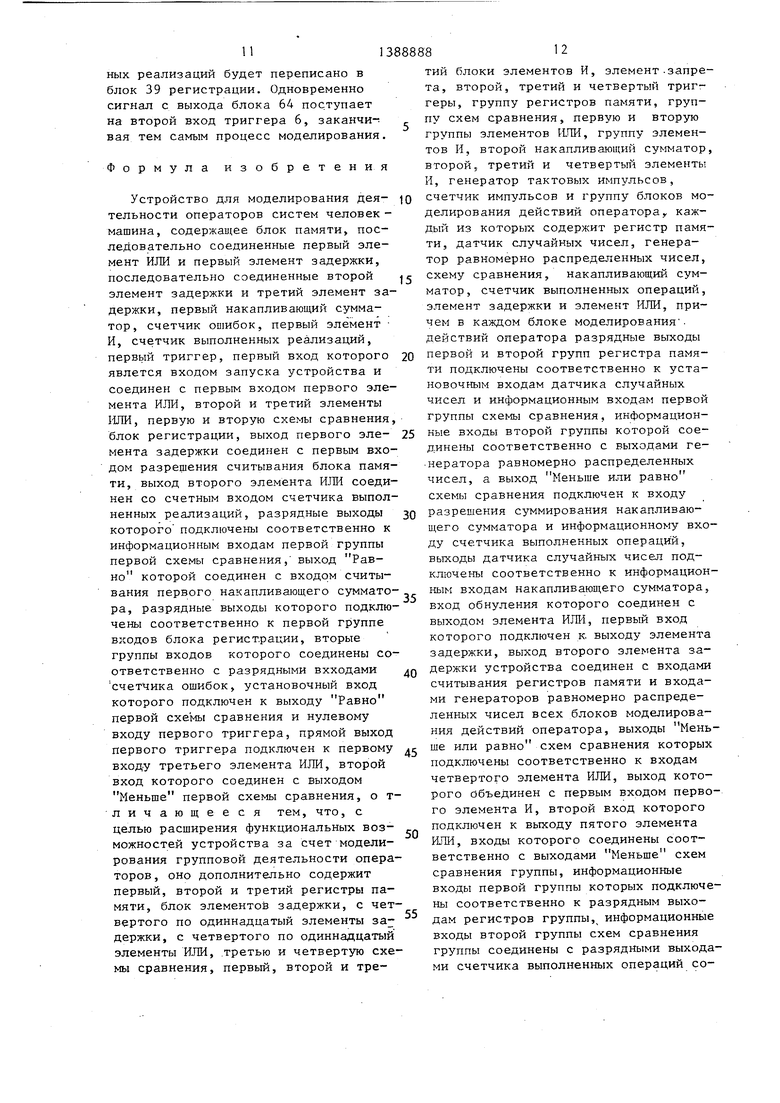

На фиг.2 представлен вариант вы- полнения блока моделирования действий оператора, содержащего регистр 53 памяти, датчик 54 случайных чисел генератор 55 равномерно распределенных случайных чисел, схему 56 сравнения, накапливающий сумматор 57, счетчик 58 выполненных операций, элемент 59 задержки, элемент ИЛИ 60.

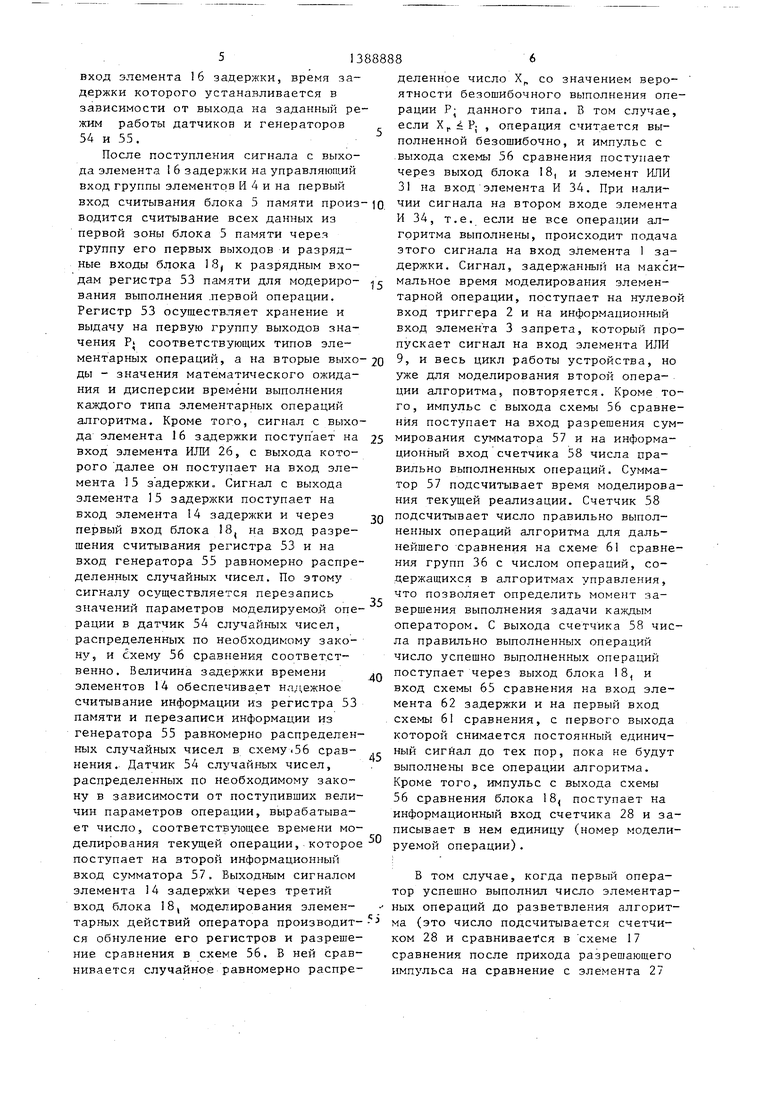

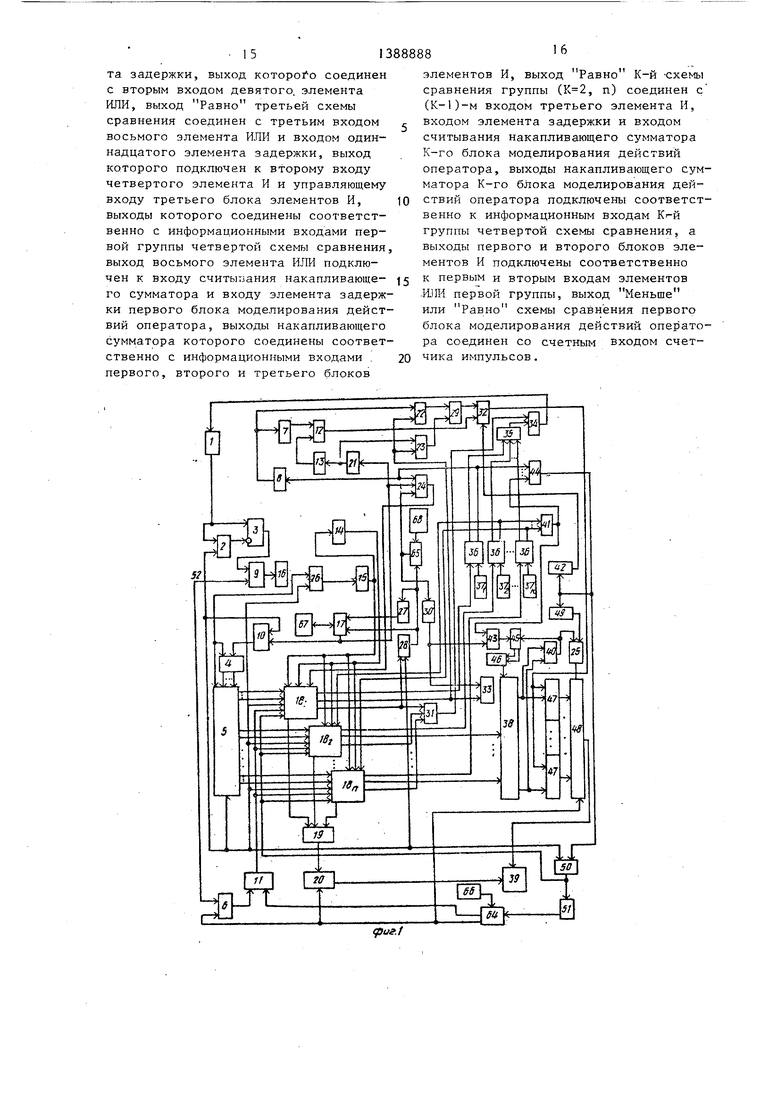

На фиг.З показан один из вариантов выполнения схемы 36 сравнения, которая содержит схему 61 сравнения, элемент 62 задержки и элемент И 63.

Устройство содержит также первую 64 и третью 65 схемы сравнения, первый 66, второй 67 и третий 68 регистры памяти.

Триггер 2 управляет работой элемента запрета. Блок 5 ггамяти предназначен для хранения и выдачи в блоки 18 моделирования элементарных действий операторов параметров алгоритма управления. В нем хранятся данные об управляющей и операционтшх составляющих алгоритма групповой деятельности, выполнение которого моделируется. Считывание этих данных осуществляется путем подачи сигналов на его входы, при этом при появлении сигнала на втором входе в блок 18 выдаются данные только о первой операции алгоритма, выполняемого первым оператором, что соответствует началу новой реализации алгоритма при условии, что предыдущая реализация им или другим любым оператором была завершена безуспешно, т.е. один из операторов допустил ошибку в алгоритме деятельности, поэтому цель управления считается не достигнутой.

Блок 5 памяти разделен на зоны по числу операторов в группе. Каждая зона, в свою очередь, имеет две подзоны памяти, причем в первой подзоне хранятся значения математического ожидания и среднеквадратического отклонения времени выполнения каждого типа элементарных операций алгоритма. Данные значения размещены в порядке следования операций алгоритма управления. Во второй его подзоне располагаются значения вероятности безошибочного выполнения соответствующего типа элементарных операций алгоритма Р; .

Эти параметры характеризуют операционную составляющую, а порядок их следования в соответствии с очередностью выполнения элементарных операций - управляющую составляющую моделируемого алгоритма деятельности.

Триггер 6 управляет включением и выключением ycтpoйctвa. Элементы 7,

8, 13 и 21 задержки предназначены для организации надежной перезаписи информации из сумматора 57 блока 18 в сумматор 32.

Элементы 14 - 16 задержки предназначены для организации надежной записи и считывания данных из блока 5 памяти в регистр 53 блоков 18 моделирования элементарных действий операторов и далее в схемы 56 сравнения, а также для перезаписи информации из генераторов 55 равномерно распределенных случайных чисел в схемы 56 сравнения и обеспечения режима синхронизации в схемах 56 сравнения.

Блоки 18 предназначены для моделирования выполнения элементарных действий .операторами АСУ.

Счетчик 20 подсчитывает общее число ошибок, допущенных при выполнении алгоритма, что соответствует числу безуспешных реализаций, т.е. попыток выполнения алгоритма.

Элемент 30 задержки предназначен для организации надежной перезаписи информации из сумматора 57 блока 18/ моделирования элементарных действий оператора в схему 38 сравнения.

Регистр 66 предназначен для хранения значения требуемого числа реализаций. Оно определяется исходя из требуемой точности результатов моделирования .

Регистр 67 предназначен для хранения значения количества операций об-, щего алгоритма, отрабатываемых первым оператором до начала развет вления на частные алгоритмы, выполняемых отдельными операторами параллельно. Это --значение записывается в регистр перёд началом моделирования.

Регистр 68 предназначен для хранения значения количества операций алгоритма, отрабатываемых первым оператором до завершения выполнения операторами частоты алгоритмов, т.е. до момента их соединения в одну ветвь. Данное значение записывается в ре гистр также перед началом моделирования.

Регистр 37, предназначен для хранения общего числа операций алгоритма, выполняемого первым оператором. Остальные регистры 37 предназначены для хранения чисел операций частных алгоритмов, отрабатываемых соответствующими операторами,, за исключением первого, после разветвления общего

0

5

0

5

0

5

0

5

алгоритма управления и до ег о Соединения. Эти значения в зависимости от количества операций в каждом частном алгоритме записываются в эти регистры перед началом моделирования.

Схема 38 сравнения предназначена для выбора наибольшего значения времени моделирования элементарных операций, выполняемых операторами в параллельных ветвях алгоритма, т. е. на разветвленном участке.

Блок 39 по окончании моделирования регистрирует число безуспешных попыток выполнения алгоритма, т.е. содержимое счетчика 20, а также значение общего времени моделирования всех успешных реализаций алгоритм а, т.е. содержимое сумматора 48.

Сумматор 32 осуществляет суммиро- вание значений временнь1Х интервалов выполнения операций как за все успешно выполненные операции алгоритма до его разветвления, так и за все успешно выполненные операции алго- нитма до его разветвления, так и за все успешно выполненные операции алгоритма после соединения общего алго- piiTMa управления в одну ветвь.

Элементы 42 и 49 задержки предназ- для организации надежной перезаписи информации из сумматора 32 в сумматор 48..

Триггер 45 предназначен для управления запуском и остановом генератора 46 тактовых импульсов.

Счетчик 51 выполненных реализаций алгоритма подсчитывает число проведенных реализаций алгоритма, причем как успешных, так и ошибочных для сравления с требуемым числом реализаций.

Устройство функционирует следующим образом.

Перед началом работы устройство находится в исходном состоянии: все счетчики, сумматоры, триггеры переведены в нулевое состояние..

После подачи сигнала Пуск на вход 52 устройства включаются датчики 54 и генераторы 55, первые из которых подготавливаются к формированию случайных чисел в зависимости от параметров законов их распределения, хранимых в блоке 5 памяти, а вторые- к генерации случайных равномерно распределенных в интервале О - 1 чисел. Кроме того, импульс с запуска через элемент ИЛИ 9 поступает на

вход элемента 16 задержки, время задержки которого устанавливается в зависимости от выхода на заданный режим работы датчиков и генераторов 54 и 55.

После поступления сигнала с выхода элемента 1 6 задержки на управляющий вход группы элементов И 4 и на первый

деленное число Х со значением вероятности безошибочного выполнения операции Р; данного типа. В том случае, если , операция считается выполненной безошибочно, и импульс с .выхода схемы 56 сравнения поступает через выход блока 18, и элемент ИЛИ 31 на вход элемента И 34, При нали

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1399761A1 |

| Устройство для моделирования деятельности человека-оператора | 1988 |

|

SU1580388A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1377870A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1413640A1 |

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1164726A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1432553A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1545226A1 |

| Устройство для моделирования деятельности человека-оператора | 1990 |

|

SU1778761A1 |

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1241254A2 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

вход считывания блока 5 памяти произ- )0 сигнала на втором входе элемента

водится считывание всех данных из первой зоны блока 5 памяти через группу его первых выходов и разрядные входы блока 18( к разрядным входам регистра 53 памяти для модериро- вания выполнения .первой операции. Регистр 53 осуществляет хранение и выдачу на первую группу выходов значения соответствующих типов элементарных операций, а на вторые выхо- ды - значения математического ожидания и дисперсии времени выполнения каждого типа элементарных операций алгоритма. Кроме то.г,о, сигнал с выхода элемента 16 задержки поступает на вход элемента ИЛИ 26, с выхода которого далее он поступает на вход элемента 5 задержки,, Сигнал с выхода элемента 15 задержки поступает на вход элемента 14 задержки и через первый вход блока IB на вход разрешения считывания регистра 53 и на вход генератора 55 равномерно распределенных случайных чисел. По этому сигналу осуществлягется перезапись значений параметров моделируемой операции в датчик 54 случайных чисел, распределенных по необходимому закону, и схему 56 сравнения соответственно. Величина задержки времени элементов 14 обеспечивает надежное считывание информации из регистра 53 памяти и перезаписи информации из генератора 55 равномерно распределенных случайных чисел в схему 56 сравнения. Датчик 54 случайных чисел, распределенных по необходимому закону в зависимости от поступивших величин параметров операции, вырабатывает число, соответствующее времени моделирования текущей операции, которое поступает на второй информационный вход сумматора 57. Выходным сигналом элемента 14 задержи через третий вход блока 18( модехшрования элементарных действий оператора производит- СИ обнуление его регистров и разрешение сравнения в схем;е 56. В ней сравнивается случайное равномерно распре

5

0 5 о

5

0

5

0

И 34, т.е. если не все операции алгоритма выполнены, происходит подача этого сигнала на вход э.лемента 1 задержки. Сигнал, задержанный на максимальное время моделирования элементарной операции, поступает на нулевой вход триггера 2 и на информационный вход элемента 3 запрета, который пропускает сигнал на вход элемента ИЛИ 9, и весь цикл работы устройства, но уже для моделирования второй операции алгоритма, повторяется. Кроме того, импульс с выхода схемы 56 сравнения поступает на вход разрешения суммирования сумматора 57 и на информационный вход счетчика 58 числа правильно выполненных операций. Сумматор 57 подсчитывает время моделирования текущей реализации. Счетчик 58 подсчитывает число правильно выполненных операций алгоритма для дальнейшего сравнения на схеме 61 сравнения групп 36 с числом операций, содержащихся в алгоритмах управления, что позволяет определить момент завершения выполнения задачи каждым оператором. С выхода счетчика 58 числа правильно выполненных операций число успешно выполненных операций поступает через выход блока 18, и вход схемы 65 сравнения на вход элемента 62 задержки и на первый вход схемы 61 сравнения, с первого выхода которой снимается постоянный единичный сигнал до тех пор, пока не будут выполнены все операции алгоритма. Кроме того, импульс с выхода схемы 56 сравнения блока 18 поступает на информационный вход счетчика 28 и записывает в нем единицу (номер моделируемой операции).

В том случае, когда первый оператор успешно выполнил число элементарных операций до разветвления алгоритма (это число подсчитывается счетчиком 28 и сравниваемся в схеме 17 сравнения после прихода разрешающего импульса на сравнение с элемента 27

задержки), на выходе схемы 17 сравнения появляется единичный импульс. Далее сигнал поступает на единичный вход триггера 10, на вход элемента 21 задержки и на первый вход элемента ИЛИ 24, выходной сигнал с которого через четвертый вход блока 18 поступает на вход элемента 59 задержки и на установочный вход сумматора 57, считывая с него информацию через четвертый выход блока 18, на информационные входы блока 33 элементов И, на информационные входы блоков 22 и 23 элементов И. Сигнал, задержанный на время считывания информации из сумматора 57, с выхода элемента 59 задержки через элемент ИЛИ 60 обнуляет сумматор 57.

Сигнал, задержанный элементом 2, организует перезапись информации из сумматора 57 через блок 23 элементов И и группу 29 элементов ИЛИ в тор 32. Сигнал с выхода элемента ГЗ

задержки, задержанный на время сраба-25 вается информация времен моделироватывания элементов 23 и 29 через элемент ИЛИ 12 поступает на вход разрешения записи сумматора 32, Таким образом, в сумматоре 32 будет записано

ния успешно выполненных операций алгоритма вторым, третьим и последующими операторами (т.е. операций разветвленной части общего алгоритма управзначение времени моделирования успеш- 30 ления). Данная информация поступает

ных операции первым оператором до разветвления алгоритма управления. Одновременно сигнал с единичного выхода триггера 10 поступает на второй Вход первой группы 4 элементов И.

При наличии сигналов на обоих входах первой группы 4 элементов И она срабатывает, и сигнал с ее группы выходов поступает на входы разрешения считывания блока 5 памяти. Произво- дится считывание всех данных из имеющихся зон блока 5 к разрядным входам регистров 53 памяти блоков 18 для моделирования выполнения первой операции разветвления алгоритма управления. Работа устройства по моделированию разветвленного участка ничем, не отличается от описанной.

В том случае, если первый оператор успешно выполнил число элементарных операций разветвленного алгоритма, а момент завершения определяется схемой 65 сравнения, на его первом выходе появляется единичный импульс. Этот импульс поступает на вход элемента 30 задержки и на вход элемента ИЛИ 24, выходной сигнал с которого через вход блока 18 поступает на вход элемента 59 задержки и на вход

5

юсумматора 57, считывая с него информацию на входы блоков 33, 22 и 23 элементов И. Сигнал, задержанный элементом 59 задержки на время считывания информации из сумматора 57, через элемент ИЛИ 60 обнуляет сумматор 57, а сигнал с выхода элемента 30 задержки организует перезапись информации из сумматора 57 через блок 33 элементов И на один из входо-в схемы 38 сравнения. Из-за отсутствия сигналов на вторых входах блоков 23 и 22 элементов И считанная информа- 5 Ция из сумматора 57 блока 18 на сумматор 32 не поступает.

В том случае, когда другие операторы успешно закончат выполнение своих алгоритмов, на первых выходах соответствующих схем 36 появятся сигналы, поступающие на входы элемента И 41 и через входы блоков 18 - 18, на входы элементов 59 задержки и на входы слт маторов 57, с которых считы20

ния успешно выполненных операций алгоритма вторым, третьим и последующими операторами (т.е. операций разветвленной части общего алгоритма управ5

Q

5

5

0

на остальные входы схемы 38 сравнения. Сигнал с выхода элемента И 41 поступает на вход элемента И 44 и на второй вход элемента И 43, который срабатывает, так как на его первом входе имеется сигнал.

Выходной сигнал с элемента И 43 поступает на единичный вход триггера 45, сигналом с единичного выхода которого запускается генератор 46, тактовые импульсы которого поступают на второй вход схемы 38 сравнения, которая выбирает наибольшее значение числа из всех поступающих на вторздо схему 38 сравнения. С выходов второй схемы 38 сравнения через вторую группу элементов ИЛИ 47 значение максимального времени моделирования разветвленного участка алгоритма поступает на первые информационные входы сумматора 48 и на входы элемента ИЛИ 40, выходной сигнал с которого поступает на нулевой вход триггера 45 (тем самым прекращая работу генератора 46). и на вход элемента ИЛИ 25, с выхода которого сигнал поступает на вход разрешения суммирования сумматора 48.

64 сравнения, с второго выхода-которой через элемент ИЛИ 11 на входы блоков 18 моделирования элементарных действий операторов будет поступать сигнал до тех пор, пока не будет выполнено требуемое число реализаций алгоритма.

В том случае, если при сравнении значений в схеме 56 сравнения любого блока 18 Х, р. ,. операция считается невыполненной, и сигнал с первого ее выхода поступает на один из входов элемента ИЛИ 19, ас его выхода - на

Когда первый оператор успешно за- канчивает выполнение оставшихся операций в алгоритме, появляется единич- ньгй импульс на выходе первого блока 36 сравнения., который поступает на вход элемента .И 44, на вход, элемента 8 задержки и на вход элемента ИЛИ 24, выходной сигнал с которого через вход блока 18,. поступает на tO вход элемента 59 задержки и на вход сумматора 57, с выхода которого считывается информация о времени моделирования успешно выполненных оставшихся операций после соединения ветвей j информационный вход счетчика 20 для алгоритма. Данная информация поступа- подсчета числа безуспешных реализа- ет на первые входы блоков 33, 22 и 23 элементов И, однако срабатывает лишь блок 22 элементов И, так как на его управляющий вход поступает сигнал 20 50 для подсчета общего числа реа- с выхода элемента 8 задержки. Сигнал лизаций алгоритма в счетчике 51 и че- с выхода элемента 7 задержки поступает на вход .элемента ИЛИ 12, с выхода которого сигнал поступает на вход

разрешения суммирования сумматора 32, 25 элемента ИЛИ 50. Кроме того, сигнал в котором будет суммировано время мо- с выхода элемента ИЛИ 19, поступаю- делирования успешных операций, выполненных первым оператором до разветвления и после соединения ветвей алгоритма управления. 30

С выхода элемента К 44 сигнал поступает на входы элементов 42 и 49 задержки и на второй вход второго элемента ИЛИ 50,. Сигнал, задержанный

ций. Одновременно с выхода элемента ИЛИ 19 сигнал поступает на вход обнуления счетчика 28, на вход элемента

рез вход блоков 18 для обнуления счетчиков 58, для подготовки их к новой реализации сигналов с выхода

щий через вход блока 18, элемент ИЛИ 60, обнуляет содержимое сумматора 57, Сигнал с выхода элемента ИЛИ 19 поступает также на второй вход разрешения считывания блока 5 памяти и обеспечивает выдачу блоку 18, данных с первой операции моделирования очередной реализации, а сигнал, поступивший с выхода элемента ИЛИ 19 на вход элемента ИЛИ 26, подается на вход элемента 15 задержки, обеспечивая за- данных в регис тр 53, их считывание и запуск генератора 55 равномерно распределенных чисел. Одн овремен- но с выхода элемента ИЛИ 19 сигнал поступает на единичный вход триггера 2 и на нулевой вход триггера 10. Первый из них выходным сигналом с единичного выхода закрывает элемент 3 запрета, а второй - отменяет управляющий сигнал на входах считывания блока 5 памяти. При моделировании элементарных действий операторов, когда число ре,ализаций алгоритма достигает требуемого числа, сигнал с первого выхода схемы 64 сравнения поступает на установочный вход счетчика 20 для считывания информации в блок 39 регистрации, а также сигнал с первого выхода схемы 64 сравнения поступает на вход считывания сумматора 48, по сигналу с которого суммарное время моделирования всех успешэлементом 42 задержки на время проведения суммирования информации в маторе 32, поступает на его вход и осуществляет считывание и обнуление сумматора 32. Значение времени моделирования успешных операций, выполненных первым оператором до разветвления и после соединения алгоритма управления, с выхода сумматора 32 через элементы ИЛИ 47 поступает на информационные входы сумматора 48 С выхода элемента 49 задержки сигнал, задержанный на время перезаписи информации из сумматора 32 в сумматор 48, поступает на вход элемента ИЛИ 25, с выхода которого сигнал подает- ся на вход разрешения суммирования сумматора 48, в котором происходит суммирование времени моделирования успешно выполненных реализаций алгоритма управления, С выхода элемента ИЛИ 50 сигнал по ступает на счетчик 51 для подсчета -общего числа реализаций алгоритма. Это число с выхода счетчика 51 поступает на вход схемтз

64 сравнения, с второго выхода-которой через элемент ИЛИ 11 на входы блоков 18 моделирования элементарных действий операторов будет поступать сигнал до тех пор, пока не будет выполнено требуемое число реализаций алгоритма.

В том случае, если при сравнении значений в схеме 56 сравнения любого блока 18 Х, р. ,. операция считается невыполненной, и сигнал с первого ее выхода поступает на один из входов элемента ИЛИ 19, ас его выхода - на

информационный вход счетчика 20 для подсчета числа безуспешных реализа- 50 для подсчета общего числа реа- лизаций алгоритма в счетчике 51 и че-

информационный вход счетчика 20 для подсчета числа безуспешных реализа- 50 для подсчета общего числа реа- лизаций алгоритма в счетчике 51 и че-

ций. Одновременно с выхода элемента ИЛИ 19 сигнал поступает на вход обнуления счетчика 28, на вход элемента

информационный вход счетчика 20 для подсчета числа безуспешных реализа- 50 для подсчета общего числа ре лизаций алгоритма в счетчике 51 и ч

рез вход блоков 18 для обнуления счетчиков 58, для подготовки их к новой реализации сигналов с выхода

5 элемента ИЛИ 50. Кроме того, сигнал с выхода элемента ИЛИ 19, поступаю- 0

5

0

щий через вход блока 18, элемент ИЛИ 60, обнуляет содержимое сумматора 57, Сигнал с выхода элемента ИЛИ 19 поступает также на второй вход разрешения считывания блока 5 памяти и обеспечивает выдачу блоку 18, данных с первой операции моделирования очередной реализации, а сигнал, поступивший с выхода элемента ИЛИ 19 на вход элемента ИЛИ 26, подается на вход элемента 15 задержки, обеспечивая за- данных в регис тр 53, их считывание и запуск генератора 55 равномерно распределенных чисел. Одн овремен- но с выхода элемента ИЛИ 19 сигнал поступает на единичный вход триггера 2 и на нулевой вход триггера 10. Первый из них выходным сигналом с единичного выхода закрывает элемент 3 запрета, а второй - отменяет управляющий сигнал на входах считывания блока 5 памяти. При моделировании элементарных действий операторов, когда число ре,ализаций алгоритма достигает требуемого числа, сигнал с первого выхода схемы 64 сравнения поступает на установочный вход счетчика 20 для считывания информации в блок 39 регистрации, а также сигнал с первого выхода схемы 64 сравнения поступает на вход считывания сумматора 48, по сигналу с которого суммарное время моделирования всех успеш5

0

ных реализаций будет переписано в блок 39 регистрации. Одновременно сигнал с выхода блока 64 поступает на второй вход триггера 6, заканчи-; вая тем самым процесс моделирования.

Формула изобретения

Устройство для моделирования деятельности операторов систем человек - машина, содержащее блок памяти, последовательно соединенные первый элемент ИЛИ и первый элемент задержки, последовательно соединенные второй элемент задержки и третий элемент задержки, первый накапливающий сумматор, счетчик ошибок, первый элемент И, счетчик выполненных реализаций, первый триггер, первый вход которого явлется входом запуска устройства и соединен с первым входом первого элемента ИЛИ, второй и третий элементы ИЛИ, первую и вторую схемы сравнения блок регистрации, выход первого эле- мента задержки соединен с первым входом разрешения считывания блока памяти, выход второго элемента ИЛ1-1 соединен со счетным входом счетчика выполненных реализаций, разрядные выходы которого подключены соответственно к информационным входам первой группы первой схемы сравнения, выход Равно которой соединен с входом считывания первого накапливающего суммато

ра, разрядные выходы которого подключены соответственно к первой группе входов блока регистрации, вторые группы входов которого соединены соответственно с разрядными вхходами счетчика ошибок, установочный вход которого подключен к выходу Равно первой схемы сравнения и нулевому входу первого триггера, прямой выход первого триггера подключен к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом Меньше первой схемы сравнения, о т- личающееся тем, что, с целью расширения функциональных возможностей устройства за счет моделирования групповой деятельности операторов , оно дополнительно содержит первый, второй и третий регистры памяти, блок элементов задержки, с вертого по одиннадцатый элементы за держки, с четвертого по одиннадцатый элементы ИЛИ, .третью и четвертую схемы сравнения, первый, второй и тречет-

10

15

20 , 25 зо8888812

тий блоки элементов И, элемент-запрета, второй, третий и четвертый триггеры, группу регистров памяти, группу схем сравнения, первую и вторую группы элементов ИЛИ, группу элементов И, второй накапливающий сумматор, второй5 третий и четвертьпЧ элементы И, генератор тактовых импульсов, счетчик импульсов и группу блоков моделирования действий оператора,, каждый из которых содержит регистр памяти, датчик случайных чисел, генератор равномерно распределенных чисел, схему сравнения, накапливающий сумматор, счетчик выполненных операций, элемент задержки и элемент ИЛИ, причем в каждом блоке моделирования , действий оператора разрядные выходы первой и второй групп регистра памяти подключены соответственно к установочным входам датчика случайных чисел и информационным входам первой группы схемы сравнения, информационные входы второй группы которой соединены соответственно с выходами генератора равномерно распределенных чисел, а выход Меньше или равно схемы сравнения подключен к входу разрешения суммирования накапливающего сумматора и информационному входу счетчика выполненных операции, выходы датчика случайных чисел подключены соответственно к информационным входам накапливающего сумматора, вход обнуления которого соединен с выходом элемента ИЛИ, первый вход которого подключен к. выходу элемента задержки, выход второго элемента задержки устройства соединен с входами считывания регистров памяти и входами генераторов равномерно распределенных чисел всех блоков моделирования действий оператора, выходы Меньше или равно схем сравнения которых подключены соответственно к входам четвертого элемента ИЛИ, выход которого объединен с первым входом первого элемента И, второй вход которого подключен к выходу пятого элемента ИЛИ, входы которого соединены соответственно с выходами Меньше схем сравнения группы, информационные входы первой группы которых подключены соответственно к разрядным выходам регистров группы, информационные входы второй группы схем сравнения группы соединены с разрядными выходами счетчика выполненных операций со35

40

45

50

55

ответствующего блока моделирования действий оператора, входы обнуления регистров памяти и входы разрешения сравнения схем срав1с1ения которых сое динены с выходом третьего элемента задержки, выход второго элемента ИЛИ подключен к обнуляющим входам счетчиков выполненных операций всех блоков моделирования действий оператора, ус тановочные входы регистров памяти которых подключены к выходу третьего элемента ИЛИ, выходы блока памяти подключены соответственно к разрядным входам регистров памяти блоков моделирования действий оператора, выходы Больше схем сравнения которых соединены соответственно с входами шестого элемента ИЛИ, выход которого подключен к первому входу второ го элемента ИЛИ, обнуляющему входу счетчика импульсов, счетному входу счетчика ошибок, второму входу разрешения считывания блока памяти, единичному входу второго триггера, нулевому входу третьего триггера, вторым входам элементов ИПИ всех блоков моделирования действий оператора и первому входу седьмого элемента ИЛИ, второй -вход которого подключен к выходу первого элемента задержки и первым входам элементов И группы, вторы входы которых соединены с прямым выходом третьего триггера, а выходы элементов И группы соединены соответственно с входами считывания группы блока памяти, выход первого .элемента И подключен к входу четвертого элемента задержки, выход которого соединен с нулевым входом второго тригге- ра и информационным зходом элемента запрета, управляющий вход которого соединен с прямым выходом второго триггера, а выход элемента запрета подключен к второму входу первого . элемента ИЛИ, выход :седьмого элемента ИПИ соединен с входом второго элемента Зсщержки, разрядные выходы счётчика импульсов соединены соответственно с входами блока элементов задержки и с информационными входами первой группы второй и третьей схем сравнения, информационные входы второй группы первой, второй и третьей схем сравнения подключены к разрядным выходам соответственно первого,, второго и третьего регистров памяти, выход блока элементов задержки соединен с входом разрешения сравнения

5

, 0 д

0

5

5

0

5

второй схемы сравнения, выход Равно которой подключен к единичному входу третьего триггера, первому входу восьмого элемента ИЛИ и входу пятого элемента задержки, выход которого соединен с управляющим входом первого блока элементов И и входом шест того элемента задержки, выход которого соединен с первым входом девятого элемента ИЛИ, выход которого подключен к входу разрешения суммирования второго накапливающего сумматора, информационные входы которого соединены Соответственно с выходами элементов ИЛИ первой группы, а выходы второго накапливающего сумматора соединены соответственно с первыми входами элементов ИЛИ второй группы, вто- рые входы элементов ИЛИ второй группы подключены соответственно к выходам четвертой схемы сравнения, а выходы элементов ИЛИ второй группы сое- щинены соответственно с информационными входами первого накапливающего сумматора, вход разрешения суммирования которого подключен к выходу десятого элемента ИЛИ, первый вход которого соединен с нулевым входом 4eTBepkToro триггера и выходом одиннадцатого элемента ИЛИ, входы которого подключены соответственно к выходам четвертой схемы сравнения, второй вход десятого элемента ИЛИ подключен к выходу седьмого элемента задержки, вход которого, второй вход второго элемента ИЛИ и вход седьмого элемента задержки соединены с выходом второго элемента И, выход восьмого элемента задержки подключен к входу считывания второго накапливающего сумматора, первьш вход второго элемента И соединен с выходом третьего элемента И, первым входом четвертого элемента И, выход которого подключен к единичному входу четвертого триггера; прямой и инверсный выходы которого соединены соответственно с входом запуска и входом останова генератора тактовых импульсов, выход которого подключен к входу разрешения сравнения четвертой схемы сравнения, выход Равно первой схемы сравнения группы подключен к второму входу второго элемента И, второму входу восьмого элемента ИЛИ и входу девятого элемента задержки, выход которого соединен с управляющим входом второго блока элементов И и входом десятого элемен(paf.i

От л. 15

.f KffA.31 ОтЗл.ЗВ

ID

iS a

Фие.2

Фиг.З

Авторы

Даты

1988-04-15—Публикация

1986-11-12—Подача