Известны способы исправления ложных срабатываний ячеек двоичных счетчиков.

Предложенный способ отличается тем, что в нем с помощью схем совпадения на выходе ячейки анализируют состояния всех предыдущих ячеек счетчика, задерживают сигнал с выхода триггера при его ложном срабатывании, произошедшем до установки всех предыдуш,их ячеек в единичные состояния, и подают сигнал по цени обратной связи на вход триггера для возвращения его в исходное состояние, причем после подачи задержанного сигнала цепь обратной связи временно размыкают для предотвращения повторного срабатывания.

Это повышает надежность счета и упрощает цепи коррекции.

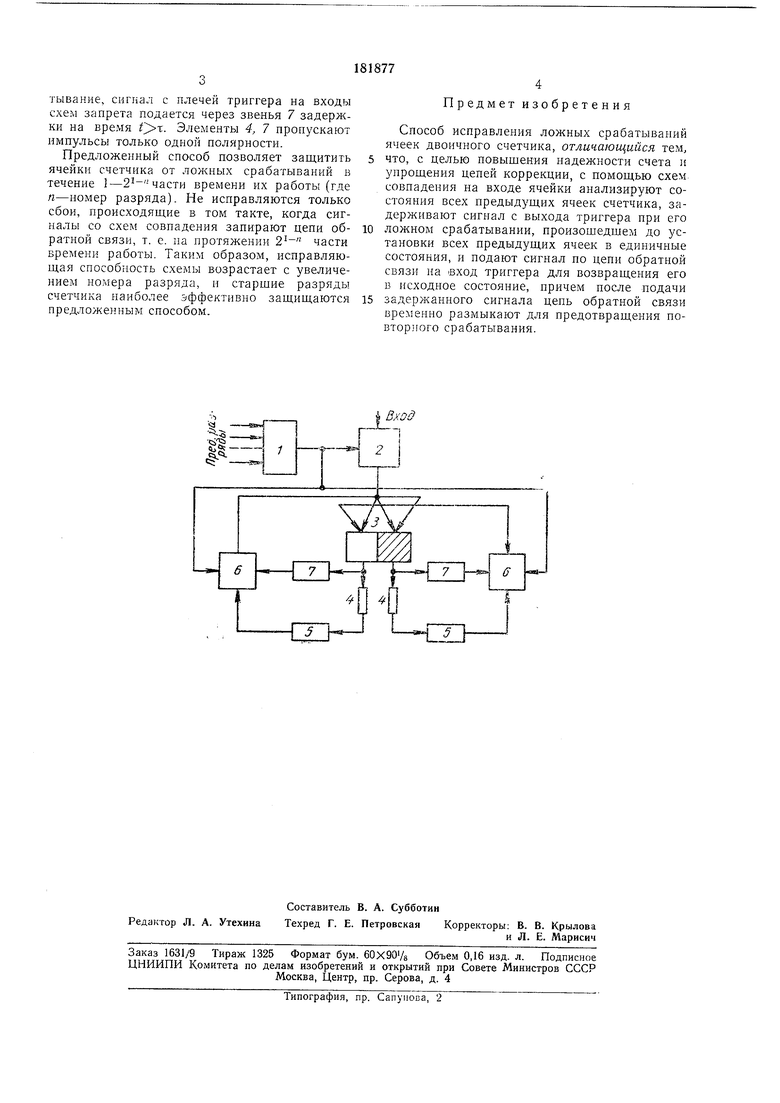

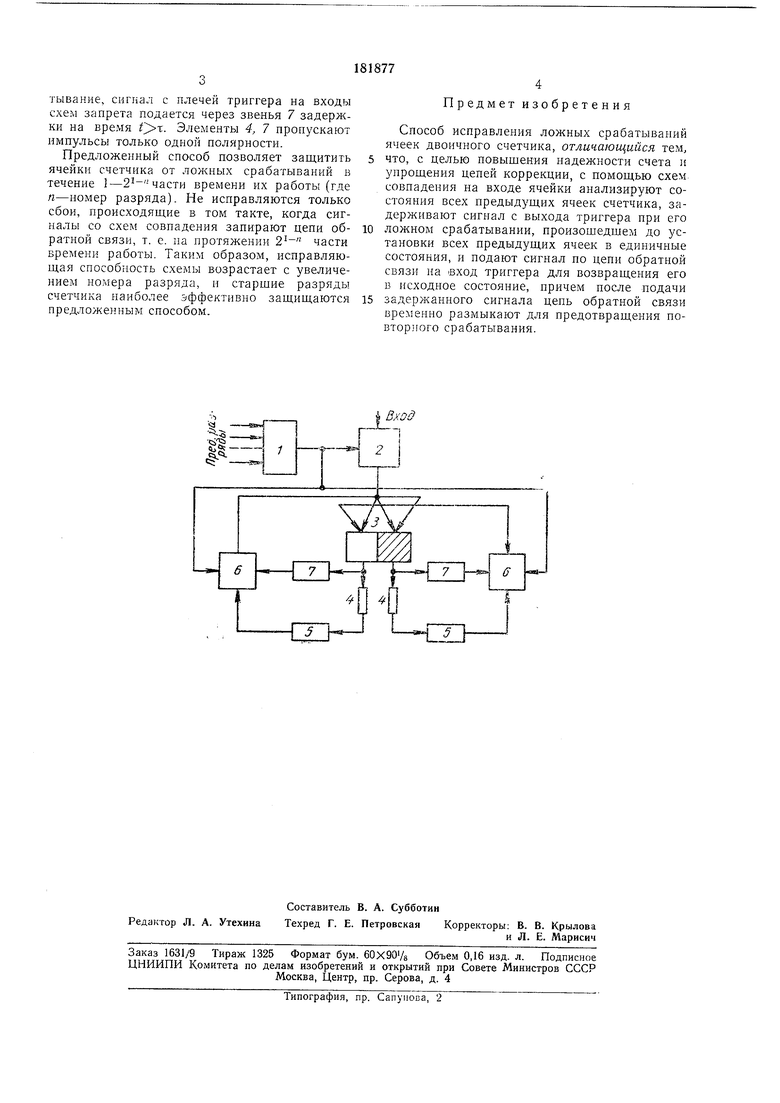

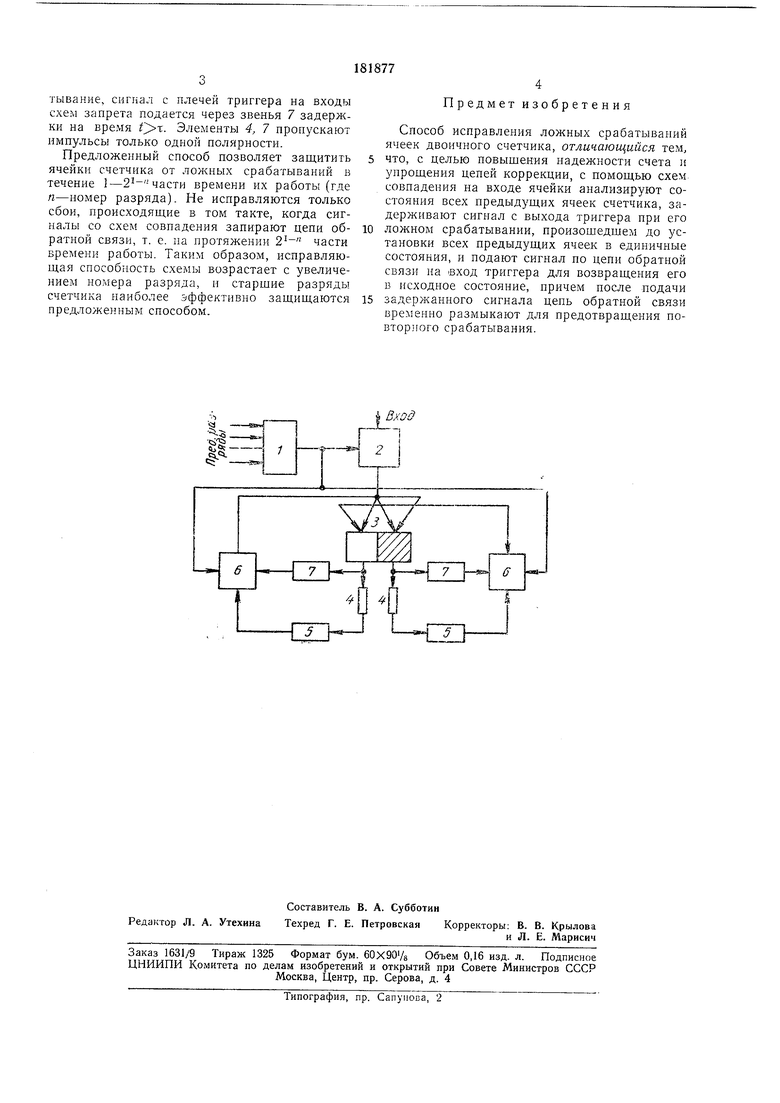

Способ иллюстрируется схемой.

Ячейка двоичного счетчика с исправлением ложных срабатываний состоит из многовходовой схемы совпадения /, входного вентиля 2, статического триггера 3, дифференцирующих цепочек 4, схемы 5 задержки на время т, потенциально-импульсных схем запрета 6 и звеньев 7 задержки на время t. Состояние разряда считывается с одного плеча триггера 3.

Счетчик построен по схеме сквозного переноса, причем входной сигнал подается на выходы вентилей 2 всех разрядов счетчика одновременно. Если все разряды, предшествующие данному, находятся в единичных состояниях, то выход схемы совпадения 1 возбужден, что позволяет входному сигналу через вентиль 2 пройти на вход триггера 3, в результате чего происходит нормальное срабатывание триггера.

Цепи обратной связи в это время разомкнуты схемами запрета 6, входы которых возбуждены сигналом с выхода схемы совпадения /. Однако, если не все разряды, предшествующие данному, находятся в единичных состояниях, то любое срабатывание триггера данного разряда ложно и должно быть исправлено. В этом случае выход схемы совпадения 1 не возбужден, вентиль 2 заперт, а цепь обратной

связи замкнута. Если в таком состоянии произойдет срабатывание (например, от помех) триггера, то продифференцированный цепочками 4 и задерл :анный на время т, нревышающее длительность переходных процессов и

триггере, схемами 5 сигнал пройдет через одну из схем запрета 6 на вход триггера и возвратит его в исходное состояние. После возвращения триггера в исходное (истинное) состояние импульс появится на другом выходе тригтывание, сигнал с плечей триггера на входы схем запрета подается через звенья 7 задержки на время . Элементы 4, 7 пропускают пмпульсы только одной полярности.

Предложенный способ позволяет запдитить ячейки счетчика от ложных срабатываний в течение -2--части времени их работы (где п-номер разряда). Не исправляются только сбои, происходящие в том такте, когда сигналы со схем совпадения запирают цепи обратной связи, т. е. па протяжении 2 части времени работы. Таким образом, исправляющая способность схемы возрастает с увеличением номера разряда, п старщие разряды счетчика наиболее эффективно защищаются предложенным способом.

Предмет изобретения

Способ исправления ложных срабатываний ячеек двоичного счетчика, отличающийся тем что, с целью повыщения надежности счета и упрощения цепей коррекции, с помощью схем совпадения па входе ячейки анализируют состояния всех предыдущих ячеек счетчика, задерживают сигнал с выхода триггера при его ложном срабатывании, произощедщем до установки всех предыдущих ячеек в единичные состояния, и подают сигнал по цепи обратной связи на вход триггера для возвращения его в исходное состояние, причем после подачи задержанного сигнала цепь обратной связи размыкают для предотвращения повторного срабатывания.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК | 1971 |

|

SU311405A1 |

| Двоичный счетчик импульсов с коррекцией | 1976 |

|

SU610308A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1971 |

|

SU293256A1 |

| Двоичный счетчик импульсов с контролем ошибок | 1977 |

|

SU687601A1 |

| СЧЕТЧЙК ИМПУЛЬСОВ | 1971 |

|

SU294256A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ С ФУНКЦИЕЙ ИСПРАВЛЕНИЯ ОШИБОК | 2011 |

|

RU2486682C2 |

| ДВОИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1971 |

|

SU301858A1 |

| УСТРОЙСТВО для УПРАВЛЕНИЯ ЦИФРОСИНТЕЗИРУЮЩИМ | 1969 |

|

SU249094A1 |

| НЕПРЕРЫВНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1969 |

|

SU241121A1 |

|Я,

Даты

1966-01-01—Публикация