Изобретение относится к области автоматики и вычислительной техники.

Известен цифровой интегратор типа двоичного сумматора, выполненный на динамических, например, ферриттранзисторных элементах, содержащий регистр подынтегральной функции, накопитель приращения интеграла и кольцевой сдвигающий регистр, который обеспечивает синхронизацию работы устройства.

Предлагаемый непрерывный (быстродействующий) цифровой интегратор отличается от известных тем, что содержит динамические триггеры, связанные с регистром подынгегральной функции и накопителем приращения интеграла. Такое выполнение устройства повыщает его точность.

Предлагаемый интегратор отличается также тем, что он содержит динамический триггер в цепи отрицательной обратной связи, которая соединяет выход накопителя с регистром, служащим нуль-органом, а в цепи ввода - счетчик входных приращений, связанный с помощью динамических триггеров с нуль-органом, и устройство совпадения, выход которого соедипен с шиной сброса счетчика. Это повышает быстродействие и надежность слежения.

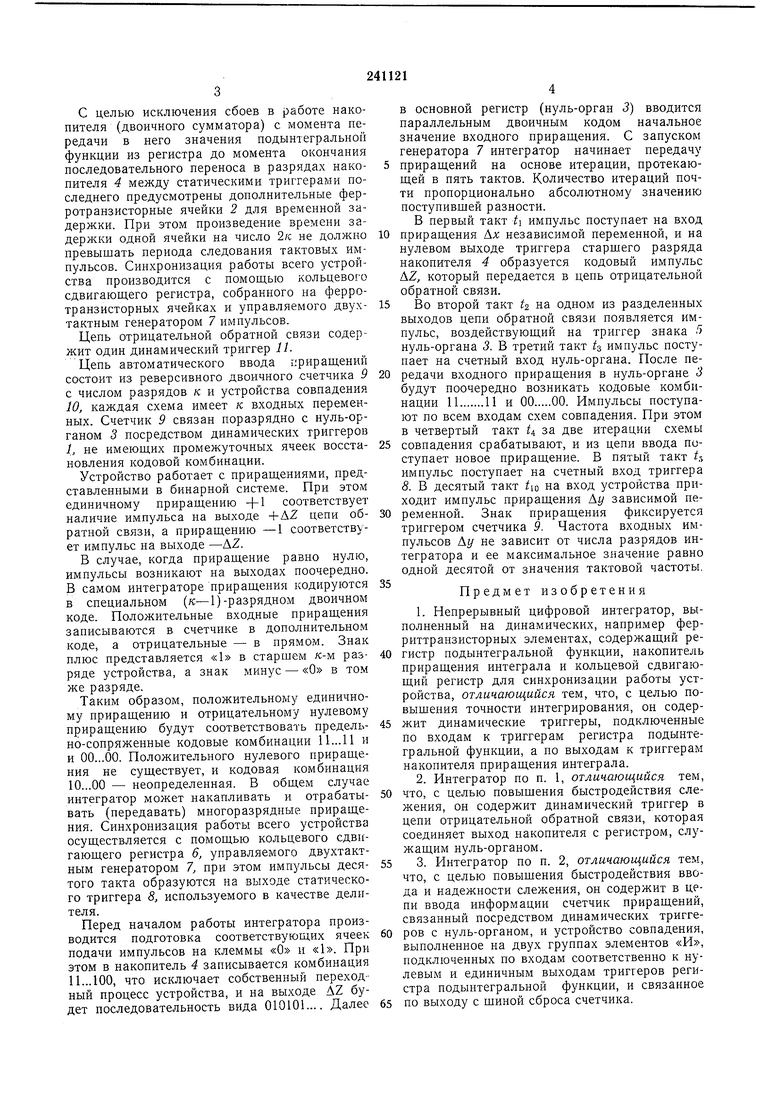

Он содержит динамические триггеры 1, ячейки 2 временной задержки, нуль-орган (устройство сравнения) 3, накопитель 4, триггеры знака 5, кольцевой сдвигающий регистр

6, генератор 7 импульсов, статический триггер 5, счетчик 5 и устройство совпадения 10. Основная часть интегратора содержит «: горизонтально расположенных динамических триггеров (к - ЧИСЛО двоичных разрядов регистра подынтегральной функции), сосгоящих из ферротранзисторных ячеек. Регистром подынтегральной функции является реверсивный двоичный счетчик, состоящий из к последовательно соединенных друг с другом ферротранзисторных статических триггеров. Поступающая на вход счетчика информация в виде единичных импульсов фиксируется в нем в виде нормального двоичного кода.

Счетчик управляется с помощью логических элементов «П.

Переключение с одного режима (суммирования) на другой (вычитание) производится триггером знака 5, собранного по обычной

полупроводниковой схеме на транзисторах. Коллекторный ток этих транзисторов подмагничивает ферротранзисторные ячейки логических элементов «И. Подмагничивание является необходимым условием работы устройС целью исключения сбоев в работе накопителя (двоичного сумматора) с момента передачи в него значения подынтегральной функции из регистра до момента окончания последовательного переноса в разрядах накопителя 4 между статическими триггерами последнего предусмотрены дополнительные ферротранзисторные ячейки 2 для временной задержки. При этом произведение времени задержки одной ячейки на число 2/с не должно превышать периода следования тактовых импульсов. Синхронизация работы всего устройства производится с помощью кольцевого сдвигающего регистра, собранного на ферротранзисторных ячейках и управляемого двухтактным генератором 7 импульсов.

Цепь отрицательной обратной связи содержит один динамический триггер 11.

Цепь автоматического ввода г;риращений состоит из реверсивного двоичного счетчика 9 с числом разрядов к и устройства совпадения 10, каждая схема имеет к входных переменных. Счетчик 9 связан поразрядно с нуль-органом 3 посредством динамических триггеро1з 1, не имеющих промежуточных ячеек восстановления кодовой комбинации.

Устройство работает с приращениями, представленными в бинарной системе. При этом единичному приращению +1 соответствует наличие импульса на выходе +AZ цепи обратной связи, а приращению -1 соответствует импульс на выходе -AZ.

В случае, когда приращение равно нулю, импульсы возникают на выходах поочередно. В самом интеграторе приращения кодируются в специальном (к-1)-разрядном двоичном коде. Положительные входные приращения записываются в счетчике в дополнительно.м коде, а отрицательные - в прямом. Знак плюс представляется «1 в старшем /с-м разряде устройства, а знак минус - «О в том же разряде.

Таким образом, положительному единичному приращению и отрицательному нулевому приращению будут соответствовать предельно-сопряженные кодовые комбинации И... 11 и и 00...00. Положительного нулевого приращения не существует, и кодовая комбинация 10...00 - неопределенная. В общем случае интегратор может накапливать и отрабатывать (передавать) многоразрядные приращения. Синхронизация работы всего устройства осуществляется с помощью кольцевого сдвигающего регистра 6, управляемого двухтактным генератором 7, при этом импульсы десятого такта образуются на выходе статического триггера 8, используемого в качестве делителя.

Перед началом работы интегратора производится подготовка соответствующих ячеек подачи импульсов на клеммы «О и «1. При этом в накопитель 4 записывается комбинация И...100, что исключает собственный переходный процесс устройства, и на выходе Az будет последовательность вида 010101.... Далее

в основной регистр (нуль-орган 3) вводится параллельным двоичным кодом начальное значение входного приращения. С запуском генератора 7 интегратор начинает передачу приращений на основе итерации, протекающей в пять тактов. Количество итераций почти пропорционально абсолютному значению поступивщей разности.

В первый такт ti импульс поступает на вход приращения Л.х независимой переменной, и на нулевом выходе триггера старшего разряда накопителя 4 образуется кодовый импульс AZ, который передается в цепь отрицательной обратной связи.

Во второй такт tz на одном из разделенных выходов цепи обратной связи появляется импульс, воздействующий на триггер знака ) нуль-органа 3. В третий такт 4 импульс поступает на счетный вход нуль-органа. После передачи входного приращения в нуль-органе 3 будут поочередно возникать кодовые комбинации 1111 и 0000. Импульсы поступают по всем входам схем совпадения. При этом в четвертый такт t за две итерации схемы совпадения срабатывают, и из цепи ввода поступает новое приращение. В пятый такт tимпульс поступает на счетный вход триггера 8. В десятый такт /ю на вход устройства приходит импульс приращения Ау зависимой переменной. Знак приращения фиксируется триггером счетчика 9. Частота входных импульсов Аг/ не зависит от числа разрядов интегратора и ее максимальное значение равно одной десятой от значения тактовой частоты.

Предмет изобретения

1.Непрерывный цифровой интегратор, выполненный на динамических, например ферриттранзисторных элементах, содержащий регистр подынтегральной функции, накопитель приращения интеграла и кольцевой сдвигающий регистр для синхронизации работы устройства, отличающийся тем, что, с целью повышения точности интегрирования, он содержит динамические триггеры, подключенные по входам к триггерам регистра подынтегральной функции, а по выходам к триггерам накопителя приращения интеграла.

2.Интегратор по п. 1, отличающийся тем, что, с целью повышения быстродействия слежения, он содержит динамический триггер в цепи отрицательной обратной связи, которая соединяет выход накопителя с регистром, служащим нуль-органом.

3.Интегратор по п. 2, отличающийся тем, что, с целью повышения быстродействия ввода и надежности слежения, он содержит в цепи ввода информации счетчик приращений, связанный посредством динамических триггеров с нуль-органом, и устройство совпадения, выполненное на двух группах элементов «И, подключенных по входам соответственно к нулевым и единичным выходам триггеров регистра подынтегральной функции, и связанное по выходу с щиной сброса счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮСЛЛЛ , HATwiiTIiO - <3>& iтг;:;и(«{?сг:! |•^U'iEKA I | 1964 |

|

SU164487A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Стереоавтограф | 1960 |

|

SU147841A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

Даты

1969-01-01—Публикация