Изобретение относится к области автоматики и вычислительной техники и может быть использовано в различных областях специального назначения.

Целью изобретения является упрощение технической реализации.

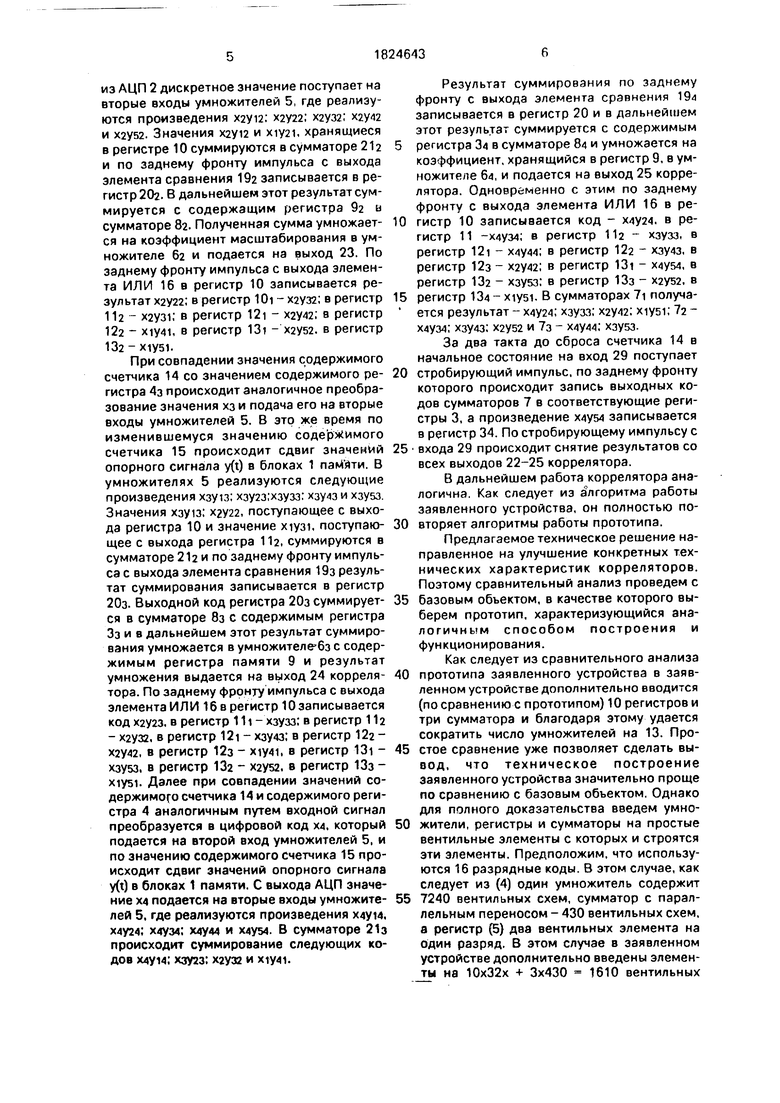

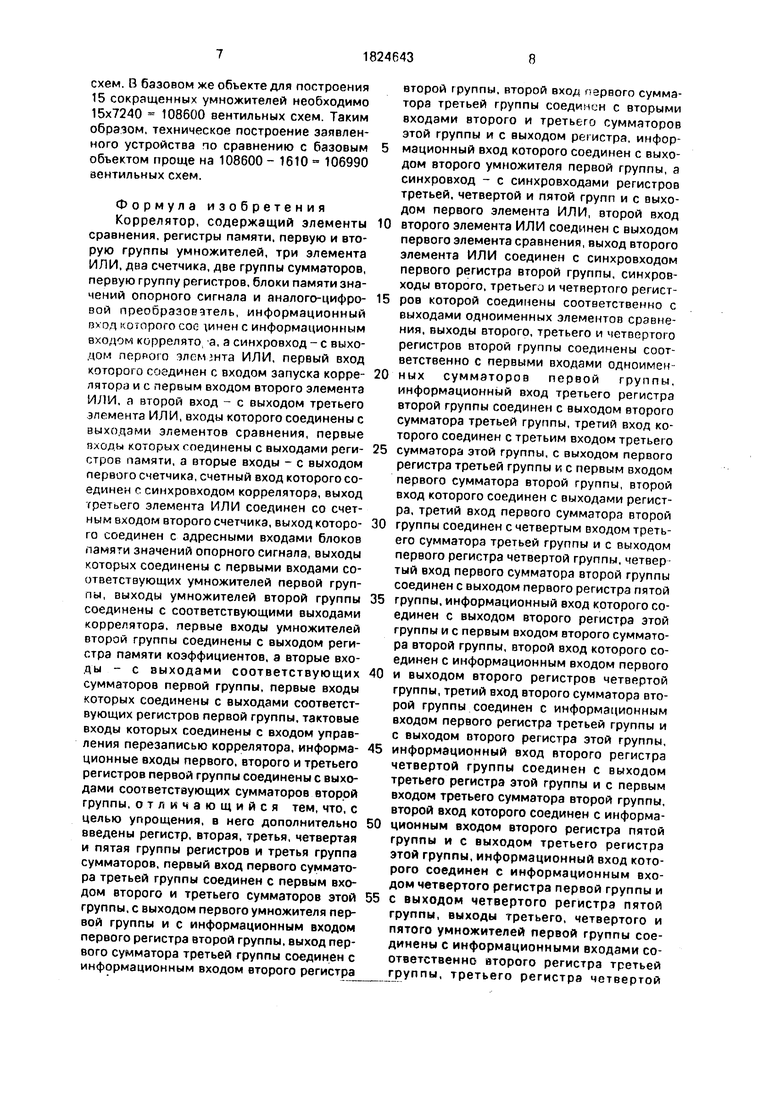

Структурная схема коррелятора приведена на чертеже.

Коррелятор содержит блоки памяти 1, аналого-цифровой преобразователь 2, первую группу регистров 3, регистры памяти 4, первую группу умножителей 5, вторую груп- лу умножителей 6, первую группу сумматоров 7, вторую группу сумматоров 8, регистр памяти коэффициентов 9, третью группу регистров 10, четвертую группу регистров 11, пятую группу регистров 12, шестую группу регистров 13, первый 14 и второй счетчики, первый 16, второй 17 и третий 18 элементы ИЛИ, элементы сравнения 19. вторую группу регистров 20, третью группу сумматороа 21, первый 22, второй 23, третий 24 и четвертый 25 выходы коррелятора, вход 26 синхронизации, информационный вход 27, вход запуска 28 и вход управления перезаписью 29.

Коррелятор работает следующим образом.

Работа коррелятора основана на использовании детерминированной неэквидистантной дискретизации.

Рассмотрим неэквидистантную дискри- тизацию эргодических сигналов x(t). y(t- t). Для этого представим отсчеты хд(т) и yA(t-t) в виде произведения непрерывных сигналов x(t) и y(t) на решетчатные функции Uli(t) и Ul2(t-t), состоящие из нерегулярных последовательностей единичных дельта-импульсов:

Uli(t)-S 5(t-tK) ,

К 0

00

1ЧЭ

Јь

к

00

LU2(t) I (5(t-t,c-lAt).

к o

Корреляционная функция СХуд() имеет вид

Схуд(1)- Hm (tMt-T)llJi(t)lil2(t-ifl

Т - оо

Учитывая, что процессы x(t) и y(t-r) независимы от UJi.2(t), получаем

л

0)

СХуд(г) llm {Cxy(i)Ci2(r). Т - оо

С корреляционной функцией Схуд однр- значно связана преобразованием Фурье спектральная мощность взаимодействия

5худ(1Д|)СхУД(1 At). Af-1/At откуда с учетом теоремы Планшереля имеем

SxW(lAfl- I m {Sxyffi Si2(lAf) (2) Т - оо

Из выражений (1) и (2) следует, что для получения насыщенной оценки SXy(f) по ди- скретнчм отсчетам сигналов {хд} и {уд} процессы дискретизации UJuW должны быть такими, чтобы при Т спектральная плотность §12(1 Af) стремилась к периодической последовательности дельта-импульсов с шагом A f 1/At. Это равносильно условию, чтобы оценка корреляционной Функции Ci2( A t) была определена для всех I 0,1,2,... и стремилась к постоянной

величине, не зависящей от г I At и Т:

1 lim Ci2(r,T)H

Т

Тогда значение Сху(г) определяется по формуле

Сху(г) ( т)

Требуемым свойством обладают периодические потоки LUn(t) с шагом дискретизации Ахи частотой Тди 1 /A t, а также стационарные стохастические процессы дискретизации Ш для которых при среднем интеграле между импульсами шд At и частоте Тд 1/Шд At ffli2 корреляционая функция равна:

i 1,2 lim Ci2(0) 1/шд; HmCi2(l At

Т - ооТ - оо

1/шд2

Очевидно, что максимальной величине шды соответствует одно совпадение при каждом изменении I на единицу

Ci2(i At) 1 /(пшди); пшди Т/ At

Импульсные потоки UJi,2(t) со свойством корреляционной функции Окно совпадение можно получитьдетерминированным способом, подобрав специальным образом расположение единичных импульсов на заданном отрезке Т - N A t.

Коррелятор работает следующим образом.

В блоки 11...1впамяти записываются дискретные значения опорного сигнала y(t)-(yn-yi5; ...;у51-у55) согласно значениям импульсного потока LLb(t). В регистры 41....44 записываются значения

импульсного потока UUi(t), Kg, K2, Кз и К« соответственно, значение Ki () не используется, так как при циклическом повторении . В регистр 9 записываются значения коэффициента масштабирования

1/N - At/T. Регистры 3, 20, 10, 11. 12, 13 обнуляются. Счетчик 14 работает с коэффициентом деления 1, счетчик 15 с коэффициентом деления п+1. При включении коррелятора на информационный вход 27

подается входной сигнал x(t), на вход 26 - последовательность импульсов тактовой частоты устройства, и один раз за все время работы коррелятора на вход 28 подается импульс запуска. Импульс с входа 28 через

элементы ИЛИ 16 и 17 подается на синхров- ход аналого-цифрового преобразователя 2, на синхровходы регистров 10... 13 и на син- хровход регистра 20i. По переднему фронту импульса аналого-цифровой преобразова

тель 2 производит преобразование сигнала x(t). Полученное дискретное значение xi, поступает на вторые входы умножителей 5, на выходы которых реализуются произведения xiyii, xjy2i: Х1уз1, xiy-ii и xiyoi. Результат

xiyn по заднему фронту импульса с выхода элемента ИЛИ 17 записывается в регистр 20i. В дальнейшем этот результат суммируется в сумматоре 8i с результатом, хранящимся в регистре 3i. умножается в

умножителе 6i на коэффициент, хранящийся в регистре 0, и выдается на выход 22 коррелятора. По заднему фронту импульса с выхода элемента ИЛИ 16 результат xiy2i записывается в регистр 10, результат xiyai

записывается в регистр 11i, результат xiy4i - в регистр 12i, а результат xiysi в регистр 13i.

При совпадении значений содержимого регистра 42 со значением содержимого счетчика 14 в элементе 192 сравнения вырабатывается импульс который проходит через элементы ИЛИ 18, увеличивает состояние счетчика 15 на единицу, проходит через элемент ИЛИ 16 и поступает на синхровходы

АЦП 2 и регистров 10, 11, 12. 13, а также поступает на синхровход регистра 202. В результате изменения содержимого счетчика 15 в блоках 1 памяти происходит сдвиг значений опорного сигнала y(t). Полученное

из АЦП 2 дискретное значение поступает на вторые входы умножителей 5, где реализуются ПрОИЗВедеНИЯ Х2У12. Х2У221 Х2У32; Х2У42

и Х2У52. Значения X2yi2 и xiy2i, хранящиеся в регистре 10 суммируются в сумматоре 212 и по заднему фронту импульса с выхода элемента сравнения 192 записывается в регистр 202. В дальнейшем этот результат суммируется с содержащим регистра 92 о сумматоре 82. Полученная сумма умножается на коэффициент масштабирования в умножителе 62 и подается на выход 23. По заднему фронту импульса с выхода элемента ИЛИ 16 в регистр 10 записывается результат Х2У22; в регистр 10i - Х2У32; в регистр 112 - Х2У31; в регистр 12i - Х2У42; в регистр 122 - xiy4i, в регистр 13i - Х2У52. в регистр

132-Х1У51.

При совпадении значения содержимого счетчика 14 со значением содержимого регистра 4з происходит аналогичное преобразование значения хз и подача его на вторые входы умножителей 5. В это же время по изменившемуся значению содержимого счетчика 15 происходит сдвиг значений опорного сигнала y(t) в блоках 1 памяти. В умножителях 5 реализуются следующие произведения хзуи; хзу2з;хзузз: хзу4э и хзувз. Значения хзутз; Х2У22, поступающее с выхода регистра 10 и значение xiysi, поступающее с выхода регистра 112, суммируются в сумматоре 212 и по заднему фронту импульса с выхода элемента сравнения 19з результат суммирования записывается в регистр 20з. Выходной код регистра 20з суммируется в сумматоре 8з с содержимым регистра Зз и в дальнейшем этот результат суммирования умножается в умножителе 6з с содержимым регистра памяти 9 и результат умножения выдается на выход 24 коррелятора. По заднему фронту импульса с выхода элемента ИЛИ 16 в регистр 10 записывается код Х2У23. в регистр 111 - хзузз: в регистр 112 - Х2У32, в регистр 12i - хзу4з; в регистр 122 - Х2У42, в регистр 12з - Х1У41, в регистр 13i - хзУ53. в регистр 13а - Х2У52. в регистр 13з - xiysi. Далее при совпадении значений содержимого счетчика 14 и содержимого регистра 4 аналогичным путем входной сигнал преобразуется в цифровой код Х4, который подается на второй вход умножителей 5, и по значению содержимого счетчика 15 происходит сдвиг значений опорного сигнала y(t) в блоках 1 памяти. С выхода АЦП значение х подается на вторые входы умножителей 5. где реализуются произведения Х4У14.

Х4У241 Х4У34; Х4У44 И Х4У54. В Сумматоре 21з

происходит суммирование следующих кодов Х4У14: хзузз: хауза и xiy4i.

Результат суммирования по заднему фронту с выхода элемента сравнения 194 записывается в регистр 20 и в дальнейшем этот результат суммируется с содержимым

регистра 34 в сумматоре 84 и умножается на коэффициент, хранящийся в регистр 9. в умножителе 64, и подается на выход 25 коррелятора. Одновременно с этим по заднему фронту с выхода элемента ИЛИ 16 в ре0 гистр 10 записывается код - Х4У24. в регистр 11 -Х4У34; в регистр 112 - хзузз, в регистр 121 - Х4У44; в регистр 122 - хзу4з, в

регистр 12з - Х2У421 В регистр 131 - Х4У54, В регистр 132 - ХЗУ53: В реГИСТр 13з - Х2У52, В

5 регистр 134 xiysi. В сумматорах 7i получа- ется результат - Х4У24; хзузз; Х2У42: xiysi; li Х4У341 ХЗУ43; Х2У52 И 7з - Х4У44, ХЗУ53.

За два такта до сброса счетчика 14 в начальное состояние на вход 29 поступает

0 стробирующий импульс, по заднему фронту которого происходит запись выходных кодов сумматоров 7 в соответствующие регистры 3, а произведение Х4У54 записывается в регистр 34. По стробирующему импульсу с

5 входа 29 происходит снятие результатов со всех выходов 22-25 коррелятора.

В дальнейшем работа коррелятора аналогична. Как следует из алгоритма работы заявленного устройства, он полностью по0 вторяет алгоритмы работы прототипа.

Предлагаемое техническое решение направленное на улучшение конкретных технических характеристик корреляторов. Поэтому сравнительный анализ проведем с

5 базовым объектом, в качестве которого выберем прототип, характеризующийся аналогичным способом построения и функционирования.

Как следует из сравнительного анализа

0 прототипа заявленного устройства в заявленном устройстве дополнительно вводится (по сравнению с прототипом) 10 регистров и три сумматора и благодаря этому удается сократить число умножителей на 13. Про5 стое сравнение уже позволяет сделать вывод, что техническое построение заявленного устройства значительно проще по сравнению с базовым объектом. Однако для полного доказательства введем умно0 жители, регистры и сумматоры на простые вентильные элементы с которых и строятся эти элементы. Предположим, что используются 16 разрядные коды. В этом случае, как следует из (4) один умножитель содержит

5 7240 вентильных схем, сумматор с параллельным переносом - 430 вентильных схем. а регистр (5) два вентильных элемента на один разряд. В этом случае в заявленном устройстве дополнительно введены элементы на 10х32х + 3x430 1610 вентильных

схем. В базовом же объекте для построения 15 сокращенных умножителей необходимо 15x7240 108600 вентильных схем. Таким образом, техническое построение заявленного устройства по сравнению с базовым объектом проще на 108600 - 1610 - 106990 вентильных схем.

Формула изобретения Коррелятор, содержащий элементы сравнений, регистры памяти, первую и вторую группы умножителей, три элемента ИЛИ, два счетчика, две группы сумматоров, первую группу регистров, блоки памяти значений опорного сигнала и аналого-цифровой преобразователь, информационный вход которого сое инен с информационным входом коррелято, а, а синхровход - с выходом лерпого элемента ИЛИ, первый вход которого соединен с входом запуска коррелятора и с первым входом второго элемента ИЛИ, а второй вход - с выходом третьего элемента ИЛИ, входы которого соединены с выходами элементов сравнения, первые плоды которых соединены с выходами регистров памяти, а вторые входы - с выходом первого счетчика, счетный вход которого соединен с синхровходом коррелятора, выход третьего элемента ИЛИ соединен со счетным входом второго счетчика, выход которого соединен с адресными входами блоков памяти значений опорного сигнала, выходы которых соединены с первыми входами соответствующих умножителей первой группы, выходы умножителей второй группы соединены с соответствующими выходами коррелятора, первые входы умножителей второй группы соединены с выходом регистра памяти коэффициентов, а вторые входы - с выходами соответствующих сумматоров первой группы, первые входы которых соединены с выходами соответствующих регистров первой группы, тактовые входы которых соединены с входом управления перезаписью коррелятора, информационные входы первого, второго и третьего регистров первой группы соединены с выходами соответствующих сумматоров второй группы, отличающийся тем, что, с целью упрощения, в него дополнительно введены регистр, вторая, третья, четвертая и пятая группы регистров и третья группа сумматоров, первый вход первого сумматора третьей группы соединен с первым входом второго и третьего сумматоров этой группы, с выходом первого умножителя первой группы и с информационным входом первого регистра второй группы, выход первого сумматора третьей группы соединен с информационным входом второго регистра

второй группы, второй вход первого сумматора третьей группы соединен с вторыми входами второго и третьего сумматоров этой группы и с выходом регистра, инфор5 мационный вход которого соединен с выходом второго умножителя первой группы, а синхровход - с синхровходами регистров третьей, четвертой и пятой групп и с выходом первого элемента ИЛИ, второй вход

0 второго элемента ИЛИ соединен с выходом первого элемента сравнения, выход второго элемента ИЛИ соединен с синхровходом первого регистра второй группы, синхров- ходы второго, третьего и четвертого регист5 ров которой соединены соответственно с выходами одноименных элементов сравнения, выходы второго, третьего и четвертого регистров второй группы соединены соответственно с первыми входами одноимен

0 ных сумматоров первой группы, информационный вход третьего регистра второй группы соединен с выходом второго сумматора третьей группы, третий вход которого соединен с третьим входом третьего

5 сумматора этой группы, с выходом первого регистра третьей группы и с первым входом первого сумматора второй группы, второй вход которого соединен с выходами регистра, третий вход первого сумматора второй

0 группы соединен с четвертым входом третьего сумматора третьей группы и с выходом первого регистра четвертой группы, четвертый вход первого сумматора второй группы соединен с выходом первого регистра пятой

5 группы, информационный вход которого соединен с выходом второго регистра этой группы и с первым входом второго сумматора второй группы, второй вход которого соединен с информационным входом первого

0 и выходом второго регистров четвертой группы, третий вход второго сумматора второй группы соединен с информационным входом первого регистра третьей группы и с выходом второго регистра этой группы,

5 информационный вход второго регистра четвертой группы соединен с выходом третьего регистра этой группы и с первым входом третьего сумматора второй группы, второй вход которого соединен с информа0 ционным входом второго регистра пятой группы и с выходом третьего регистра этой группы, информационный вход которого соединен с информационным входом четвертого регистра первой группы и

5 с выходом четвертого регистра пятой группы, выходы третьего, четвертого и пятого умножителей первой группы соединены с информационными входами соответственно второго регистра третьей

группы, третьего регистра четвертой

группы и четвертого регистра пятой группысоединен с втопыми входами умножитрлей

выход аналого-цифрового преобразователя первой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Коррелометр | 1988 |

|

SU1550532A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Устройство для измерения динамических характеристик | 1983 |

|

SU1168902A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Коррелометр | 1985 |

|

SU1292007A1 |

| Устройство для оценки точности вычислений | 1990 |

|

SU1830532A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1439619A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в различных областях специального назначения. Цель изобретения - упрощение коррелятора. Коррелятор содержит блоки памяти, аналого-цифровой преобразователь, группы регистров, регистры памяти, блоки памяти значений опорного сигнала, группы умножителей, группы сумматоров, счетчики, элементы, элементы сравнения.1 ил. w fe

-i

&

J

/8

JT

fТВ

LQI

Г

2926

| Авторское свидетельство СССР № 980101, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коррелометр | 1983 |

|

SU1091173A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коррелометр | 1985 |

|

SU1292007A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Лощилов И.И | |||

| Перспективы роста производительности ЭВМ | |||

| - Зарубежная радиоэлектроника, № 5 | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Радиотехника и электроника,1980,№ 9, с.1902. | |||

Авторы

Даты

1993-06-30—Публикация

1991-01-09—Подача