о

со

С

43.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР СИНУСОИДАЛЬНЫХ СИГНАЛОВ | 1991 |

|

RU2010414C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АМПЛИТУДНО-ЧАСТОТНОЙ ХАРАКТЕРИСТИКИ ТРАКТА СВЯЗИ | 1992 |

|

RU2069935C1 |

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Частотный детектор | 1982 |

|

SU1137563A1 |

| Устройство записи видеоинформации | 1989 |

|

SU1721840A1 |

| Дельта-модулятор | 1990 |

|

SU1718383A1 |

| Цифровой синтезатор частот | 1988 |

|

SU1566454A1 |

| Устройство для разделения направлений передачи и приема | 1989 |

|

SU1734220A1 |

Использование - радиотехника для демодуляции частотномодулированных сигналов. Сущность изобретения: цифровой частотный детектор содержит формирователь 1 импульсов, блок 2 управления, генератор 3 импульсов, реверсивные счетчики 4, 5, блоки 6, 7 памяти, источник 8 опорного напряжения, цифроаналоговые преобразователи 9, 10, блок 11 вычитания, фильтр 12 нижних частот. 1 ил.

00

ю

XI

VI

О О

Изобретение относится к радиотехнике и может быть использовано для демодуляции частотномодулированных сигналов.

Цель изобретения -увеличениеточности детектирования путем стабилизации нулевой точки дискриминационной характеристики.

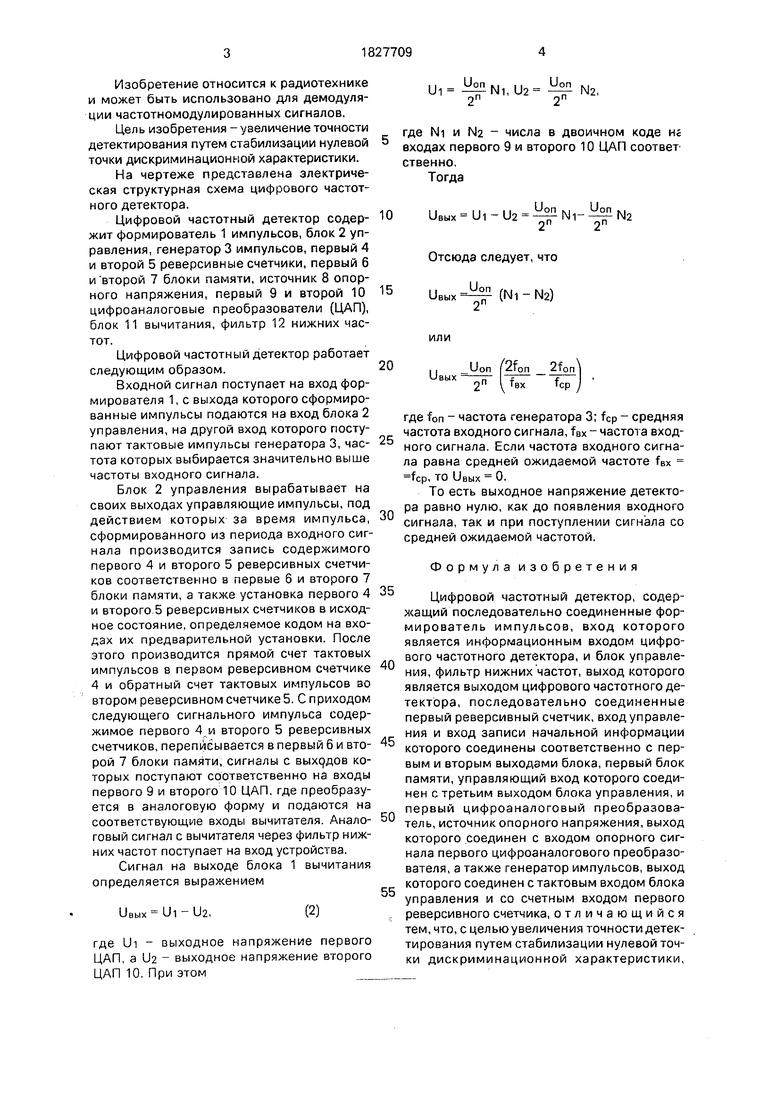

На чертеже представлена электрическая структурная схема цифрового частотного детектора.

Цифровой частотный детектор содержит формирователь 1 импульсов, блок 2 управления, генератор 3 импульсов, первый 4 и второй 5 реверсивные счетчики, первый 6 и второй 7 блоки памяти, источник 8 опорного напряжения, первый 9 и второй 10 цифроаналоговые преобразователи (ЦАП), блок 11 вычитания, фильтр 12 нижних частот.

Цифровой частотный детектор работает следующим образом.

Входной сигнал поступает на вход формирователя 1, с выхода которого сформированные импульсы подаются на вход блока 2 управления, на другой вход которого поступают тактовые импульсы генератора 3, частота которых выбирается значительно выше частоты входного сигнала.

Блок 2 управления вырабатывает на своих выходах управляющие импульсы, под действием которых за время импульса, сформированного из периода входного сигнала производится запись содержимого первого 4 и второго 5 реверсивных счетчиков соответственно в первые 6 и второго 7 блоки памяти, а также установка первого 4 и второго 5 реверсивных счетчиков в исходное состояние, определяемое кодом на входах их предварительной установки. После этого производится прямой счет тактовых импульсов в первом реверсивном счетчике 4 и обратный счет тактовых импульсов во втором реверсивном счетчике 5. С приходом следующего сигнального импульса содержимое первого 4 и второго 5 реверсивных счетчиков, переписывается в первый 6 и второй 7 блоки памяти, сигналы с вых9дов которых поступают соответственно на входы первого 9 и второго 10 ЦАП, где преобразуется в аналоговую форму и подаются на соответствующие входы вычитателя. Аналоговый сигнал с вычитателя через фильтр нижних частот поступает на вход устройства.

Сигнал на выходе блока 1 вычитания определяется выражением

UBblx Ul-U2,

(2)

где Ui - выходное напряжение первого ЦАП, a U2 - выходное напряжение второго ЦАП 10. При этом

щ ,U2 Uon

2п

2п

N2,

5 где NI и N2 - числа в двоичном коде иг входах первого 9 и второго 10 ЦАП соответ ственно, Тогда

10 u.b«-U, Отсюда следует, что

15UBb,x(Ni-N2)

2П

N2

или

UE

Uon f2f,

2П lf

2f0

rep

где ton - частота генератора 3; fcp - средняя частота входного сигнала, fBx - частота входного сигнала. Если частота входного сигнала равна средней ожидаемой частоте fBx fcp, то ивых 0.

То есть выходное напряжение детектора равно нулю, как до появления входного сигнала, так и при поступлении сигнала со средней ожидаемой частотой.

Формула изобретения

Цифровой частотный детектор, содержащий последовательно соединенные формирователь импульсов, вход которого является информационным входом цифро- вого частотного детектора, и блок управления, фильтр нижних частот, выход которого является выходом цифрового частотного детектора, последовательно соединенные первый реверсивный счетчик, вход управления и вход записи начальной информации которого соединены соответственно с первым и вторым выходами блока, первый блок памяти, управляющий вход которого соединен с третьим выходом блока управления, и первый цифроаналоговый преобразователь, источник опорного напряжения, выход которого соединен с входом опорного сигнала первого цифроаналогового преобразователя, а также генератор импульсов, выход которого соединен с тактовым входом блока управления и со счетным входом первого реверсивного счетчика, отличающийся тем, что, с целью увеличения точности детектирования путем стабилизации нулевой точки дискриминационной характеристики,

введены последовательно соединенные второй реверсивный счетчик, счетный вход и вход управления счетом и вход записи начальной информации соединены соответственно с выходом генератора импульсов и с первым и вторым выходами блока управления, второй блок памяти, управляющий вход которого соединен с третьим выходом блока управления, второй цифроаналого- вый преобразователь, вход опорного сигнала которого соединен с выходом источника

0

опорного напряжения, и блок вычитания, второй вход которого соединен с выходом первого цифроаналогового преобразователя, а выход - соединен с входом фильтра нижних частот, при этом входы кода предварительной установки и входы установки в О первого и второго реверсивных счетчиков, а также входы установки в О первого и второго блоков памяти являются управляющими входами цифрового частотного детектора.

| УСТРОЙСТВО ДЛЯ АЭРАЦИИ ЖИДКОСТИ | 2003 |

|

RU2236306C1 |

Авторы

Даты

1993-07-15—Публикация

1991-01-08—Подача