Изобретение относится к вычислительной технике и микроэлектронике, и может быть использовано для построения арифметических устройств, работающих в системе остаточных классов.

Цель изобретения - повышение быстродействия сумматора по модулю пять.

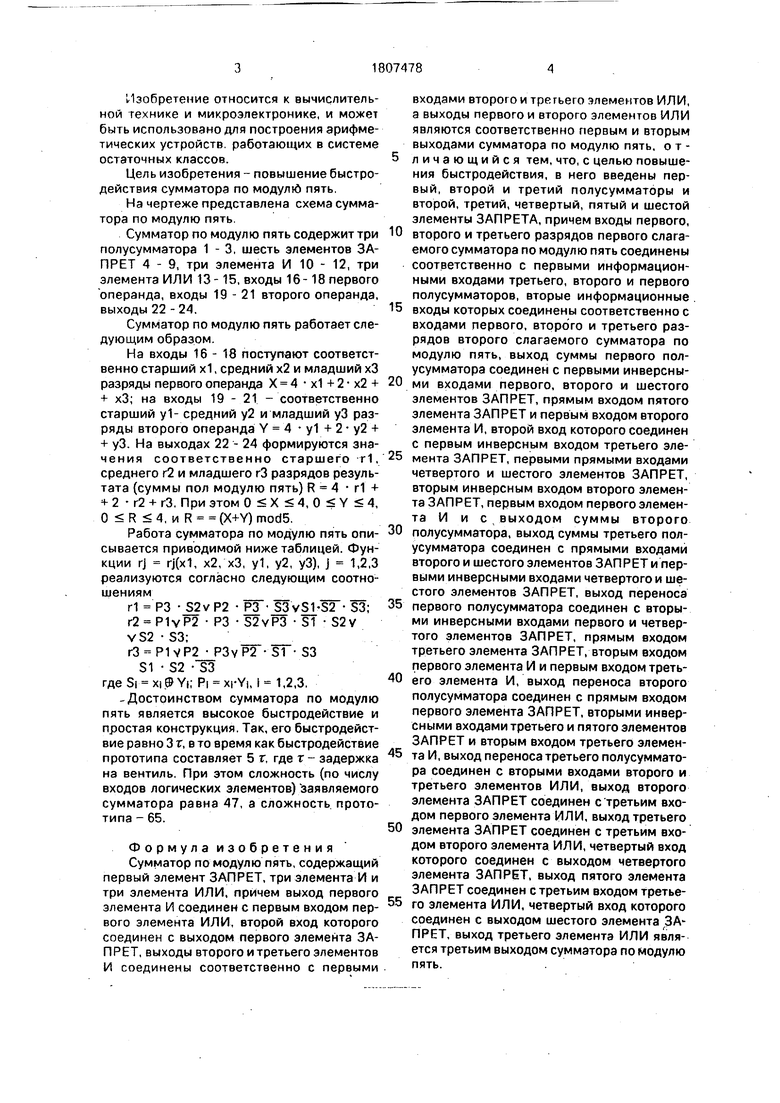

На чертеже представлена схема сумматора по модулю пять.

Сумматор по модулю пять содержит три полусумматора 1-3, шесть элементов ЗАПРЕТ 4 - 9, три элемента И 10 - 12, три элемента ИЛ И 13-15, входы 16-18 первого операнда, входы 19-21 второго операнда, выходы 22 - 24.

Сумматор по модулю пять работает следующим образом.

На входы 16-18 поступают соответственно старший х1, средний х2 и младший хЗ разряды первого операнда X 4 х1 + 2 х2 + + хЗ; на входы 19 - 21 - соответственно старший у1- средний у2 и младший уЗ разряды второго операнда Y 4 у1 + 2 у2 + + уЗ. На выходах 22 - 24 формируются зна- чения соответственно старшего т1, среднего г2 и младшего гЗ разрядов результата (суммы пол модулю пять) R 4 М + + 2 г2 + гЗ, При этом , , , иЯ (X+Y) mod5.

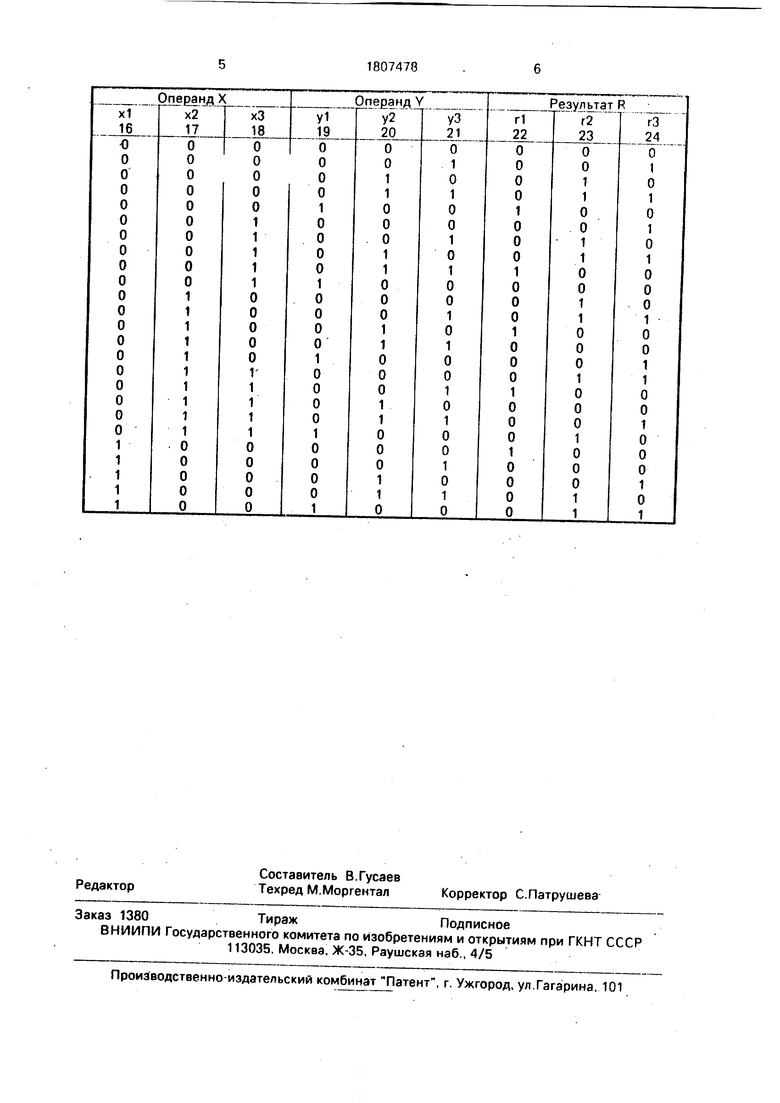

Работа сумматора по модулю пять описывается приводимой ниже таблицей. Функции rj rj(x1, х2, хЗ, у1, у2, уЗ), j 1,2,3 реализуются согласно следующим соотношениям

г1 РЗ -S2vP2 РЗ .S3VS1/S2 S3;

r2 P1vP2 РЗ S2vP3 S1 S2V

VS2 S3;

гЗ Р1 V P2 S1 S3

S1 S2 S3 где5г х|ФУ|,- PI XI-YI, 1 1,2,3.

-Достоинством сумматора по модулю пять является высокое быстродействие и простая конструкция. Так, его быстродействие равно 3 г, в то время как быстродействие прототипа составляет 5 г, где т - задержка на вентиль. При этом сложность (по числу входов логических элементов) заявляемого сумматора равна 47, а сложность прототипа - 65.

Ф о р м у л а и з о б р е т е н и я Сумматор по модулю пять, содержащий первый элемент ЗАПРЕТ, три элемента И и три элемента ИЛИ, причем выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента ЗАПРЕТ, выходы второго и третьего элементов И соединены соответственно с первыми

входами второго и третьего элементов ИЛИ, а выходы первого и второго элементов ИЛИ являются соответственно первым и вторым выходами сумматора по модулю пять, о т личающийся тем, что, с целью повышения быстродействия, в него введены первый, второй и третий полусумматоры и второй, третий, четвертый, пятый и шестой элементы ЗАПРЕТА, причем входы первого,

второго и третьего разрядов первого слагаемого сумматора по модулю пять соединены соответственно с первыми информационными входами третьего, второго и первого полусумматоров, вторые информационные

входы которых соединены соответственно с входами первого, второго и третьего разрядов второго слагаемого сумматора по модулю пять, выход суммы первого полусумматора соединен с первыми инверсными входами первого, второго и шестого элементов ЗАПРЕТ, прямым входом пятого элемента ЗАПРЕТ и первым входом второго элемента И, второй вход которого соединен с первым инверсным входом третьего элемента ЗАПРЕТ, первыми прямыми входами четвертого и шестого элементов ЗАПРЕТ, вторым инверсным входом второго элемента ЗАПРЕТ, первым входом первого элемента И и с выходом суммы второго

полусумматора, выход суммы третьего полусумматора соединен с прямыми входами второго и шестого элементов ЗАПРЕТИ первыми инверсными входами четвертого и шестого элементов ЗАПРЕТ, выход переноса

первого полусумматора соединен с вторыми инверсными входами первого и четвертого элементов ЗАПРЕТ, прямым входом третьего элемента ЗАПРЕТ, вторым входом первого элемента И и первым входом третьего элемента И, выход переноса второго полусумматора соединен с прямым входом первого элемента ЗАПРЕТ, вторыми инверсными входами третьего и пятого элементов ЗАПРЕТ и вторым входом третьего элемента И, выход переноса третьего полусумматора соединен с вторыми входами второго и третьего элементов ИЛИ, выход второго элемента ЗАПРЕТ соединен с третьим входом первого элемента ИЛИ, выход третьего

элемента ЗАПРЕТ соединен с третьим входом второго элемента ИЛИ, четвертый вход которого соединен с выходом четвертого элемента ЗАПРЕТ, выход пятого элемента ЗАПРЕТ соединен с третьим входом третьего элемента ИЛИ, четвертый вход которого соединен с выходом шестого элемента ЗАПРЕТ, выход третьего элемента ИЛИ является третьим выходом сумматора по модулю пять.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю пять | 1991 |

|

SU1783514A1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1837280A1 |

| Устройство для подсчета числа единиц | 1988 |

|

SU1730621A1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1797110A1 |

| Устройство для подсчета числа единиц | 1988 |

|

SU1658146A1 |

| Сумматор по модулю пять | 1991 |

|

SU1803911A1 |

| Сумматор по модулю три | 1991 |

|

SU1830528A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для деления чисел | 1990 |

|

SU1795456A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах, работающих в системе остаточных классов. Цель изобретения - повышение быстродействия. Сумматор по модулю пять содержит три полусумматора 1-3, шесть элементов ЗАПРЕТ 4-9, три элемента И 10 - 12 и три элемента ИЛИ 13 -15, соединенные между собой функционально, 1 ил., 1 табл.

| Сумматор по модулю три | 1986 |

|

SU1381488A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сумматор по модулю пять | 1988 |

|

SU1566342A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-04-07—Публикация

1991-02-25—Подача