Изобретение относится к вычислительной технике и может быть использовано для построения арифметических устройств, работающих в системе остаточных классов.

Известен сумматор по модулю Р. содержащий четыре элемента И, два элемента ИЛИ, дешифратор, регистры, схему сравнения, счетчик 1.

Недостатком сумматора является его конструктивная сложность и низкое быстродействие.

Наиболее близким по технической сущности к предложенном / является сумматор по модулю пять, содержащий четырнадцать элементов И, девять элементов ИЛИ. три элемента ИЛИ-НЕ, элемент И-НЕ и элемент ЗАПРЕТА 2.

Недостатком известного сумматора по модулю пять является его высокая конструктивная сложность.

Цель изобретения - упрощение конструкции.

Предлагаемый сумматор по модулю пять содержит первый, второй и третий элементы илИ-НЕ,злемент ЗАПРЕТА, элемент И и элемент ИЛИ, первый вход которого

соединен с выходом элемента И, выход элемента ЗАПРЕТА соединен с вторым входом элемента ИЛИ, выход которого соединен с третьим разрядным выходом сумматора. Для достижения поставленной цели в устройство введены четвертый и пятый элементы ИЛИ-НЕ и первый, второй, третий и четвертый полусумматоры, причем первый, второй и третий разряды входа первого слагаемого соединены соответственно с первыми информационными входами третьего, второго и первого полусумматоров, вторые информационные входы которых соединены соответственно с первым, вторым и третьим разрядами входа второго слагаемого. Выход переноса первого полусумматора и выход суммы второго полусумматора соединены соответственно с первым и вторым информационными входами четвертого полусумматора. Выходы переноса четвертого и второго полусумматоров соединены с первым и вторым входами первого элемента ИЛИ-НЕ, третий вход которого соединен с выходом суммы третьего полусумматора. Выходы суммы первого и четвертого полусумматоров соединены с первым и вторым

Ч 00

со ел

Ј

входами второго элемента ИЛИ-НЕ, третий вход которого соединен с первыми входами третьего элемента ИЛИ-НЕ и элемента И, первым инверсным входом элемента ЗАПРЕТА и выходом первого элемента ИЛИ- 5 НЕ. Выход суммы первого полусумматора соединен с вторыми входами третьего элемента ИЛИ-НЕ и элемента И и с вторым инверсным входом элемента ЗАПРЕТА. Выход суммы четвертого полусумматора сое- 10 динен с первым входом четвертого элемента ИЛИ-НЕ и прямым входом элемента ЗАПРЕТА, выход переноса третьего полусумматора соединен со вторым входом четвертого элемента ИЛИ-НЕ и с третьим 15 входом элемента ИЛИ. Выходы третьего и четвертого элементов ИЛИ-НЕ соединены с первым и вторым входами пятого элемента ИЛИ-НЕ, выход которого соединен со вторым разрядным выходом сумматора, пер- 20 вый разрядный выход которого соединен с выходом второго элемента ИЛИ-НЕ.

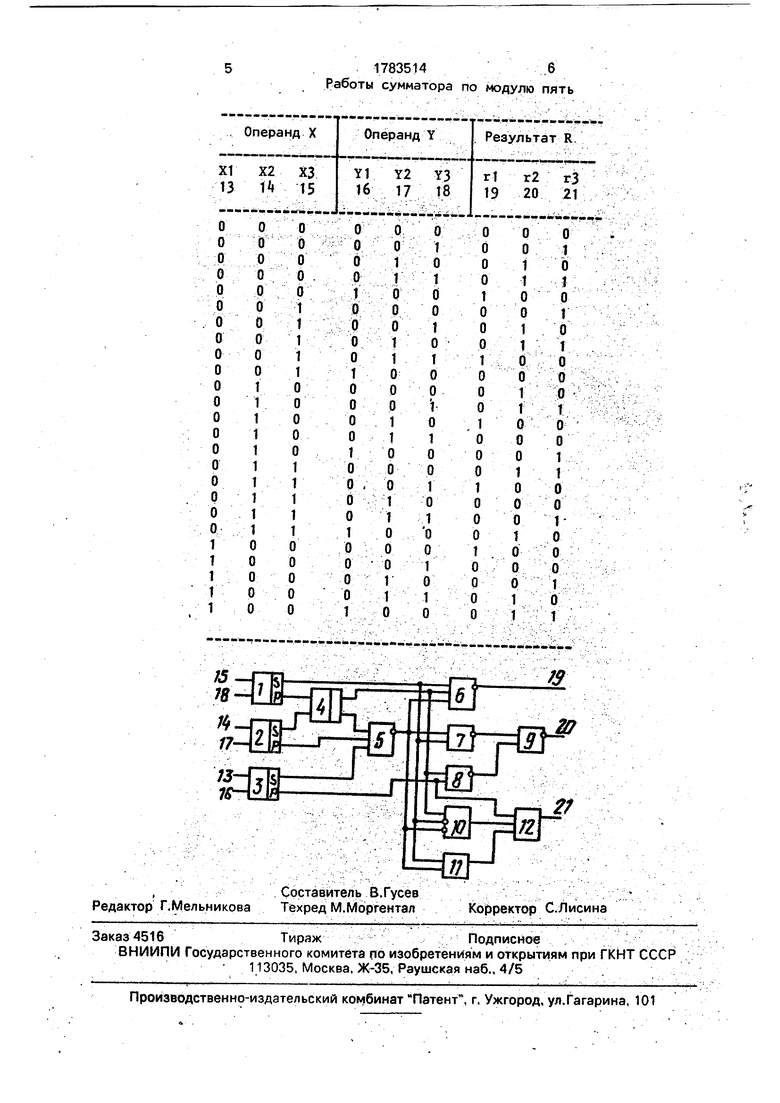

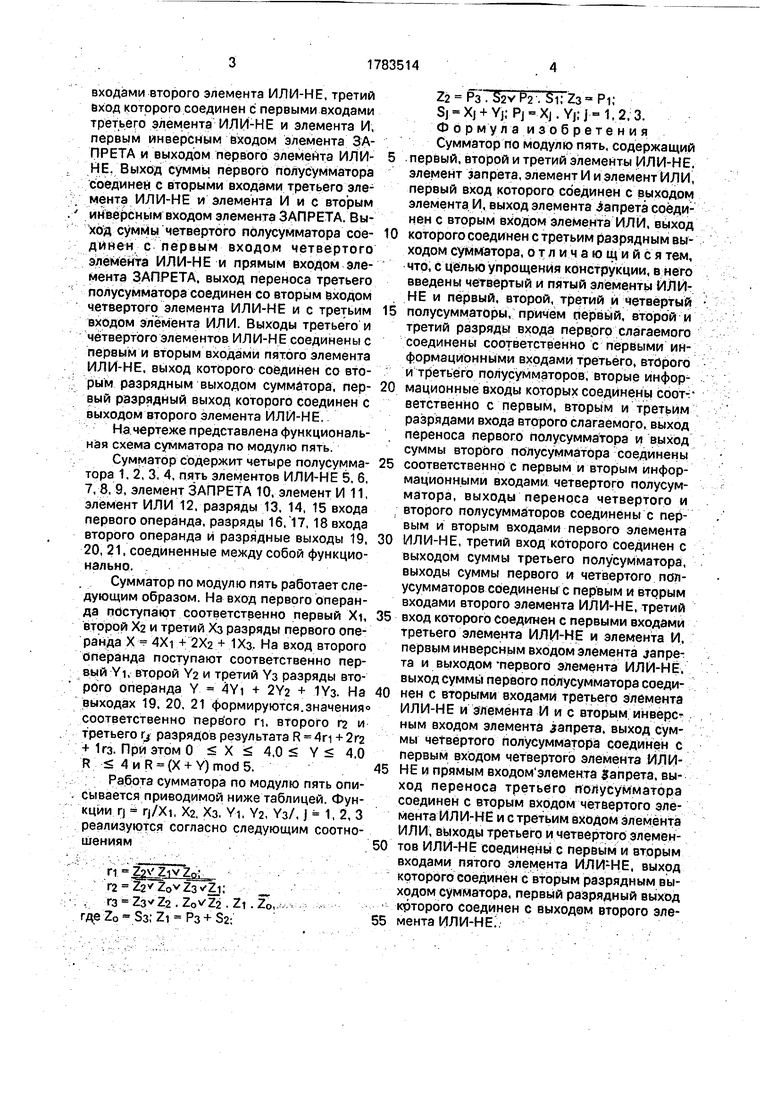

На чертеже представлена функциональная схема сумматора по модулю пять.

Сумматор содержит четыре полусумма- 25 тора 1, 2, 3, 4, пять элементов ИЛИ-НЕ 5, б, 7,8. 9, элемент ЗАПРЕТА 10, элемент И 11, элемент ИЛИ 12, разряды 13. 14, 15 входа первого операнда, разряды 16,17, 18 входа второго операнда и разрядные выходы 19, 30 20, 21, соединенные между собой функционально.

Сумматор по модулю пять работает следующим образом. На вход первого операнда поступают соответственно первый Xi, 35 второй Х2 и третий Хз разряды первого операнда X 4Xi + 2X2 + 1Хз. На вход второго операнда поступают соответственно первый YI, второй Y2 и третий Уз разряды вто- рОго операнда Y 4Yi + 2Y2 + 1Ys. На 40 выходах 19. 20, 21 формируются.значения соответственно перв ого п. второго п и третьего tj разрядов результата R 4п + 2Г2 + 1гз. При этом 0 X 4.0 Y 4,0 R 4 и R (X + Y) mod 5.45

Работа сумматора по модулю пять опи- . сывается приводимой ниже таблицей. Функции rj - rj/Xi, X2. Хз. Yi. Y2, Уз/, j 1, 2, 3 реализуются согласно следующим соотношениям50

n°Zg ZivZo:

Г2 Z2 ZovZ3vZj;

гз . Z0vZ2 Zi. Z0,

где Z0 - Ss; Zi Рз + S2:

0 5 0

5 0

5 0 5

0

5

Z2 Рз . S2V P2 . Si; Zs Pi;

Sj Xj + Yj;Pj Xj.Yj;j 1,2.3.

Формула изобретения

Сумматор по модулю пять, содержащий первый, второй и третий элементы ИЛИ-НЕ. элемент запрета, элемент И и элемент ИЛИ, первый вход которого соединен с выходом элемента И, выход элемента запрета соединен с вторым входом элемента ИЛИ, выход которого соединен с третьим разрядным выходом сумматора, отличающийся тем, что, с целью упрощения конструкции, в него введены четвертый и пятый элементы ИЛИ- НЕ и первый, второй, третий и четвертый полусумматоры, причем первый, второй и третий разряды входа перврго слагаемого соединены соответственно с первыми информационными входами третьего, второго и третьего полусумматоров, вторые информационные входы которых соединены соответственно с первым, вторым и третьим разрядами входа второго слагаемого, выход переноса первого полусумматора и выход суммы второго полусумматора соединены соответственно с первым и вторым информационными входами четвертого полусумматора, выходы переноса четвертого и второго полусумматоров соединены с первым и вторым входами первого элемента ИЛИ-НЕ, третий вход которого соединен с выходом суммы третьего полусумматора, выходы суммы первого и четвертого полусумматоров соединены с первым и вторым входами второго элемента ИЛИ-НЕ, третий вход которого соединен с первыми входами третьего элемента ИЛИ-НЕ и элемента И, первым инверсным входом элемента janpe- та и выходом -первого элемента ИЛИ-НЕ. выход суммы первого полусумматора соединен с вторыми входами третьего элемента ИЛИ-НЕ и элемента И и с вторым инверсным входом элемента запрета, выход суммы четвертого полусумматора соединен с первым входом четвертого элемента ИЛИ- НЕ и прямым входом элемента Запрета, выход переноса третьего полусумматора соединен с вторым входом четвертого элемента ИЛИ-НЕ и с третьим входом элемента ИЛИ, выходы третьего и четвертого элементов ИЛИ-НЕ соединены с первым и вторым входами пятого элемента ИЛИ1НЕ. выход которого соединен с вторым разрядным выходом сумматора, первый разрядный выход крторого соединен с выходом второго элемента ИЛИ-НЕ.

17835146

Работы сумматора по модулю пять

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подсчета числа единиц | 1989 |

|

SU1837280A1 |

| Сумматор по модулю пять | 1991 |

|

SU1807478A1 |

| Сумматор по модулю пять | 1991 |

|

SU1803911A1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1797110A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для умножения | 1987 |

|

SU1411733A1 |

| МНОГОВЫХОДНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2613536C1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Устройство для подсчета числа единиц | 1988 |

|

SU1730621A1 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

Изобретение относится к вычислительной технике и может быть использована для построения арифметических устройств, работающих в системе остаточных классов. Цель изобретения - упрощение конструкции. Сумматор по модулю пять содержит четыре полусумматора 1, 2, 3, 4, пять элементов ИЛИ-НЕ 5,6,7,8, элемент ЗАПРЕТА 10, элемент И 11 и элемент ИЛИ 12, соединенные между собой функционально. 1 ил , 1 табл.

| Устройство для сложения и вычитания чисел по модулю @ | 1983 |

|

SU1168934A1 |

| Сумматор по модулю пять | 1988 |

|

SU1566342A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-23—Публикация

1991-02-19—Подача