Изобретение относится к области автоматики и вычислительной техники, как средство для преобразования информации, и может быть использовано при построении прецизионных цифровых измерительных систем, преимущественно для океанографических исследований.

Целью изобретения является повышение быстродействия и точности преобразования за счет исключения потери информации при обнулении интегратора.

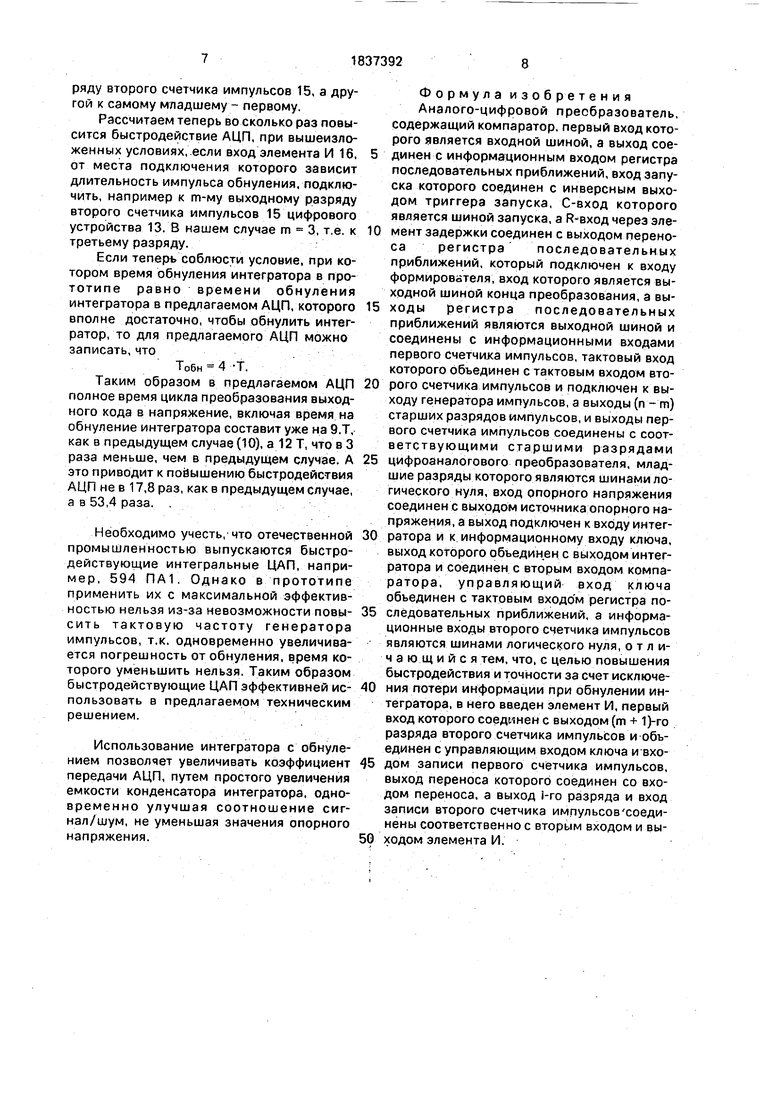

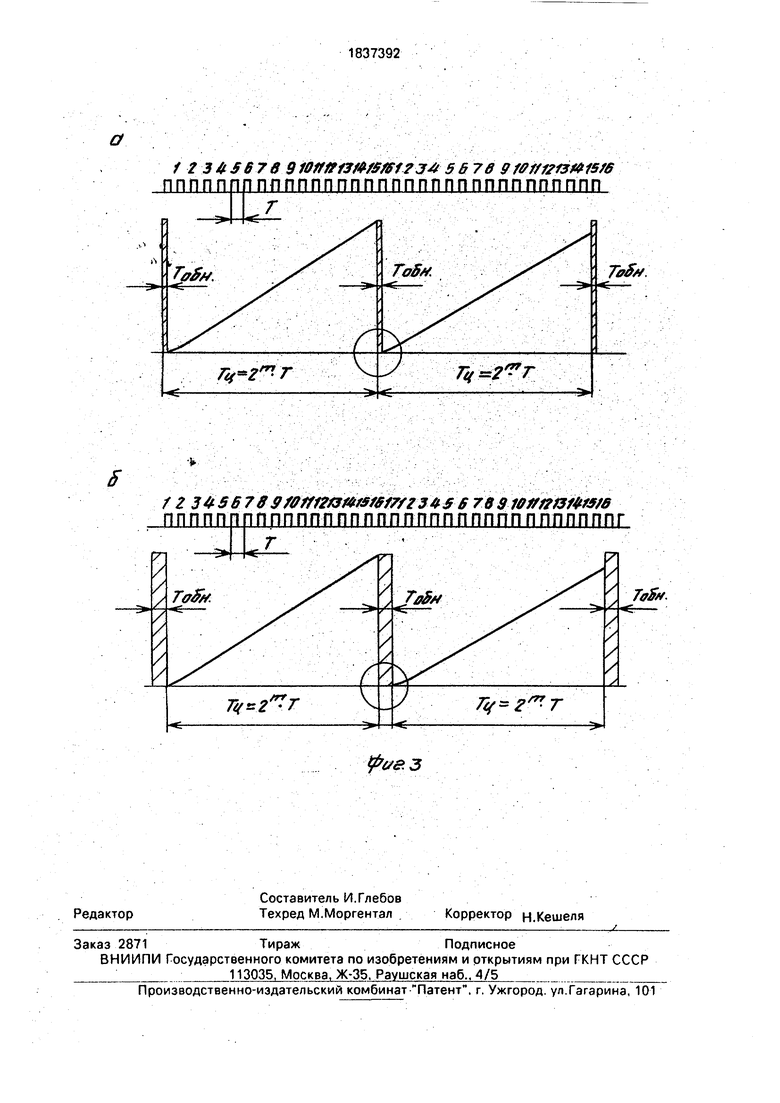

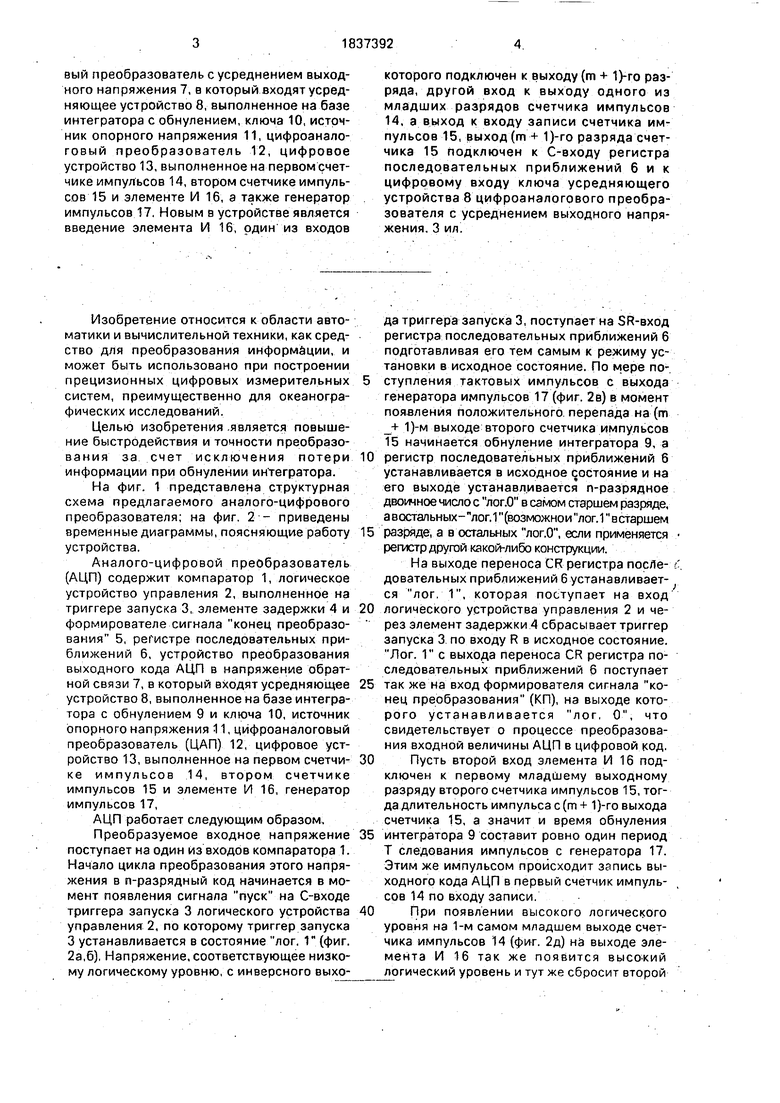

На фиг. 1 представлена структурная схема предлагаемого аналого-цифрового преобразователя; на фиг. 2 - приведены временные диаграммы, поясняющие работу устройства.

Аналого-цифровой преобразователь (АЦП) содержит компаратор 1, логическое устройство управления 2, выполненное на триггере запуска 3, элементе задержки 4 и формирователе сигнала конец преобразования 5, регистре последовательных приближений 6, устройство преобразования выходного кода АЦП в напряжение обратной связи 7, в который входят усредняющее устройство 8, выполненное на базе интегратора с обнулением 9 и ключа 10, источник опорного напряжения 11, цифроаналоговый преобразователь (ЦАП) 12, цифровое устройство 13, выполненное на первом счетчике импульсов 14, втором счетчике импульсов 15 и элементе И 16, генератор импульсов 17,

АЦП работает следующим образом.

Преобразуемое входное напряжение поступает на один из входов компаратора 1. Начало цикла преобразования этого напряжения в n-разрядный код начинается в момент появления сигнала пуск на С-входе триггера запуска 3 логического устройства управления 2, по которому триггер запуска 3 устанавливается в состояние лог. 1 (фиг. 2а,б), Напряжение, соответствующее низкому логическому уровню, с инверсного выхода триггера запуска 3, поступает на SR-вход регистра последовательных приближений 6 подготавливая его тем самым к режиму установки в исходное состояние. По мере поступления тактовых импульсов с выхода генератора импульсов 17 (фиг. 2в) в момент появления положительного перепада на (т + 1)-м выходе второго счетчика импульсов 15 начинается обнуление интегратора 9, а

регистр последовательных приближений 6 устанавливается в исходное состояние и на его выходе устанавливается п-разрядное двоичное число с лог.О в самом старшем разряде, а востальных- лог. 1 (возможной лог. 1 в старшем

разряде, а в остальных лог.О, если применяется регистр другой какой-либо конструкции.

На выходе переноса CR регистра после- довательных приближений 6 устанавливается лог. 1, которая поступает на вход

логического устройства управления 2 и через элемент задержки 4 сбрасывает триггер запуска 3 по входу R в исходное состояние. Лог. 1 с выхода переноса CR регистра последовательных приближений 6 поступает

так же на вход формирователя сигнала конец преобразования (КП), на выходе которого устанавливается лог, 0, что свидетельствует о процессе преобразования входной величины АЦП в цифровой код.

Пусть второй вход элемента И 16 подключен к первому младшему выходному разряду второго счетчика импульсов 15, тогда длительность импульса с (т + 1)-го выхода счетчика 15, а значит и время обнуления

интегратора 9 составит ровно один период Т следования импульсов с генератора 17. Этим же импульсом происходит запись выходного кода АЦП в первый счетчик импульсов 14 по входу записи.

При появлении высокого логического

уровня на 1-м самом младшем выходе счетчика импульсов 14 (фиг. 2д) на выходе элемента И 16 так же появится высо-кий логический уровень и тут же сбросит второй

счетчик 15 в исходное состояние, в результате исчезнет и высокий логический уровень с выхода элемента совпадения 16. С этого момента начинается цикл преобразования выходного кода АЦП в аналоговый сигнал обратной связи.

По мере поступления импульсов с выхода генератора импульсов 17 на тактовые входы первого 14 и второго 15 счетчиков импульсов на выходах последних начинает- возрастать значение кодов от записанных в них по импульсам с (т + 1)-го выхода второго счетчика 15 и выхода элемента И 16.

Процесс формирования аналогового сигнала на выходе цифроаналогового преобразователя (ЦАП) 12 иллюстрируется временными диаграммами, представленными на фиг. 2.3.

После занесения выходного кода АЦП в первый счетчик импульсов 14 на выходе ЦАП 12 установится значение равное

ицдм Дицдп (целая часть дроби-{Ј ) (1)

NBX

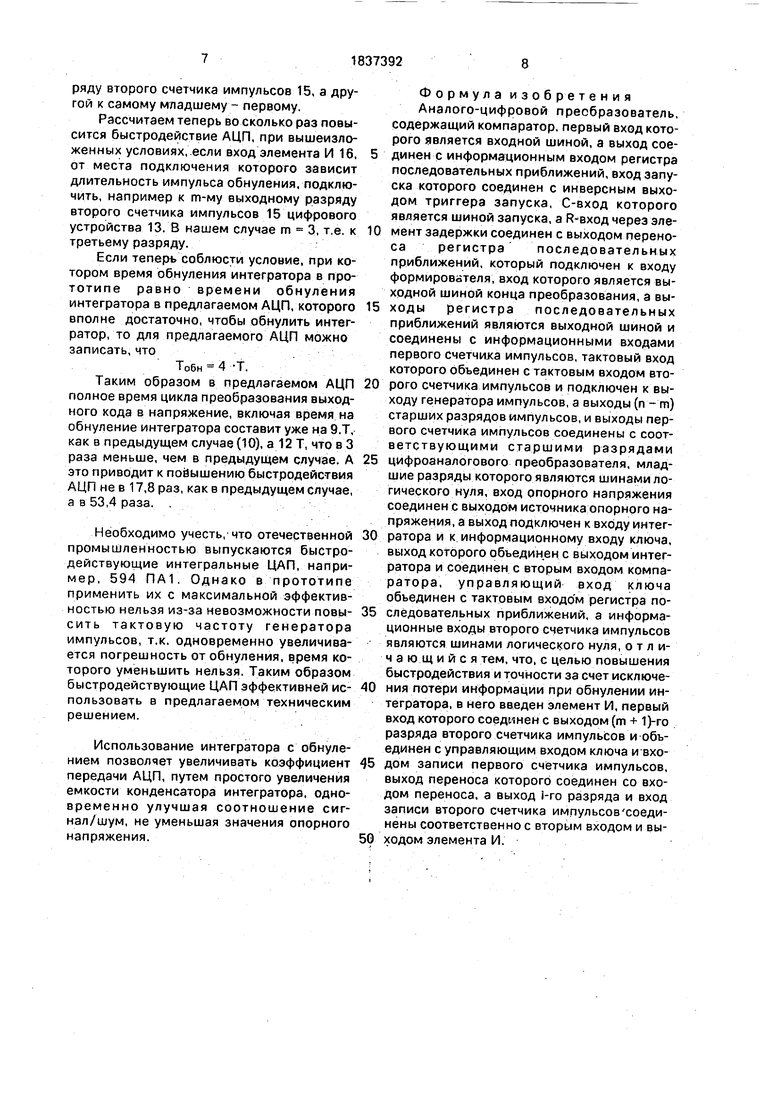

где m п - К - количество младших разрядов, получающихся в процессе преобразования выходного кода АЦП в напряжение обратной связи цифровым устройством 13. По мере поступления тактовых импульсов с генератора 17, через определенное количество периодов тактовых импульсов, определяемых численным значением кода из m младших разрядов, напряжение на выходе ЦАП 12 возрастет на величину Аицдп соответствующую используемой его дискретности (К-разрядов). Эта величина напряжения на выходе ЦАП 12 будет оставаться до 16-го тактового импульса, т.е. до момента появления импульса на (т + 1)-ом выходном разряде второго счетчика импульсов 15 фиг. 2з) Т.е. в процессе преобразования выходного кода АЦП в напряжение обратной связи попросту будет происходить ши- ротноимпульсная модуляция младшего используемого разряда ЦАП 12 Дицдп на фоне установленного значения определяемого выражением (1) (см. фиг 2, 3).

Напряжение с выхода ЦАП 12 усредняется интегратором 9 за период Тц, равным 2т периодам тактовых импульсов генератора 17 Время обнуления интегратора находится за пределами времени осреднения, что позволило исключить погрешность преобразования от обнуления интегратора, применяя его, совместно с ключем, в качестве усредняющего устройства.

Кроме того, предлагаемое решение позволяет наряду с точностью существенно повысить быстродействие АЦП.

Пусть необходимо построить АЦП по схеме прототипа с дифференциальной нелинейностью, приведенной ко входу, не более 0,3 кванта. Причем быстродействие элемен- 5 тов схемы позволяет обнулить интегратор за 1/10 периода тактовых импульсов генератора импульсов. Тогда, дифференциальная нелинейность интегрального ЦАП должна составить 0,2 кванта. А это легко

0 достигнуть, не используя три младших разряда в ЦАП, если его дифференциальная нелинейность равна 1 кванту (например, с буквой А в микросхемах 572 ПА1А и 572 ПА2А). Но при этом необходимо нарастить

5 второй счетчик цифрового устройства на три разряда, чтобы получить восемь градаций при широтно-импульсной модуляции полученного младшего разряда интегрального ЦАП (т.е. m 3). Таким образом дифференциальная нелинейность ЦАП с усреднением выходного напряжения составит 0,1 + 0,125 0,225 кванта, что удовлетворяет условию, т.е. 0,3 кванта.

Учитывая, что быстродействие элемен5 тов схемы достаточны для обнуления интегратора за 1/10 Т, время одного цикла преобразования выходного кода АЦП в напряжение обратной связи составит 80 Тобн. В приведенном примере (где также m

0 3) предлагаемого АЦП полное время цикла преобразования выходного кода АЦП в напряжение обратной связи, включая время на обнуление интегратора составит 9 Т0бн, что в 8,9 меньше, чем в прототипе.

5

А если учесть, что дифференциальная нелинейность не должна превышать всего лишь 0,3 кванта, то в предлагаемом техническом решении достаточно не использо0 вать лишь 2 младших разряда интеграла ЦАП, в результате чего дифференциальная нелинейность АЦП достигнет уже 0,25 кванта, чего вполне достаточно для реализую- мой точности, т.к. погрешность об

5 обнуления интегратора отсутствует 8 результате для широтно-импульсной модуляции полученного младшего разряда ЦАП потребуется не 8 градаций, а всего 4, а это приводит к уменьшению разрядности втс0 рого счетчика цифрового устройства и увеличению быстродействия еще в 2 раза. Таким образом, предлагаемое техническое решение при указаных выше условиях не только повышает точность преобразования,

5 но и повышает быстродействие АЦП в 17,8 раз.

Вышеизложенный расчет приведен для примера, изложенного в описании предла гаемого АЦП, в котором один вход элемента И 16 подключен к (т + 1}-му выходному разряду второго счетчика импульсов 15, а другой к самому младшему - первому.

Рассчитаем теперь во сколько раз повысится быстродействие АЦП, при вышеизложенных условиях, если вход элемента И 16, от места подключения которого зависит длительность импульса обнуления, подключить, например к m-му выходному разряду второго счетчика импульсов 15 цифрового устройства 13. В нашем случае m 3, т.е. к третьему разряду.

Если теперь соблюсти условие, при котором время обнуления интегратора в прототипе равно времени обнуления интегратора в предлагаемом АЦП, которого вполне достаточно, чтобы обнулить интегратор, то для предлагаемого АЦП можно записать, что

Тобн 4 -Т.

Таким образом в предлагаемом АЦП полное время цикла преобразования выходного кода в напряжение, включая время на обнуление интегратора составит уже на 9.Т, как в предыдущем случае (10), а 12 Т, что в 3 раза меньше, чем в предыдущем случае. А это приводит к повышению быстродействия АЦП не в 17,8 раз, как в предыдущем случае, а в 53,4 раза.

Необходимо учесть, что отечественной промышленностью выпускаются быстродействующие интегральные ЦАП, например, 594 ПА1. Однако в прототипе применить их с максимальной эффективностью нельзя из-за невозможности повысить тактовую частоту генератора импульсов, т.к. одновременно увеличивается погрешность от обнуления, время которого уменьшить нельзя. Таким образом быстродействующие ЦАП эффективней использовать в предлагаемом техническим решением.

Использование интегратора с обнулением позволяет увеличивать коэффициент передачи АЦП, путем простого увеличения емкости конденсатора интегратора, одновременно улучшая соотношение сигнал/шум, не уменьшая значения опорного напряжения.

Формула изобретения Аналого-цифровой преобразователь, содержащий компаратор, первый вход которого является входной шиной, а выход соединен с информационным входом регистра последовательных приближений, вход запуска которого соединен с инверсным выходом триггера запуска, С-вход которого является шиной запуска, а R-вход через элемент задержки соединен с выходом переноса регистра последовательных приближений, который подключен к входу формирователя, вход которого является выходной шиной конца преобразования, а выходы регистра последовательных приближений являются выходной шиной и соединены с информационными входами первого счетчика импульсов, тактовый вход которого объединен с тактовым входом второго счетчика импульсов и подключен к выходу генератора импульсов, а выходы (п - т) старших разрядов импульсов, и выходы первого счетчика импульсов соединены с соответствующими старшими разрядами

цифроаналогового преобразователя, младшие разряды которого являются шинами логического нуля, вход опорного напряжения соединен с выходом источника опорного напряжения, а выход подключен к входу интегратора и к информационному входу ключа, выход которого объединен с выходом интегратора и соединен с вторым входом компаратора, управляющий вход ключа обьединен с тактовым входо м регистра последовательных приближений, а информационные входы второго счетчика импульсов являются шинами логического нуля, отличающийся тем, что, с целью повышения быстродействия и точности за счет исключения потери информации при обнулении интегратора, в него введен элемент И, первый вход которого соединен с выходом (т + 1)-го разряда второго счетчика импульсов и объединен с управляющим входом ключа и входом записи первого счетчика импульсов, выход переноса которого соединен со входом переноса, а выход 1-го разряда и вход записи второго счетчика импульсов соеди- нены соответственно с вторым входом и выходом элемента И.

I tow Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1986 |

|

SU1562971A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2002 |

|

RU2204884C1 |

| Логарифмический аналого-цифровой преобразователь | 1987 |

|

SU1481803A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1358094A1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2656989C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2205500C1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Устройство для автоматической фокусировки луча электронно-лучевой трубки | 1989 |

|

SU1626451A2 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

Изобретениетфедназначено для прецизионных цифровых измерительных систем, преимущественно для океанографических исследований. Цель изобретения - повышение быстродействия и точности преобразования за счет исключения потери информации при обнулении интегратора. Аналого-цифровой преобразователь содержит компаратор 1, логическое устройство 2, в которое входят триггер знака 3, элемент задержки 4 и инвертор 5, регистр последовательных приближений 6, цифроаналого

Гг. Запуска

3;

TV/

-Tjafa 0

пппппппппппппп

(trn-П-и ЙУхад 1® счетчица, г

1-й Выход 2-го счетчика

п п

ПППППППГ

СИ-Выход регистра. /7/7

(ОстатокdpoSu - -f-J-fy

Zm

js

X

fy 2

U

и,

инт

1718

пппппппппп

п п

п

-f

Zm

/

Фиг.г

/ 2 345678 910tffff3f№fff 34 5676 9 fff#fff3#15t6 ППППППППЛПППППППППППППППППППППППП

f Z 3456789f0fm&#fWf7f234$678910tfff13f№/6

ППППППППППППППППППППППППППППППППППГ

Tfffa.

TaS/f.

fie/аз

Авторы

Даты

1993-08-30—Публикация

1990-05-03—Подача