112

Изобретение относится к цифровой измерительной и вычислительной технике и может быть использовано для преобразования аналоговых величин в цифровые.

Цель изобретения - повышение быстродействия устройства аналого-цифрового преобразования.

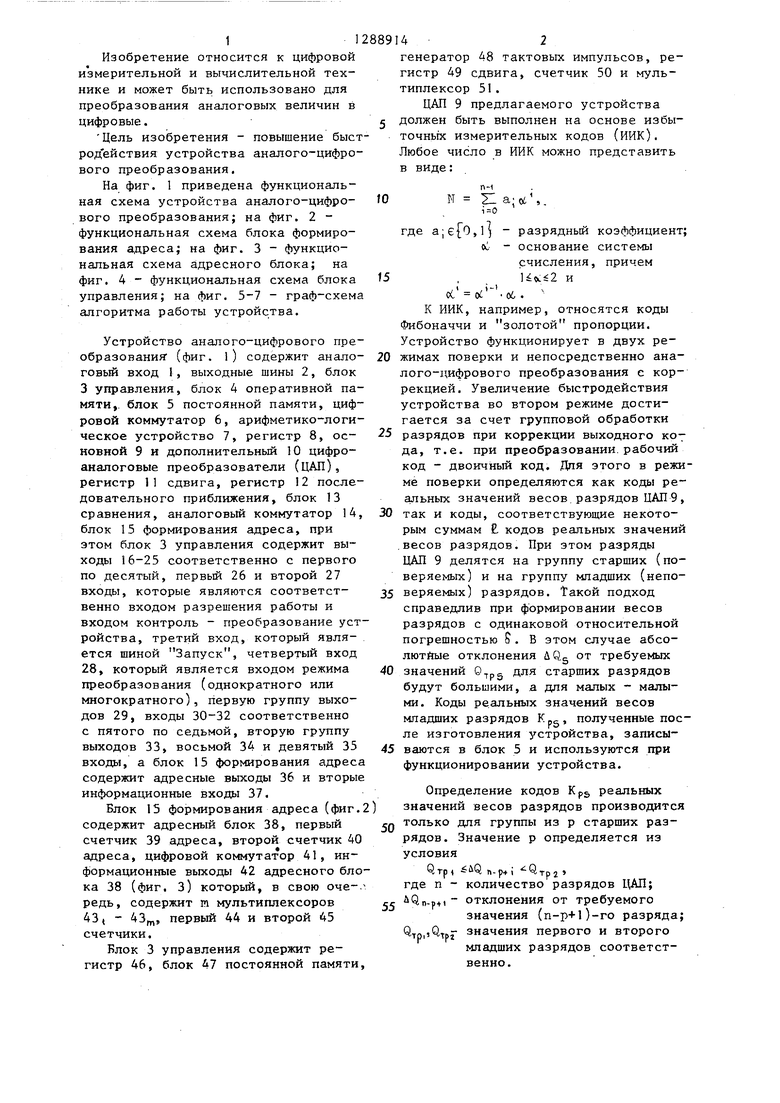

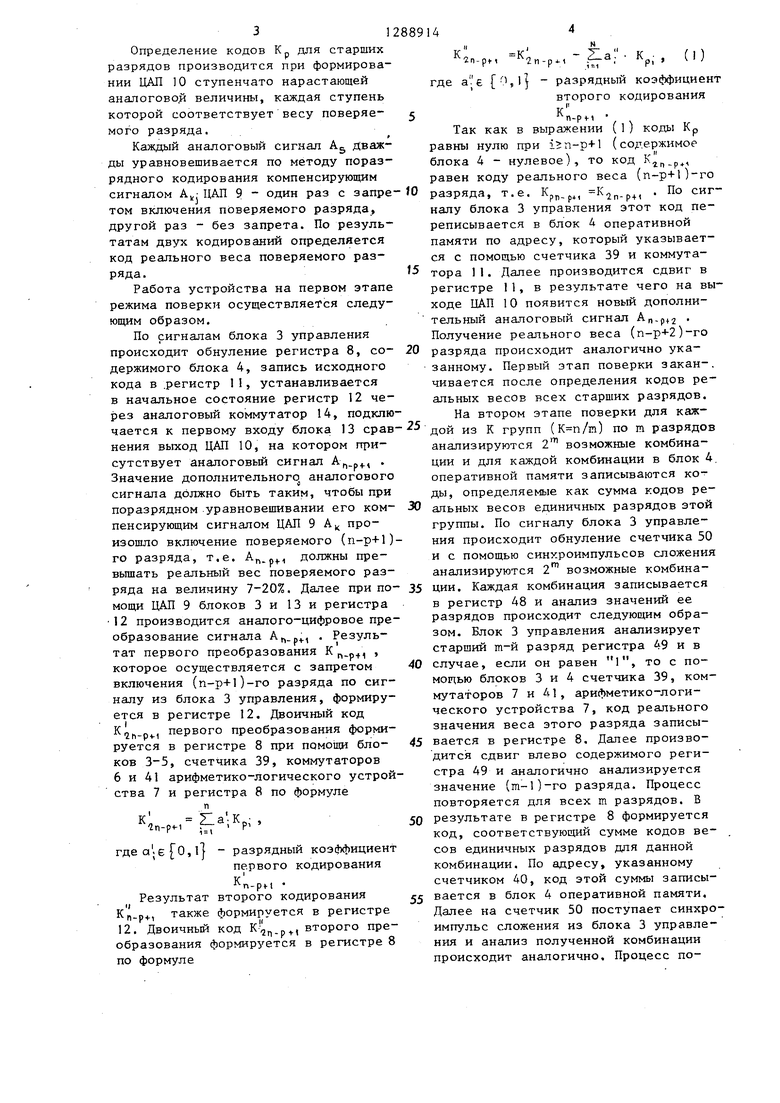

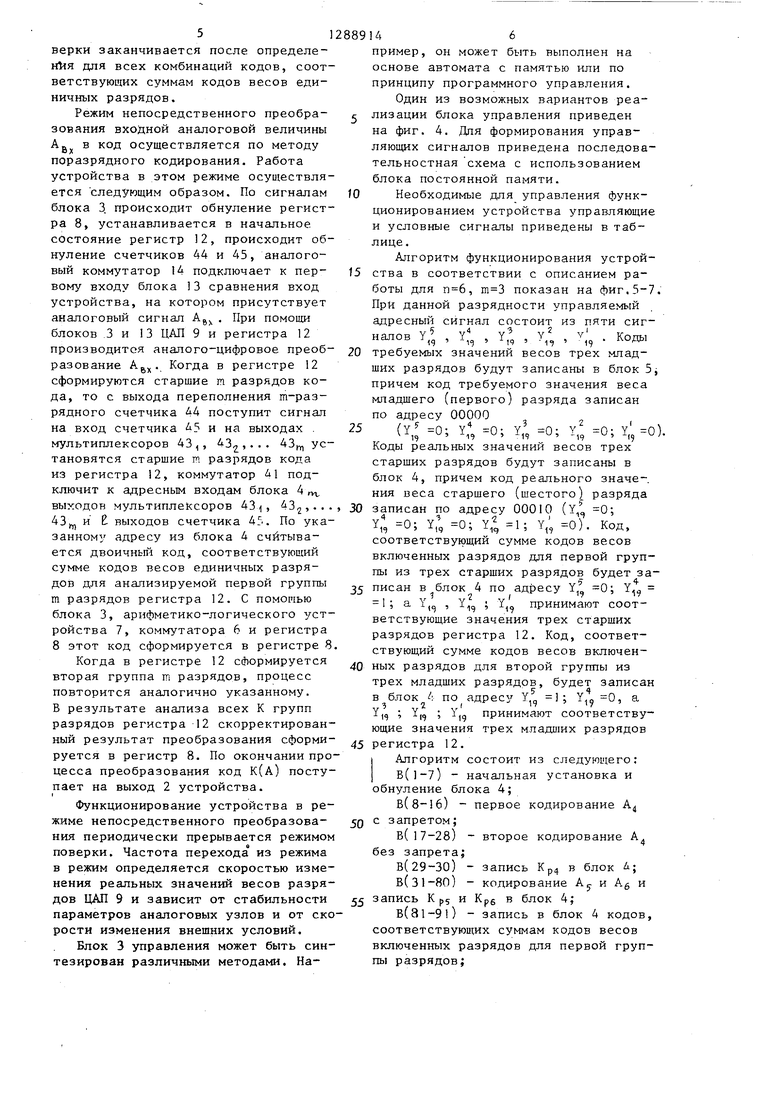

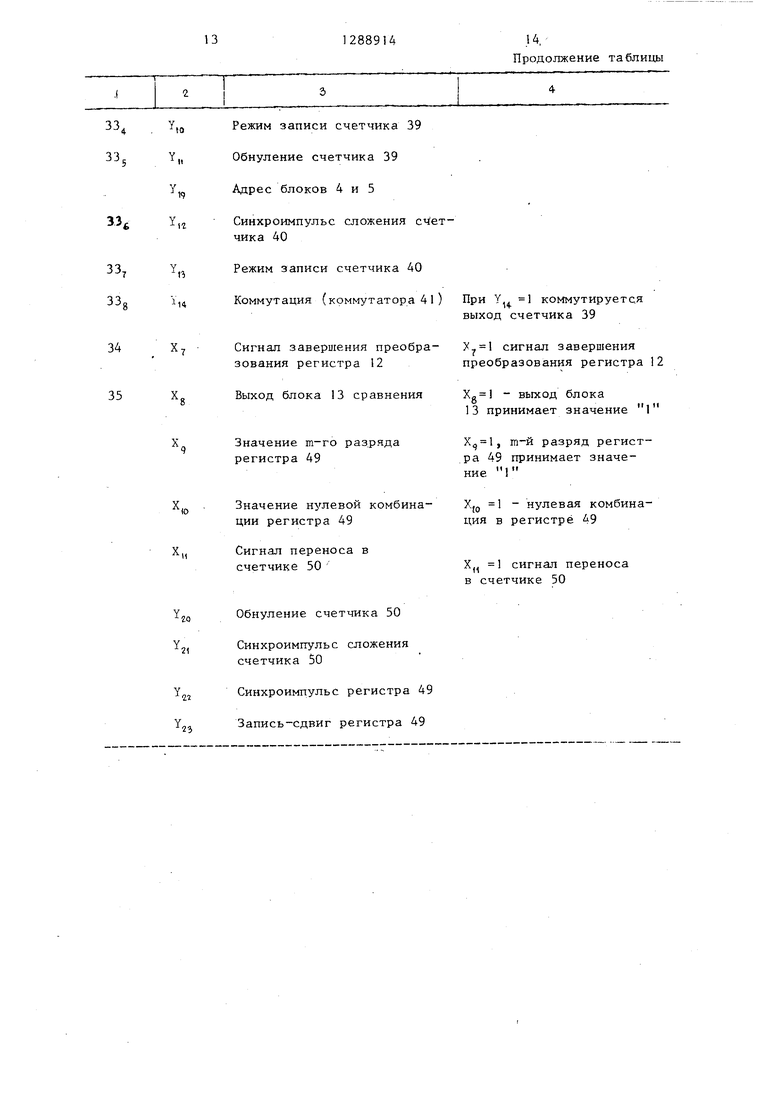

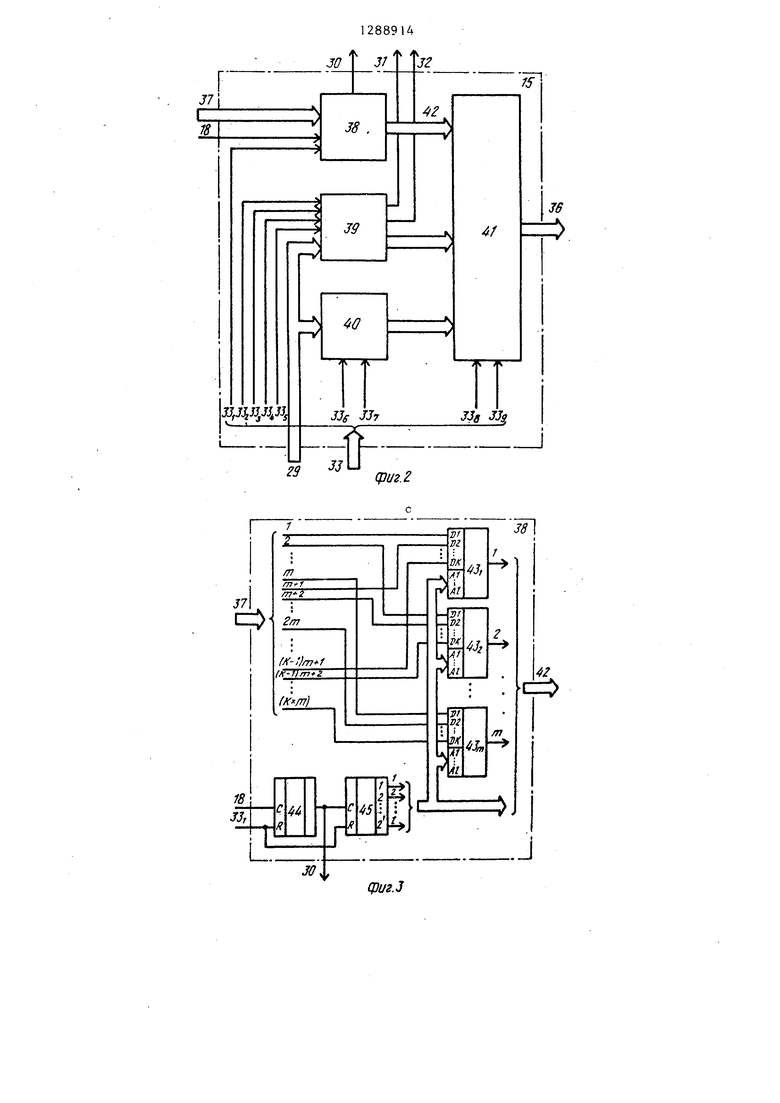

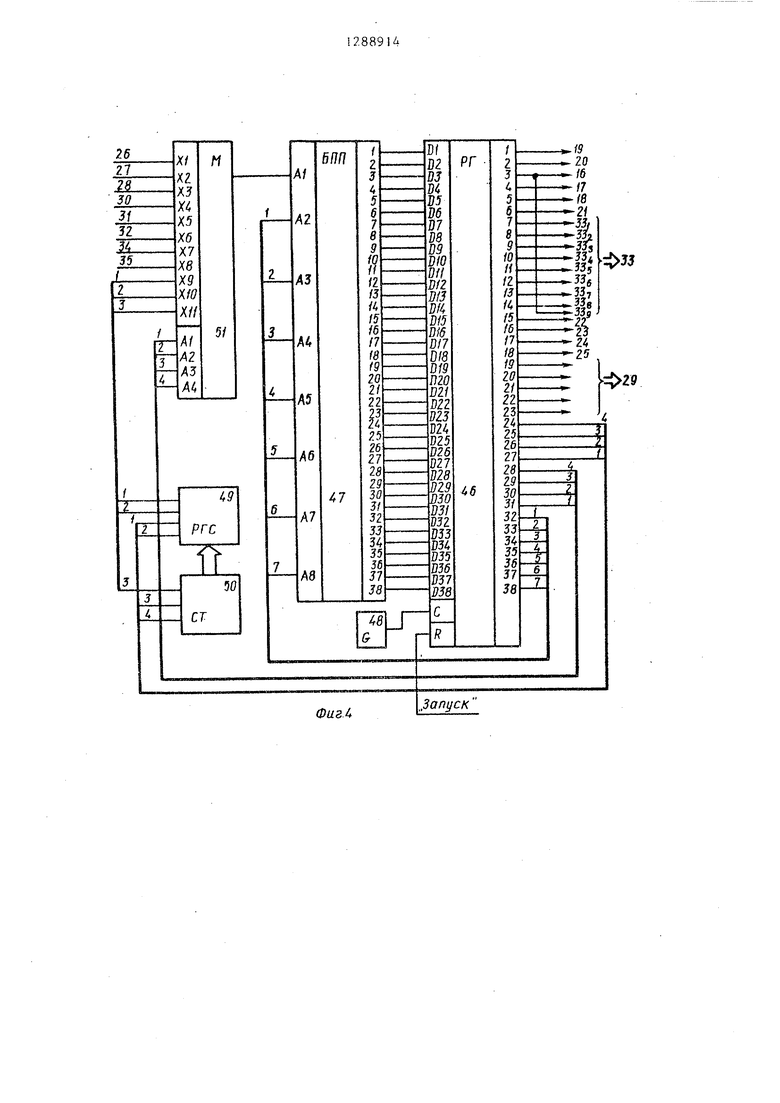

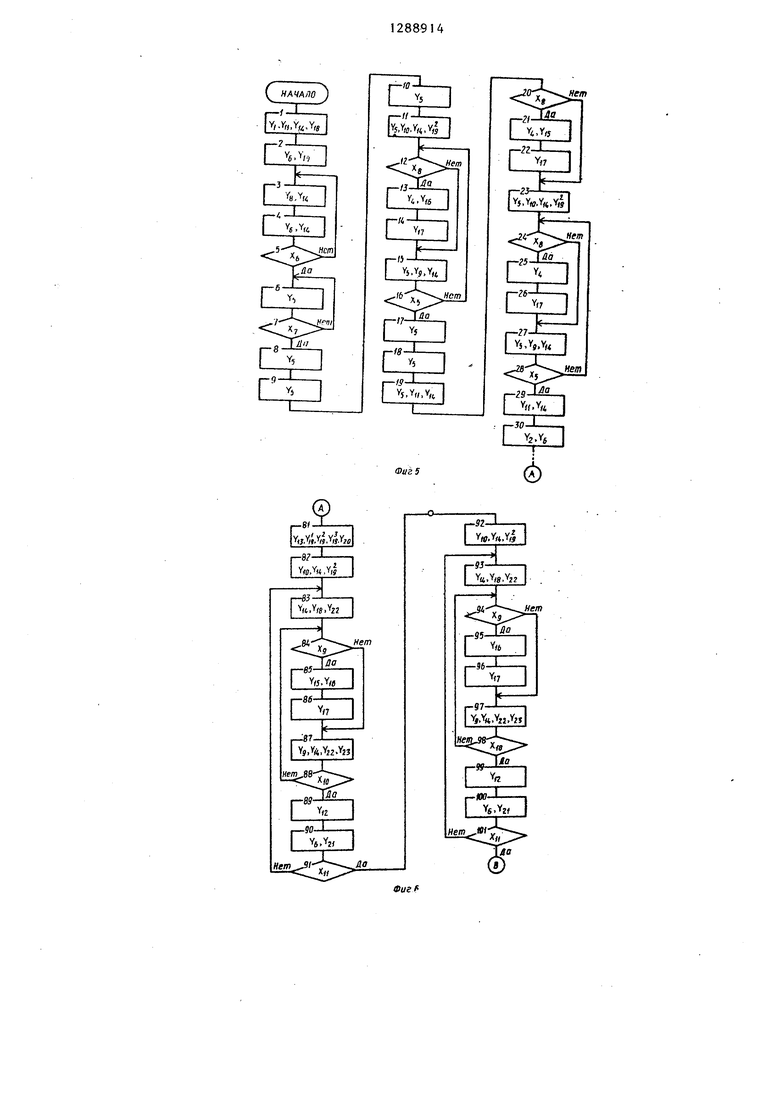

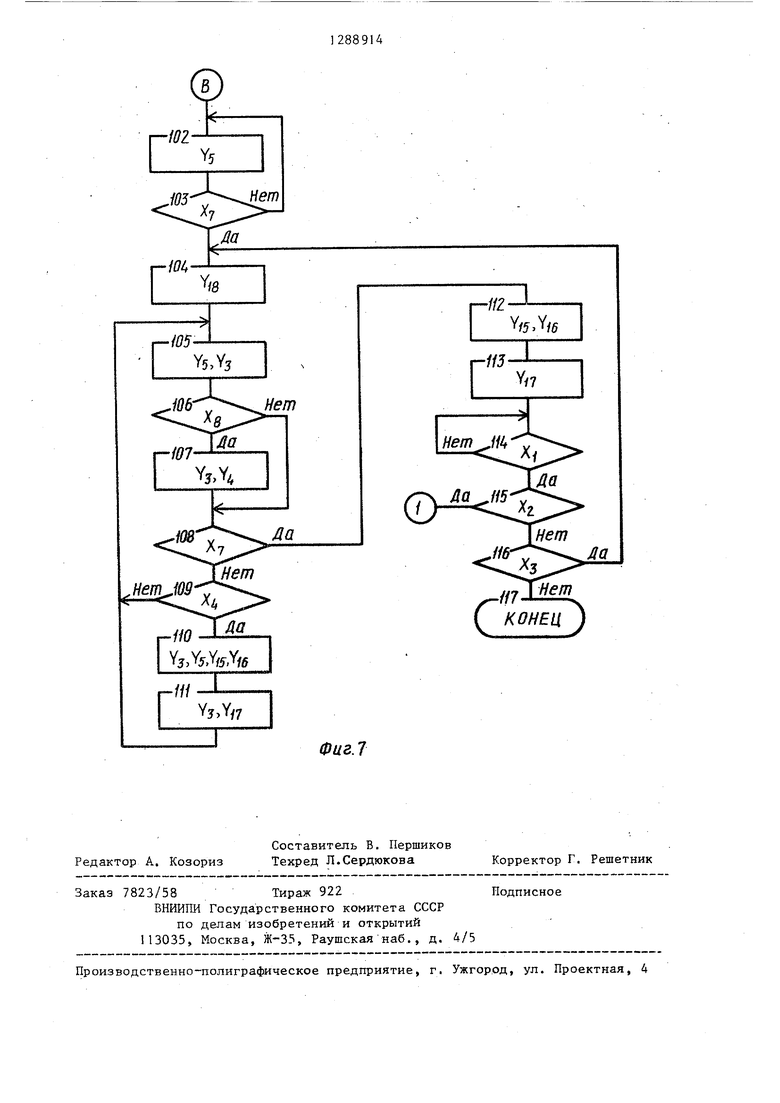

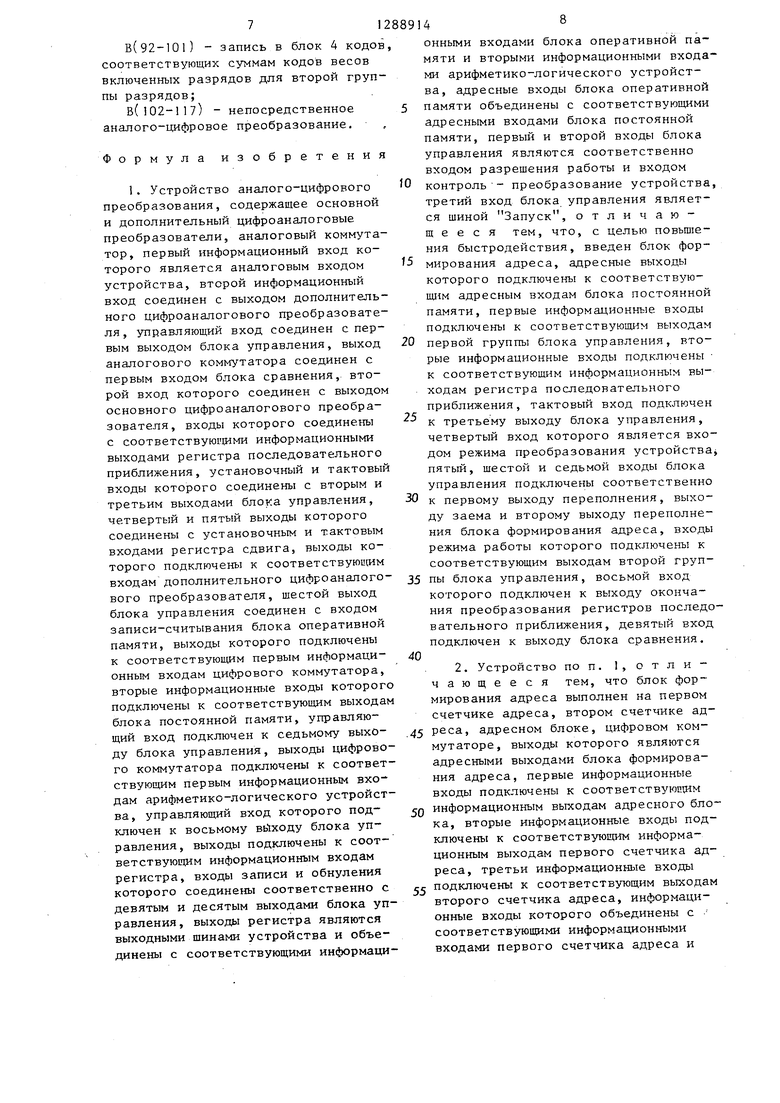

На фиг. 1 приведена функциональная схема устройства аналого-цифро- вого преобразования; на фиг. 2 - функциональная схема блока формирования адреса; на фиг. 3 - функциональная схема адресного блока; на фиг, 4 - функциональная схема блока управления; на фиг, 5-7 - граф-схема алгоритма работы устройства.

Устройство аналого-цифрового преобразования (фиг, l) содержит анало- говьй вход I, выходные шины 2, блок 3 управления, блок 4 оперативной памяти,, блок 5 постоянной памяти, цифровой коммутатор 6, арифметико-логическое устройство 7, регистр 8, ос- новной 9 и дополнительный 10 цифро- аналоговые преобразователи (ЦАП), регистр 11 сдвига, регистр 12 последовательного приближения, блок 13 сравнения, аналоговый коммутатор 14, блок 15 формирования адреса, при этом блок 3 управления содержит выходы 16-25 соответственно с первого по десятый, первый 26 и второй 27 входы, которые являются соответст- венно входом разрешения работы и входом контроль - преобразование устройства, третий вход, который является шиной Запуск, четвертый вход 28, который является входом режима преобразования (однократного или многократного), первую группу выходов 29, входы 30-32 соответственно с пятого по седьмой, вторую группу выходов 33, восьмой 34 и девятый 35 входы, а блок 15 формирования адреса содержит адресные выходы 36 и вторые информационные входы 37,

Блок 15 формирования адреса (фиг,2 содержит адресный блок 38, первый счетчик 39 адреса, второй счетчик 40 адреса, цифровой коммутатор 41, информационные выходы 42 адресного блока 38 (фиг, З) который, в свою оче-- редь, содержит п мультиплексоров 43, - 43, первый 44 и второй 45 счетчики.

Блок 3 управления содержит регистр 46, блок 47 постоянной памяти.

14 2

генератор 48 тактовых импульсов, регистр 49 сдвига, счетчик 50 и мультиплексор 51 .

ЦАП 9 предлагаемого устройства должен быть выполнен на основе избы- точньЬс измерительных кодов (ИИК). Любое число в ИИК можно представить в виде:

П-1

N 21 а; Об ,.

где ,1) - разрядный коэффициент л1 - основание системы счисления, причем и сО .о6.

К ИИК, например, относятся коды Фибоначчи и золотой пропорции. Устройство функционирует в двух режимах поверки и непосредственно ана- лого-1 ифрового преобразования с коррекцией. Увеличение быстродействия устройства во втором режиме достигается за счет групповой обработки разрядов при коррекции выходного кода, т,е, при преобразовании, рабочий код - двоичный код. Для этого в режиме поверки определяются как коды реальных значений весов,разрядов ЦАП 9 так и коды, соответствуюш;ие некоторым суммам кодов реальных значений .весов разрядов. При этом разряды ЦАП 9 делятся на группу старших (поверяемых) и на группу младших (неповеряемых) разрядов. Такой подход справедлив при формировании весов разрядов с одинаковой относительной погрешностью S, В этом случае абсо- лютйые отклонения uQg от требуемых значений O-rpg для старших разрядов будут большими, .а для малых - малыми. Коды реальных значений весов младших разрядов К-, полученные после изготовления устройства, записываются в блок 5 и используются при функционировании устройства.

Определение кодов Кр реальных значений весов разрядов производится только для группы из р старших разрядов. Значение р определяется из условия

Qrp, uQn-p+i QTp2

где n - количество разрядов ЦАП;

Qn-p+( отклонения от требуемого

значения (п-р-И)-го разряда;

Q.jpi,Q - значения первого и второго младших разрядов соответственно.

Определение кодов Кр для старших разрядов производится при формировании ЦАП 10 ступенчато нарастающей аналоговой величины, каждая ступень которой соответствует весу поверяе

мого разряда.

f

Каждый аналоговый сигнал Ag Дважды уравновешивается по методу поразрядного кодирования компенсирующим сигналом Ау- ЦАП 9 - один раз с запре том включения поверяемого разряда, другой раз - без запрета. По результатам двух кодирований определяется код реального веса поверяемого разряда.

Работа устройства на первом этапе режима поверки осуществляется следующим образом.

По сигналам блока 3 управления происходит обнуление регистра 8, содержимого блока 4, запись исходного кода в .регистр 11, устанавливается в начальное состояние регистр 12 через аналоговый коммутатор 14, подклю чается к первому входу блока 13 срав нения выход ЦАП 10, на котором присутствует аналоговый сигнал А.р4- Значение дополнительного, аналогового сигнала должно быть таким, чтобы при поразрядном уравновешивании его компенсирующим сигналом ЦАП 9 А, произошло включение поверяемого (п-р+1) го разряда, т.е. А ., должны пре- вьшать реальный вес поверяемого разряда на величину 7-20%. Далее при помощи ЦАП 9 блоков 3 и 13 и регистра 12 производится аналого-цифровое преобразование сигнала А. р, . Результат первого преобразования К г,.р+, , которое осуществляется с запретом включения (п-р+1)-го разряда по сигналу из блока 3 управления, формируется в регистре 12, Двоичный код К,2 первого преобразования формируется в регистре 8 при помощи блоков 3-5, счетчика 39, коммутаторов 6 и 41 арифметико-логического устройства 7 и регистра 8 по формуле

К

,

,

гдеа ;е 0,1| - разрядный коэффициент первого кодирования

п-ри Результат второго кодирования

КП-РЧ-, также формируется в регистре 12. Двоичный код ., второго преобразования формируется в регистре 8 по формуле

., ., - .lal . Кр, , (1)

где а е 1 - разрядный коэффициент

второго кодирования

К

п-р

Так как в выражении (1) коды Кр равны нулю при i п-р+1 (содержимое блока 4 - нулевое), то код , равен коду реального веса (п-р+1)-го 10 разряда, т.е. К., К2п-р+, ° налу блока 3 управления этот код переписывается в блок 4 оперативной памяти по адресу, который указывается с помощью счетчика 39 и коммута15 тора 11. Далее производится сдвиг в регистре 11, в результате чего на выходе ЦАП 10 появится новый дополнительный аналоговый сигнал А„, Получение реального веса (п-р+2)-го

20 разряда происходит аналогично указанному. Первый этап поверки закан-. чивается после определения кодов реальных весов всех старших разрядов. На втором этапе поверки для каж- дои из К групп () по m разрядов анализируются 2 возможные комбинации и для каждой комбинации в блок 4. оперативной памяти записываются ко- ды, определяемые как сумма кодов ре альных весов единичных разрядов этой группы. По сигналу блока 3 управления происходит обнуление счетчика 50 и с помощью синхроимпульсов сложения анализируются 2 возможные комбина35 ции. Каждая комбинация записывается в регистр 48 и анализ значений ее разрядов происходит следующим образом. Блок 3 управления анализирует старший т-й разряд регистра 49 и в

40 случае, если он равен 1, то с помощью блоков 3 и 4 счетчика 39, коммутаторов 7 и 41, арифметико-логического устройства 7, код реального значения веса этого разряда записы45 вается в регистре 8. Далее производится сдвиг влево содержимого регистра 49 и аналогично анализируется значение (m-l)-ro разряда. Процесс повторяется для всех m разрядов. В

50 результате в регистре 8 формируется код, соответствующий сумме кодов весов единичных разрядов для данной комбинации. По адресу, указанному счетчиком 40, код этой суммы записы55 вается в блок 4 оперативной памяти. Далее на счетчик 50 поступает синхроимпульс сложения из блока 3 управления и анализ полученной комбинации происходит аналогично. Процесс по51

верки заканчивается после определе- }Ля для всех комбинаций кодов, соответствующих суммам кодов весов единичных разрядов.

Режим непосредственного преобра- зования входной аналоговой величины Ag в код осуществляется по методу поразрядного кодирования. Работа устройства в этом режиме осуществляется следующим образом. По сигналам блока 3. происходит обнуление регистра 8, устанавливается в начальное состояние регистр 12, происходит обнуление счетчиков 44 и 45, аналоговый коммутатор 14 подключает к пер- вому входу блока 13 сравнения вход устройства, на котором присутствует аналоговый сигнал А, . При помощи блоков 3 и 13 ЦАП 9 и регистра 12 производится аналого-цифровое преоб- разование А. Когда в регистре 12 сформируются старшие m разрядов кода, то с выхода переполнения т-раз- рядного счетчика 44 поступит сигнал на вход счетчика З и на выходах . мультиплексоров 43,, 43,... 43 установятся старшие m разрядов кода из регистра 12, коммутатор 41 подключит к адресньм входам блока 4 п выходов мультиплексоров 43 , 43, 43( и t выходов счетчика 45. По указанному адресу из блока 4 считывается двоичньй код, соответствующий сумме кодов весов единичных разрядов для анализируемой первой группы m разрядов регистра 12. С помоиью блока 3, арифметико-логического устройства 7, коммутатора 6 и регистра 8 этот код сформируется в регистре 8

Когда в регистре 12 сформируется вторая группа m разрядов, процесс повторится аналогично указанному. Б результате анализа всех К групп разрядов регистра 12 скорректированный результат преобразования сформи- руется в регистр 8. По окончании процесса преобразования код К(А) поступает на выход 2 устройства.

Функционирование устройства в режиме непосредственного преобразова- ния периодически прерывается режимом поверки. Частота перехода из режима в режим определяется скоростью изменения реальных значений весов разрядов ЦАП 9 и зависит от стабильности параметров аналоговых узлов и от скорости изменения внешних условий.

Блок 3 управления может быть синтезирован различными методами. На

5

146

пример, он может быть выполнен на основе автомата с памятью или по принципу программного управления.

Один из возможных вариантов реализации блока управления приведен на фиг. 4. Для формирования управляющих сигналов приведена последова- тельностная схема с использованием блока постоянной памяти.

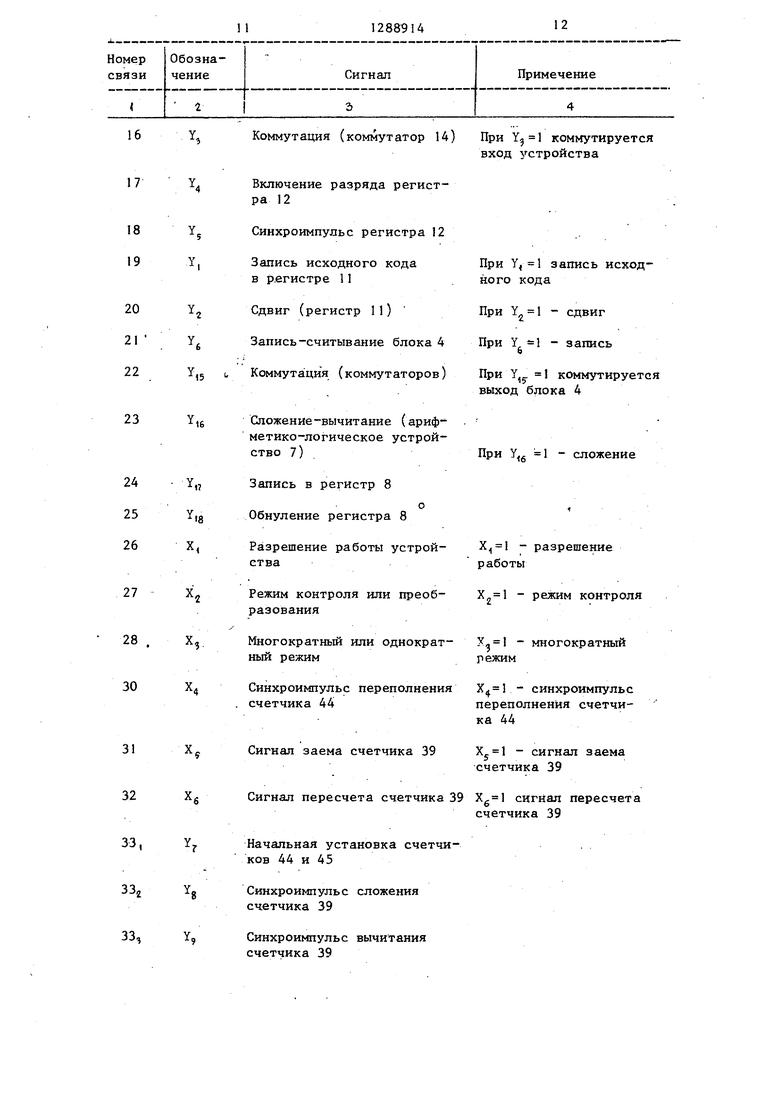

Необходимые для управления функционированием устройства управляющие и условные сигналы приведены в таблице.

Алгоритм функционирования устройства в соответствии с описанием работы для , показан на фиг.5-7. При данной разрядности управляемый адресный сигнал состоит из пяти сиг- налов У , Y; , Yf, , Y; , v; . Коды требуемых значений весов трех младших разрядов будут записаны в блок 5 причем код требуемого значения веса младщего (первого) разряда записан по адресу 00000

CY п- Y п- Y п V Y -ci

- -19 - - 19

Коды реальных значений весов трех старших разрядов будут записаны в блок 4, причем код реального значе-. ния веса старшего (шестого) разряда записан по адресу 00010 (уД 0; у, 0; у , 0; уД -1; У,, 0). Код, соответствующий сумме кодов весов включенных разрядов для первой группы из трех старших разрядов будет записан в блок 4 по адресу У, 0; У,, -1; а У,,, , У,

1

4q принимают соответствующие значения трех старших разрядов регистра 12. Код, соответствующий сумме кодов весов включенных разрядов для второй группы из трех младших разрядов, будет записан в блок 4 по адресу У 1 ; У,о 0, а y,q ; У, ; принимают соответствующие значения трех младших разрядов регистра 12.

Алгоритм состоит из следующего:

B(l-7) - начальная установка и обнуление блока 4;

Б() - первое кодирование А с запретом;

Б(17-28) - второе кодирование А без запрета;

Б(29-30) - запись Кр в блок ;

в( 31-80) - кодирование Aj. и Ag и запись К р5 и Крб в блок 4;

Б(а1-91) - запись в блок 4 кодов, соответствующих суммам кодов весов включенных разрядов для первой группы разрядов;

71

В(92-101) - запись в блок 4 кодов соответствующих суммам кодов весов включенных разрядов для второй группы разрядов;

В(102-117) - непосредственное аналого-цифровое преобразование.

Формула изобретения

1. Устройство аналого-цифрового преобразования, содержащее основной и дополнительный цифроанапоговые преобразователи, аналоговый коммутатор, первый информационный вход которого является аналоговым входом устройства, второй информационный вход соединен с выходом дополнительного цифроаналогового преобразователя , управляющий вход соединен с первым выходом блока управления, выход аналогового коммутатора соединен с первым входом блока сравнения, второй вход которого соединен с выходом основного цифроаналогового преобразователя, входы которого соединены с соответствуюидами информационными выходами регистра последовательного приближения, установочный и тактовый входы которого соединены с вторым и третьим выходами блока управления, четвертый и пятый выходы которого соединены с установочным и тактовым входами регистра сдвига, выходы которого подключены к соответствующим входам дополнительного цифроаналого- вого преобразователя, щестой выход блока управления соединен с входом записи-считывания блока оперативной памяти, выходы которого подключены к соответствующим первым информаци- онным входам цифрового коммутатора, вторые информационн1 1е входы которого подключены к соответствующим выходам блока постоянной памяти, управляющий вход подключен к седьмому выхо- ду блока управления, выходы цифрового коммутатора подключены к соответ- cтвyюш м первым информационным входам арифметико-логического устройства, управляющий вход которого под- ключен к восьмому вЫходу блока управления, выходы подключены к соответствующим информационным входам регистра, входы записи и обнуления которого соединены соответственно с девятым и десятым выходами блока управления, выходы регистра являются выходными шинами устройства и объединены с соответствующими информаци5

5

89

5

О 0 0 5 40 45 50

148

онными входами блока оперативной памяти и вторыми информационными входами арифметико-логического устройства, адресные входы блока оперативной памяти объединены с соответствующими адресными входами блока постоянной памяти, первый и второй входы блока управления являются соответственно входом разрешения работы и входом контроль - преобразование устройства, третий вход блока управления является шиной Запуск, отличающееся тем, что, с целью повьш е- ния быстродействия, введен блок формирования адреса, адресные выходы которого подключены к соответствующим адресным входам блока постоянной памяти, первые информационные входы подключены к соответствующим выходам первой группы блока управления, вторые информационные входы подключены к соответствующим информационным выходам регистра последовательного приближения, тактовый вход подключен к третьему выходу блока управления, четвертый вход которого является входом режима преобразования устройства пятый, щестой и седьмой входы блока управления подключены соответственно к первому выходу переполнения, выходу заема и второму выходу переполнения блока формирования адреса, входы режима работы которого подключены к соответствующим выходам второй группы блока управления, восьмой вход которого подключен к выходу окончания преобразования регистров последовательного приближения, девятый вход подключен к выходу блока сравнения.

2. Устройство по п. 1, о т л и - чающееся тем, что блок фор мирования адреса выполнен на первом счетчике адреса, втором счетчике адреса, адресном блоке, цифровом коммутаторе, выходы которого являются адресными выходами блока формирования адреса, первые информационные входы подключены к соответствуюптим информационным выходам адресного блока, вторые информационные входы подключены к соответствующим информационным выходам первого счетчика адреса, третьи информационные входы подключены к соответствующим выходам второго счетчика адреса, информационные входы которого объединены с соответствующими информационными входами первого счетчика адреса и

являются первыми информационными вхо- д ами блока формирования адреса, информационные входы адресного блока являются вторыми информационными входами блока формирования адреса, так- тобый вход является тактовым входом блока формирования адреса, выход переполнения является первым выходом переполнения блока формирования адреса, выход заема и выход переполнения первого счетчика адреса являются соответственно выходом заема и вторым выходом переполнения блока формирования адреса, установочный вход адресного блока, входы сложения, вычитания, записи и обнуления первого счетчика адреса, входы сложения и записи второго счетчика адреса, первый и второй управляющие входы цифрового коммутатора являются входами режима работы блока формирования адреса.

3.Устройство по пп. 1 и 2, о т- личающееся тем, что адресный блок в блоке формирования адреса выполнен на первом и вт,ором счетчиках, т-мультиплексорах с К информационными, входами каждый, где число разрядов основного цифроанапо- гового преобразователя, одноименные адресные входы которых объединены и подключены к соответствующим выходам второго счетчика, вход обнуления которого объединен с входом обнуления первого счетчика и является установочным входом адресного блока, счетный вход первого счетчика является тактовым входом адресного блока, выход переполнения первого счетчика подключен к счетному входу второго счетчика и является выходом переполнения адресного блока, одноименные информационные входы и мультиплексоров объединены в соответствующие К группы входов,которые являются соответствующими информационными входами адресного блока, выходы мультиплексоров и второго счетчика являются информационными выходами адресного блока.

4.Устройство по п. 1,отличающееся тем, что блок уп

равления выполнен на мультиплексоре, регистре сдвига, счетчике, блоке постоянной памяти, генераторе тактовых импульсов, регистре, информационные

входы которого подключены к соответствующим выходам блока постоянной памяти, тактовый вход подключен к выходу генератора тактовых импульсов, вход обнуления является третьим входом блока управления, выходы с первого по шестой Являются соответственно четвертым, пятым, первым, вторым, третьим и шестым выходами блока управления, выходы с седьмого по

четырнадцатый и третий выход регист- ра являются второй группой выходов блока управления, выходы с пятнадцатого по восемнадцатый являются соответственно, седьмым, восьмым, девятым и десятым выходами блока управления , выходы с девятнадцатого- по двадцать третий являются первой группой выходов блока управления, двадцать четвертый и двадцать пятый выходы подключены соответственно к входу обнуления и тактовому входу счетчика, двадцать шестой и двадцать седьмой выходы подключены соответственно к тактовому входу и входу записи сдвига регистра сдвига, выходы с двадцать восьмого по тридцать первый подключены соответственно к управляющим входам мультиплексора, информационные входы которого с первого по восьмой являются соответственно первым, вторым, четверть1м, пятым, шестым, седьмым5 восьмым и девятым входами блока управления, девятый и десятый информационные входы подключены к

соответствующим выходам регистра

сдвига, информационные входы которого подключены соответственно к информационным выходам счетчика, выход переполнения которого подключен к

одиннадцатому входу мультиплексора, выход которого подключен к первому адресному входу блока постоянной па-, мяти, адресные входы с второго по восьмой которого подключены к выходам регистра соответственно с тридцать JBToporo по тридцать восьмой.

16

Коммутация (коммутатор 14)

Y Включение разряда регистра 12

YJ Синхроимпульс регистра 12

YI Запись исходного кода в р.егистре 11

Yj Сдвиг (регистр 11)

YJ Запись-считывание блока 4

Y,5 1. Коммута ция (коммутаторов)

Чб

48

Сложение-вычитание (арифметико-логическое устройство 7) .

Запись в регистр 8

о Обнуление регистра 8

Разрешение работы устройства

27 Xj Режим контроля или преобразования

28 , Х Многократньш или однократный режим

30 Х Синхроимпульс переполнения . счетчика 44

31

Ху Сигнал заема счетчика 39

32

X.

Сигнал пересчета счетчика 39

33,

Начальная установка счетчи- ков 44 и 45

33,

Синхроимпульс сложения счетчика 39

33,

Синхроимпульс вычитания счетчика 39

При Yj 1 коммутируется вход устройства

При Y,l запись исходного кода

При Y l сдвиг

При Y - запись р

При . 1 коммутируется выход блока 4

При Y,g 1 - сложение

- разрешение работы

X 1 - режим контроля

Х,1 - многократный режим

- синхроимпульс переполнения счетчика 44

- сигнал заема счетчика 39

сигнал пересчета счетчика 39

чика 40

f, Режим записи счетчика 40 1, Коммутация (коммутатора 4 1 )

7 Сигнал завершения преобразования регистра 12

(g Выход блока 13 сравнения

Значение т-го разряда регистра 49

Значение нулевой комбинации регистра 49

Сигнал переноса в счетчике 50

Обнуление счетчика 50

Синхроимпульс сложения счетчика 50

Синхроимпульс регистра 49 Запись-сдвиг регистра 49

При Y 1 коммутируется выход счетчика 39

сигнал завершения преобразования регистра 12

- выход блока

13 принимает значение

, m-й разряд регистра 49 принимает значение 1

Х,(, 1 - нулевая комбинация в регистре 49

X,, 1 сигнал переноса в счетчике 50

(риг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257848A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1702525A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| Многоканальное устройство для ввода-вывода аналоговой информации | 1988 |

|

SU1564606A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования аналоговых сигналов в цифровой код. Устройство аналого-цифрового преобразования содержит аналоговый вход 1, выходные шины 2, блок 3 управления, блок 4 оперативной памяти. блок 3 постоянной памяти, цифровой коммутатор 6, арифметико-логическое устройство 7, регистр 8, основной цнфроаналоговый преобразователь 9, выполненный на основе избыточного измерительного кода, например, кода Фибоначчи, дополнительный цифроана- логовьш преобразователь 10, регистр 11 сдвига, регистр 12 последовательного приближения, блок 13 сравнения, аналоговый коммутатор 1А, блок 15 формирования адреса. Введенный блок 15 форкирования адреса и изменение алгоритма работы блока управления позволили обеспечить повьш1ение быстродействия устройства за счет последовательно-параллельного преобразования рабочего кода с выхода регистра 12 последовательного приближения в выходной двоичный код. 3 з.п. ф-лы, 7 ил. 1 табл. с (/)

77

fTJ f

ь

/77 г

77

/Ж-/;/ /

1К-11т г

iK fn)

л,

L

-:

3,

/ h

42

ч

У1

VZ

м 7П

лР

FL

..J

( НАЧАЛО J

,Y,S I I- -

ГЧ,1

нет

r-2t-i I y«,Y/5

.

Г 1

Е

П

аг- Vfff.Yw ,v/s

.Y4

«.«Лгг

//гл

Ли

Г У«-УМ

р-вГ

I Ур,Уй,

0

-50.

I Yft.

;Jff

Фиг. 7

( КОНЕЦ)

Редактор А. Козориз

Составитель В, Першиков Техред Л.Сердюкова

Заказ 7823/58Тираж 922Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Г. Решетник

| Электродвигатель со встроенным тахогенератором | 1979 |

|

SU788282A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-07—Публикация

1985-07-08—Подача