Известны делители частоты импульсов, содержащие регистр сдвига, схему «ИЛИ и схему «Запрет.

Предложенный делитель отличается от известных тем, что в нем выходы каждого разряда регистра соединены со входами схемы «ИЛИ, выход которой соединен с одним из входов схемы «Запрет, на другой ее вход подаются импульсы, частота которых подлежит делению, а выход схемы «Запрет соединен со входом записи первого разряда регистра. Это позволяет повысить стабильность коэффициента его деления.

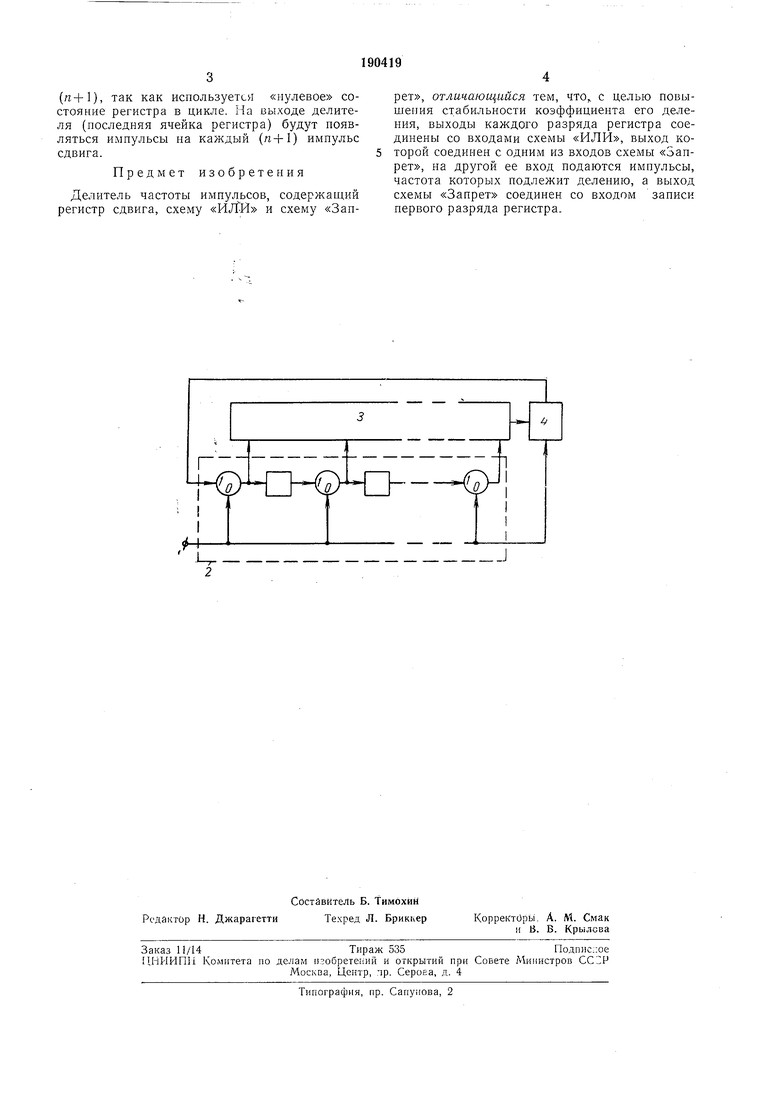

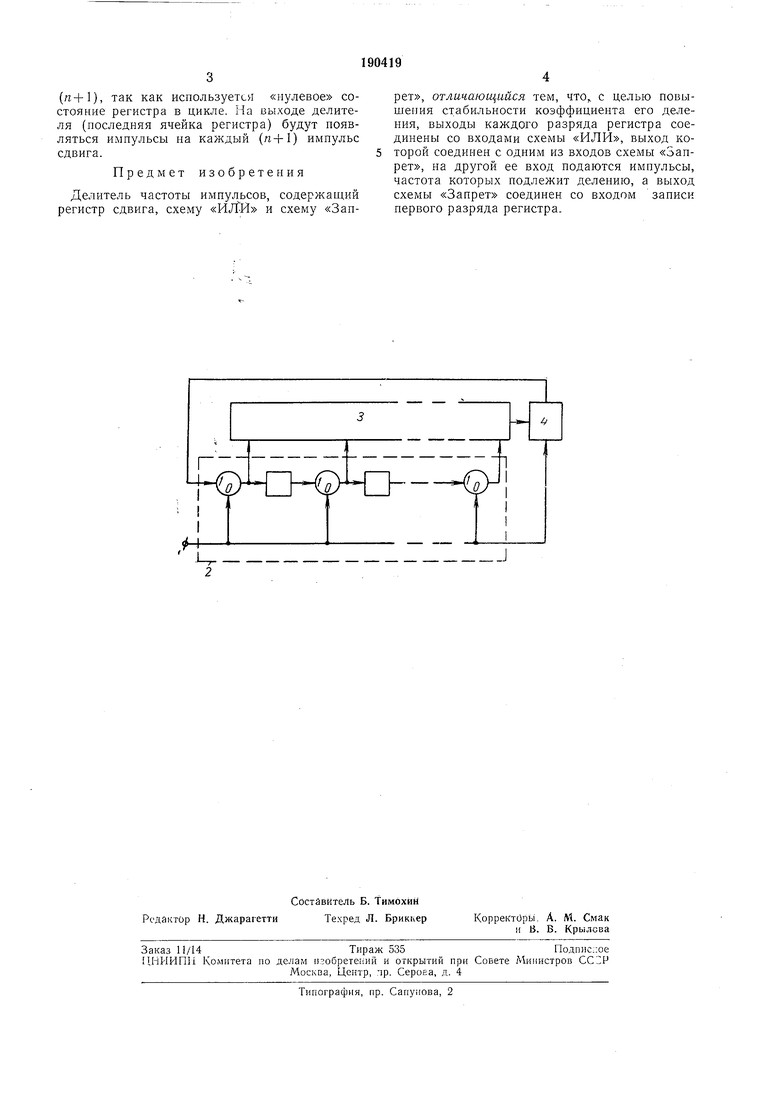

Схема описываемого делителя показана па чертеже.

Он построен таким образом, что, если регистр начинает свою работу из произвольного состояния (любое количество «единиц в регистре от О до д и в любой последовательности), в нем, по крайней мере, через (л-1) сдвигающих импульсов делитель переходит в нормальный режим работы.

В таком делителе случайная потеря основной «единицы или случайное приобретение от помех двух и более «единиц приводит только к временным сбоям.

В худшем случае через га периодов основной частоты он восстанавливает свою способность работать делителем.

ся в различных дискретных системах автоматики, вычислительной техники и т. п.

Схема работает следующим образом. На вход / поступают имнульсы, подлежащие делению, которые подаются в цепь сдвига регистра 2. Если при этом в регистре записана определенная комбинация «единиц (хотя бы одна единица), то эта комбинация сдвигается на одну позицию вправо. При этом на выходе

схемы ИЛИ 3 ноявляется сигнал отрицательной полярности, который постунает на схему запрета 4. Импульс со входа 1 на вход записи «единицы первого разряда регистра не проходит через схему 4. Так происходит до

тех пор, пока в регистре останется хотя бы одпа «единица. Но максимум через п имнульсо;; сдвига в регистре не останется ни одной «единицы. Тогда после сдвигающих импульсов на запрещающий вход схемы запрета 4 не

поступит сигнала со схемы «ИЛИ 5, и в первую ячейку регистра 2 запишется «единица.

Так как к приходу нового сдвигающего импульса регистр содержит одну «единицу, то больше запись производиться не будет. И

только через (/г + 1) импульсов сдвига снова в регистре не будет ни одной «единицы и опять произойдет запись «единицы на первую ячейку регистра. Таким образом, делитель, имеющий п ячеек

(n+1), так как используется «нулевое состояние регистра в цикле. На выходе делителя (последняя ячейка регистра) будут появляться импульсы па каждый (n+l) импульс сдвига.

Предмет изобретения

Делитель частоты импул ьсов, содержащий регистр сдвига, схему «ИЛЙ и схему «Запрет, отличающийся тем, что,, с целью повышения стабильности коэффициента его деления, выходы каждого разряда регистра соединены со входами схемы «ИЛИ, выход которой соединен с одним из входов схемы «Запрет, на другой ее вход подаются импульсы, частота которых подлежит делению, а выход схемы «Запрет соединен со входом записи первого разряда регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ДОСТОВЕРНОСТИ ИНФОРМАЦИИ, ПЕРЕДАВАЕМОЙ ЦИКЛИЧЕСКИМ КОДоМ | 1971 |

|

SU316204A1 |

| ИНТЕРПОЛЯТОР | 1970 |

|

SU272415A1 |

| АЯ ПАТЕНТНО- ^fт;;х!:ИЧЕС1:А:1 '"БИБЛИОТЕКА | 1966 |

|

SU181388A1 |

| Феррит-транзисторный делитель частоты | 1959 |

|

SU129389A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1973 |

|

SU430369A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1968 |

|

SU217705A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1972 |

|

SU427479A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU289448A1 |

| Симметричный делитель частоты импульсов | 1982 |

|

SU1089763A2 |

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ ДВОИЧНЬ[ХСООБЩЕНИЙ | 1967 |

|

SU197273A1 |

Даты

1967-01-01—Публикация