Известны устройства для перекодирования двоичного кода с постоянным весом в полный двоичный код на триггерах и логических элементах, содержащие входной и анализирующий узлы.

Предложенное устройство отличается от известных тем, что в нем к единичным цепям триггеров входного узла, кроме триггера старщего разряда и триггеров нескольких младщих разрядов, подключены схемы совпадения для фиксации номера первого ненулевого разряда, причем выходы схем совпадения и единичная цепь триггера старщего разряда присоединены ко входам вентильных анализаторов, выходы которых через схемы совнадений подключены к триггерам выходного узла.

Это позволило упростить устройство при больщом числе разрядов в исходном коде.

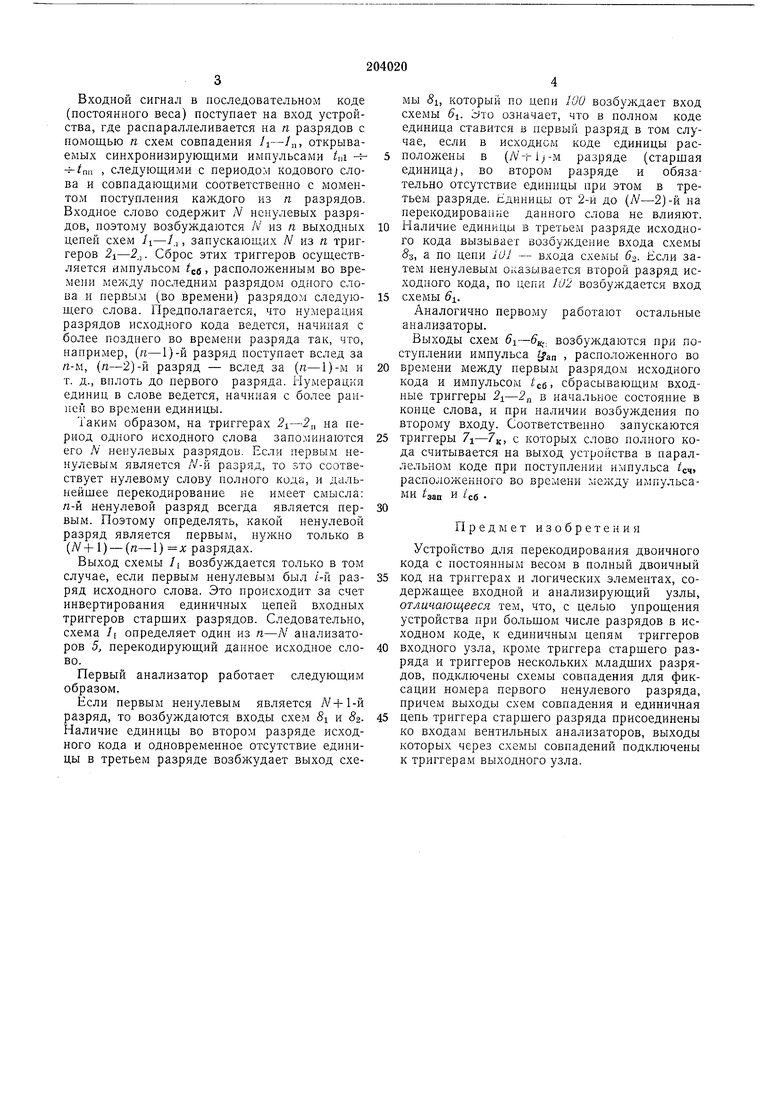

Схема устройства приведена на чертеже.

Входная часть устройства состоит из схем совпадения li-/„ и п триггеров 2i-2„, осуществляющих преобразование последовательного исходного кода в параллельный и запоминание его на время перекодирования одного слова. Выходные цепи триггеров - - 2п-1 подсоединены к схемам совпадения 3i-«Jn-N-i , на другой вход которых подключены через инверторы 4i-- „„N-S единичные цепи всех старших разрядов по отпощению к

данному. На второй вход схемы подключена нулевая цепь триггера 2„.

Назначение схем З - n-N-i и инверторов 4i-- n-N-z состоит в определении первого «i времени (старщего) ненулевого разряда.

Выходные цепи схем 3 -5n-N-i , а также единичная цепь триггера 2 подсоединены к анализаторам 5, ..., , состоящим в основном из схем совпадения на 2 и 3 входа. Назначение анализаторов заключается в сопоставлении первому и определенной части пар непулевых разрядов кода с постоянным веСОЛ1 одного или нескольких ненулевых разрядов в полном коде. К одному входу схем совпадения, образующих анализатор, подключена либо выходная цепь схемы 5; (для старщего анализатора - едипичная цепь триггера 2), либо выходная цепь предществующей

схемы совпадения анализатора. К другим входам этих схем совпадения (на чертеже не показаны) подключены единичные и нулевые цепи триггеров 2i-2„, причем в необходимых случаях это подключение производится через

инверторы.

Выходные цепи анализаторов подсоединены ко входам схем совпадения выходной части устройства, содержащей также триггеры 7i-7к.

Входной сигнал в последовательном коде (постоянного веса) поступает на вход устройства, где распараллеливается на п разрядов с помощью п схем совпадения /i-/„, открываемых синхронизирующими импульсами , следующими с периодом кодового слова и совпадающими соответственно с моментом поступления каждого из п разрядов. Входное слово содержит V ненулевых разрядов, поэтому возбуждаются Л из п выходных цепей схем /i-/,,, запускающих N кз п триггеров 2i-2,i. Сброс этих триггеров осуществляется импульсом tcs, располол енным во времени между последним разрядом одного слова и первым (во времени) разрядом следующего слова. Предполагается, что нумерация разрядов исходного кода ведется, начиная с более позднего во времени разряда так, что, например, (п-1)-й разряд поступает вслед за я-м, (п-2)-и разряд - вслед за (п-1)-м и т. д., вплоть до первого разряда. Нумерация единиц в слове ведется, начиная с более раниен во времени единицы.

Таким образом, на триггерах на нернод одного исходного слова запоминаются его N ненулевых разрядов. Если первым ненулевым является //-и разряд, то зто соотвествует нулевому слову полного кода, и дальнейщее перекодирование не имеет смысла: л-й ненулевой разряд всегда является первым. Поэтому определять, какой ненулевой разряд является первым, нужно только в ( 1) - (я-1) х разрядах.

Выход схемы /i возбуждается только в том случае, если первым непулевым был /-и разряд исходного слова. Это происходит за счет инвертирования единичных цепей входных триггеров старщих разрядов. Следовательно, схема /i определяет один из я-Л анализаторов 5, перекодирующий данное исходное слово.

Первый анализатор работает следующим образом.

Если первым ненулевым является УУ-ь1-й разряд, то возбуждаются входы схем Si и З. Наличие единицы во втором разряде исходного кода и одновременное отсутствие единицы в третьем разряде возбжудает выход схемы §1, который по цепи 100 возбуждает вход схемы 6i. Это означает, что в полном коде единица ставится в первый разряд в том случае, если в исходном коде единицы расположены в (A/-rij-M разряде (старщая единица;, во втором разряде и обязательно отсутствие единицы при этом в третьем разряде. ЕДИНИЦЫ от 2-й до (N-2) -и на перекодирование данного слова не влияют.

Наличие единицы в третьем разряде исходного кода вызывает возбуждение входа схемы §3, а по цепи 101 - входа схемы б. Если затем ненулевым оказывается второй разряд исходного кода, по цепи Ш2 возбуждается вход

схемы 1.

Аналогично первому работают остальные анализаторы.

Выходы схем 6i-6,, возбулсдаются при поступлении импульса tjaa расположенного во

времени между первым разрядом исходного кода и импульсом , сбрасывающим входные триггеры 2i-2п в начальное состояние в конце слова, и при наличии возбуждения по второму входу. Соответственно запускаются

триггеры 7i-ZK, с которых слово полного кода считывается па выход устройства в параллельном коде при поступлении импульса /сч расположенного во времени между импульсами /зап И /сб

Предмет изобретения

Устройство для перекодирования двоичного кода с постоянным весом в полный двоичный

код на триггерах и логических элементах, содерл :ащее входной и анализирующий узлы, отличающееся тем, что, с целью упрощения устройства при больщом числе разрядов в исходном коде, к единичным цепям триггеров

входного узла, кроме триггера старщего разряда и триггеров нескольких младщих разрядов, подключены схемы совпадения для фиксации номера первого ненулевого разряда, причем выходы схем совпадения и единичная

цепь триггера старщего разряда присоединены ко входам вентильных анализаторов, выходы которых через схемы совпадений подключены к триггерам выходного узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ПЕРЕКОДИРОВАНИЯ ДВОИЧИОГО КОДА В ДВОИЧНЫЙ код с постоянным ВЕСОМ | 1967 |

|

SU191895A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ С ПОСТОЯННЫМ ЧИСЛОМ «ЕДИНИЦ» | 1969 |

|

SU241110A1 |

| УСТРОЙСТВО для ПЕРЕКОДИРОВАНИЯ /г-РАЗРЯДНОГО | 1970 |

|

SU281897A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕКОДИРОВАНИЯ ДВОИЧНОГО КОДА С ПОСТОЯННЫМ ВЕСОМ В ПОЛНЫЙ ДВОИЧНЫЙ КОД | 1970 |

|

SU260963A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ | 2002 |

|

RU2215369C1 |

| МНОГОКАНАЛЬНЫЙ ИНФРАНИЖОЧАСТОТНЫЙ ЦИФРОВШ КОРРЕЛЯТОР | 1972 |

|

SU433486A1 |

| ЮЗНАЯ | 1973 |

|

SU370612A1 |

| Устройство для ввода информации | 1981 |

|

SU966682A1 |

| ШИФРАТОР | 1989 |

|

RU2033691C1 |

Даты

1967-01-01—Публикация