Изобретение относится к вычис- лительной технике и может быть использовано в системах обработки массивов информации.

Известно устройство для обмена данными, содержащее блок основной памяти, блок буферной памяти, блок сопряжения, кoм /Iyтaтop байтов, блок приема управляющего слова, регистр конечного адреса, регистр текущего адреса, сравнения, блок управления обменом П.

Однако для реализации блока управления обменом такого устройства требуются большие затраты оборудования и обмен информацией производится без учета ее статистических свойств, что увеличивает время обмена.

Наиболее близким к предлагаемому является устройство для ввода информации , содерх ащее -блок преобразования входных данных, блоки сжатия информации, состоящие из группы вентилей, регистров сдвига, преобразователей кодов и схемы селекции приз-наков, блок перераспределения информации, блок обмена информацией, блок анализа состояний регистров, блок управления 2.

Недостатками устройства являются большие аппаратурные затраты из-за сложности его реализации и необходимость дополнительного времени для кодирования и раскодирования передаваемой информации, что снижает пропускную способность канала обмена.

цель изобретения - сокращение аппаратурных затрат и повышения про10пускной способности путем уменьшения избыточности передаваемой ийформации.

Поставленная цель достигается тем, что в устройство, содержащее

15 информационный регистр, К блоков анализа состояния регистров, блок управления и блок преобразования информации, включающий К входных коммутаторов, К регистров сдвига и К

20 выходных коммутаторов, причем первые выходы блоков анализа состояния регистров подключены к группе входов блоков управления, вход которого соединен со входом тактовых импульсов

25 устройства, а выход - с выходом тактовых импульсов устройства, в блоке преобразования информации выход i-ro (i 1,К) входного коммутатора соединен с первым входом i-ro регистра

30 сдвига, первый выход которого соеди-.

нен с первым входом. 1-го выходногокоммутатора, введены .два дополнительных регистра сдвига,- блок коммутации выходного управляющего слова два входных коммутатора информации, К-обходных коммутаторов и блок приема управляющего слова, причем первый вход, второй и третий выходы i-ro блока анализа состояния регистра подключены соответственно к второму выходу i-ro регистра сдвига и первым входам i-x входного и выходного коммутаторов блока преобразования информации, вход-выход и второй вход i-ro регистра сдвига блока преобразования информации подключены соответственно к i-му входу-выходу информационного регистра и к выходу блока управления и первым входам дополнительных регистров сдвига и блока коммутации выходного управляющего слова, а выход - ко второму входу i-ro выходного коммутатора блока преобразования информации, -выход которого соединен со вторым входом (i+1)-ro входного коммутатора блока преобразования информации и первым входом 1+1)-го обходного коммутатора, второй и третий входы которого подключены соответственно к выходу i-ro обходного коммутатора и третьему входу (i+1)-го входного коммутатора, блока преобразования информации и к четвертЪмУ выходу (i + l) го блока анализа состояния регистра, второй и пятый выход которого соединены соответственно с -первым выходом блока приема управляющего слова и вторым входом блока коммутации выходного управляющего слова, первые входы первого и второго входных коммутаторов информации подключены к информационному входу устройства, вторые входы - соответственно ко второму и третьему выходам блока приема управляющего слова, первым и вторым входами подключенного соответс.твенно к входу тактовых импульсов устройства и выходу первого дополнительного регистра сдвига, второй вход которого соединен с выходом первого входного коммутатора информации, выход второго входного коммутатора информации подключен ко вторым входам первого входного коммутатора блока преобразования информации и первого обходного коммутатора, второй вход второго дополнительного регистра сдвига соединен с выходом К-го выходного коммутатора блока преобразования информации и выходом К-го обходного коммутатора, а третий вход и выход соответственно с выходом блока коммутации выходного управляющего .слова и информационным выходом устройства, а также тем, что блок приема управляющего слова содержит счетчик,

три элемента И, триггер, элемент НЕ , элемент задержки и группу элементов И, причем счётный вход счётчика соединен с выходом первого элемента И, а выходы - с группой входов второго элемента И,, выход которого,и выход элемента НЕ подключены к соответст вующим входам триггера, первым выходом соединенного с третьим выходом блока и первым входом третьего элемента И, второй вход которого является вторым входом блока и подключен через элемент задержки ко вторым выходам триггера и блока и первому входу первого элемента И, второй вход которого соединен с первым входом блока и входом элемента НЕ, первые входы элементов И группы подключены ко второму входу блока, вторые входы -/к выходу третьего элемента И, а выходы - к первому выходу блока.

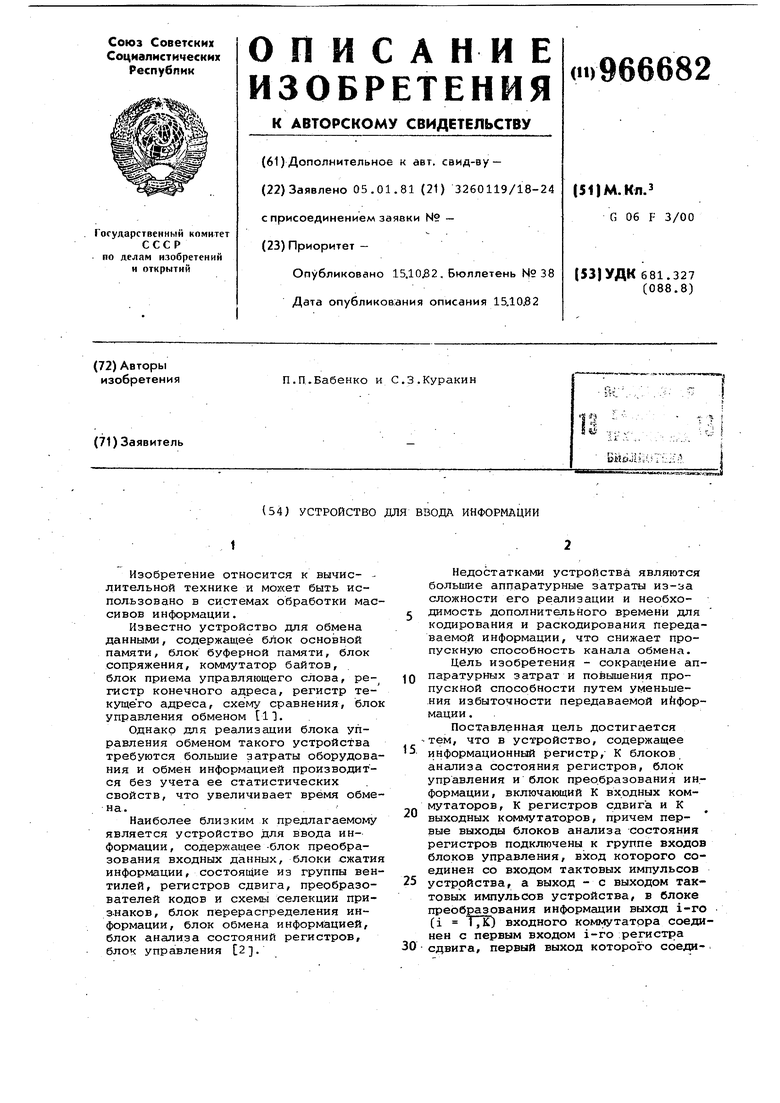

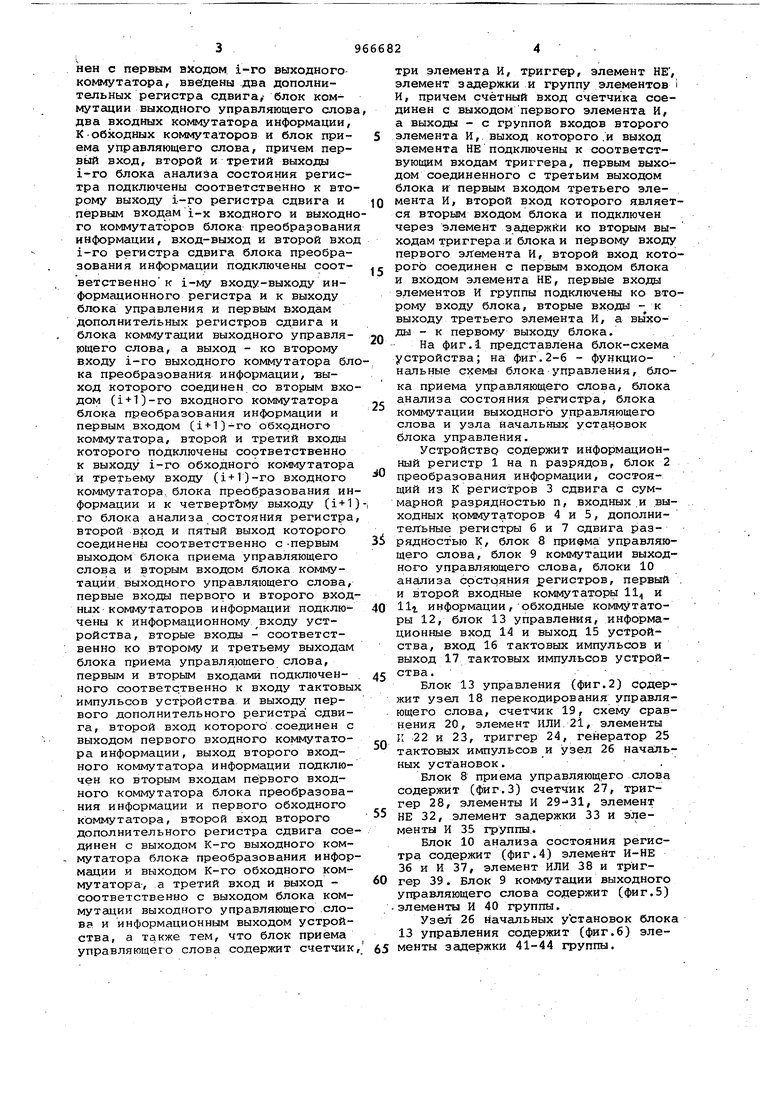

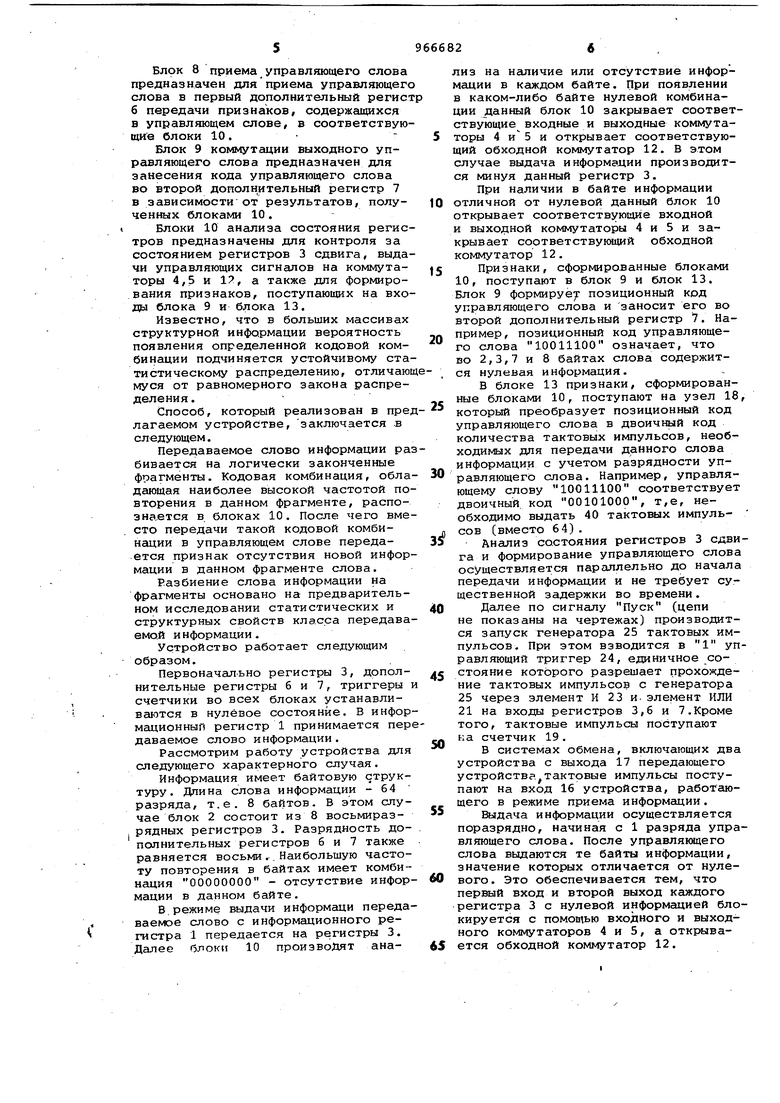

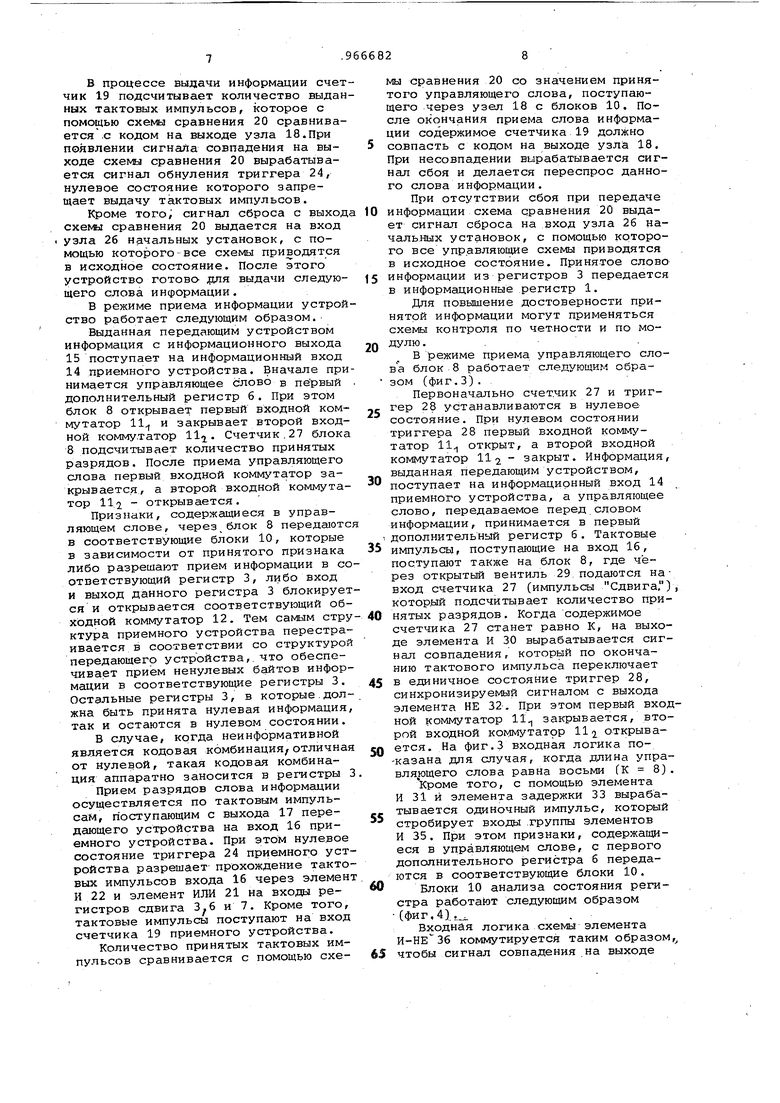

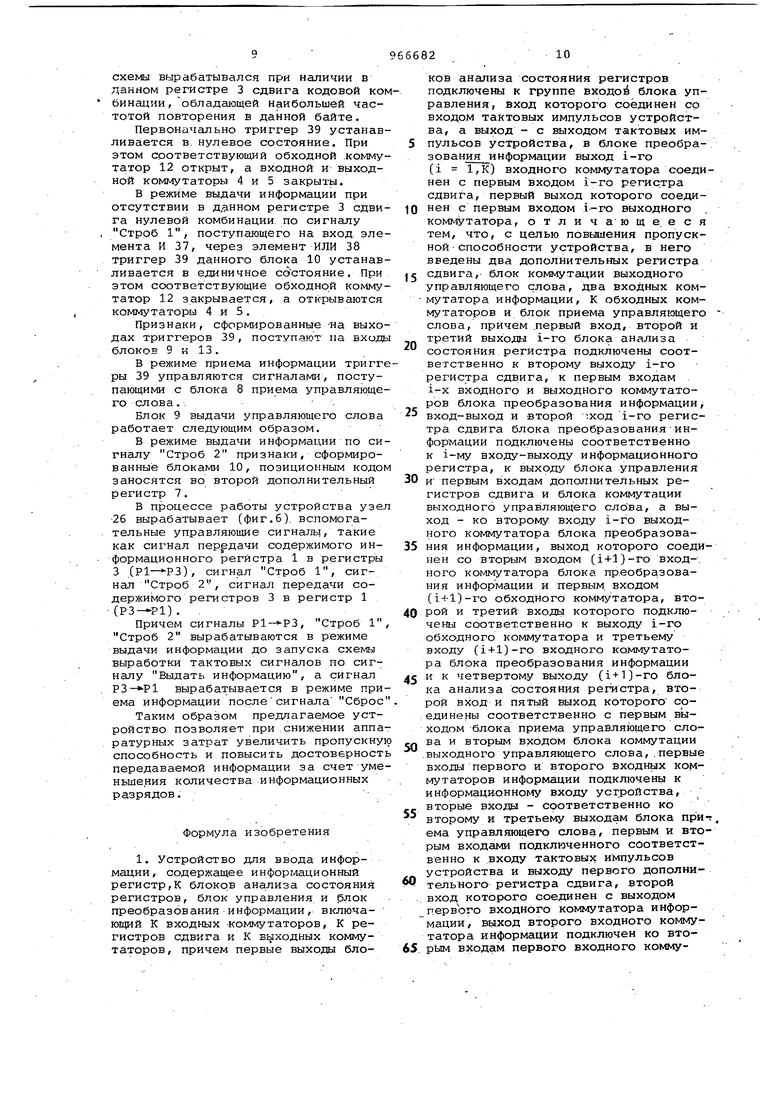

На фиг.1 представлена блок-схема устройства; на фиг.2-6 - функциональные схемы блока управления, блока приема управляющего слова, блока анализа состояния регистра, блока коммутации выходного управляющего слова и узла начальных установок блока управления.

Устройство содержит информационный регистр 1 на п разрядов, блок 2 преобразования информации, состоящий из К регистров 3 сдвига с суммарной разрядностью п, входных и выходных коммутаторов 4 и 5, дополнительные регистры 6 и 7 сдвига разрядностью К, блок 8 приема управляющего слова, блок 9 коммутации выходного управляющего слова, блоки 10 анализа состояния регистров, первый и второй входные коммутаторы 11 и 111 информации,Обходные коммутаторы 12, блок 13 управления, информационные вход 14 и выход 15 устройства, вход 16 тактовых импуЛьсов и выход 17 тактовых импульсов устройства.

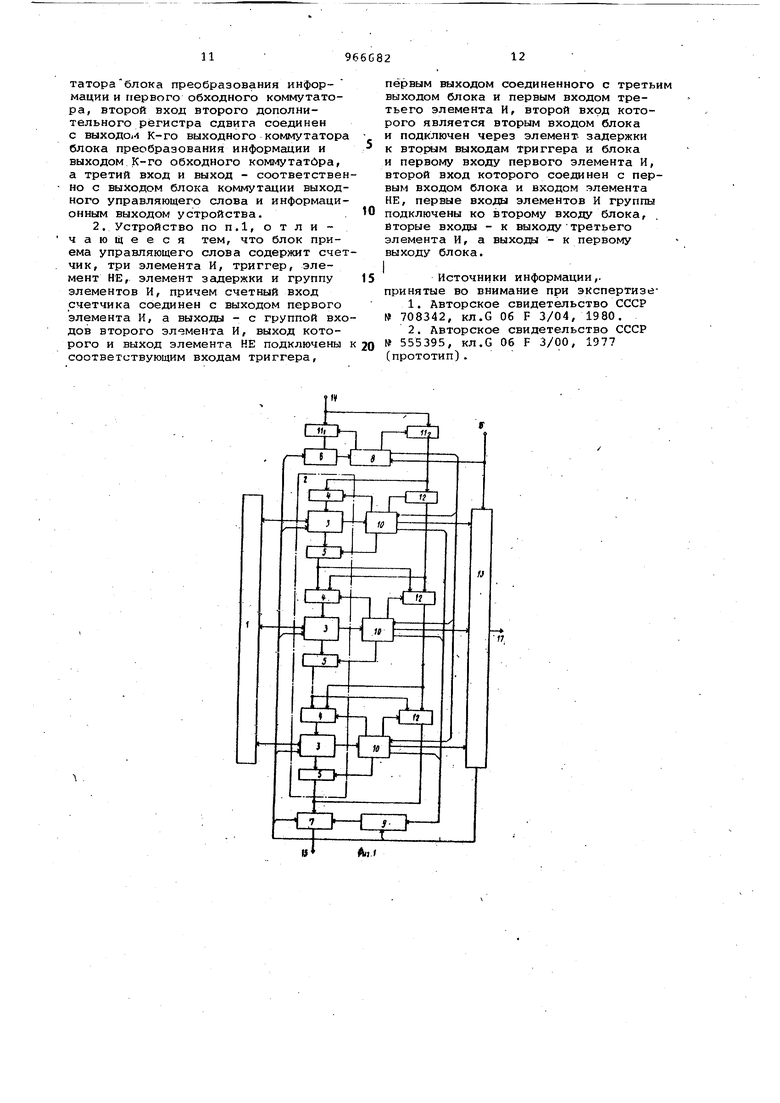

Блок 13 управления {фиг.2) содержит узел 18 перекодирования управляющего слова, счетчик 19, схему сравнения 20, элемент ИЛИ.21, элементы И 22 и 23, триггер 24, генератор 25 тактовых импульсов и узел 26 начальных установок.

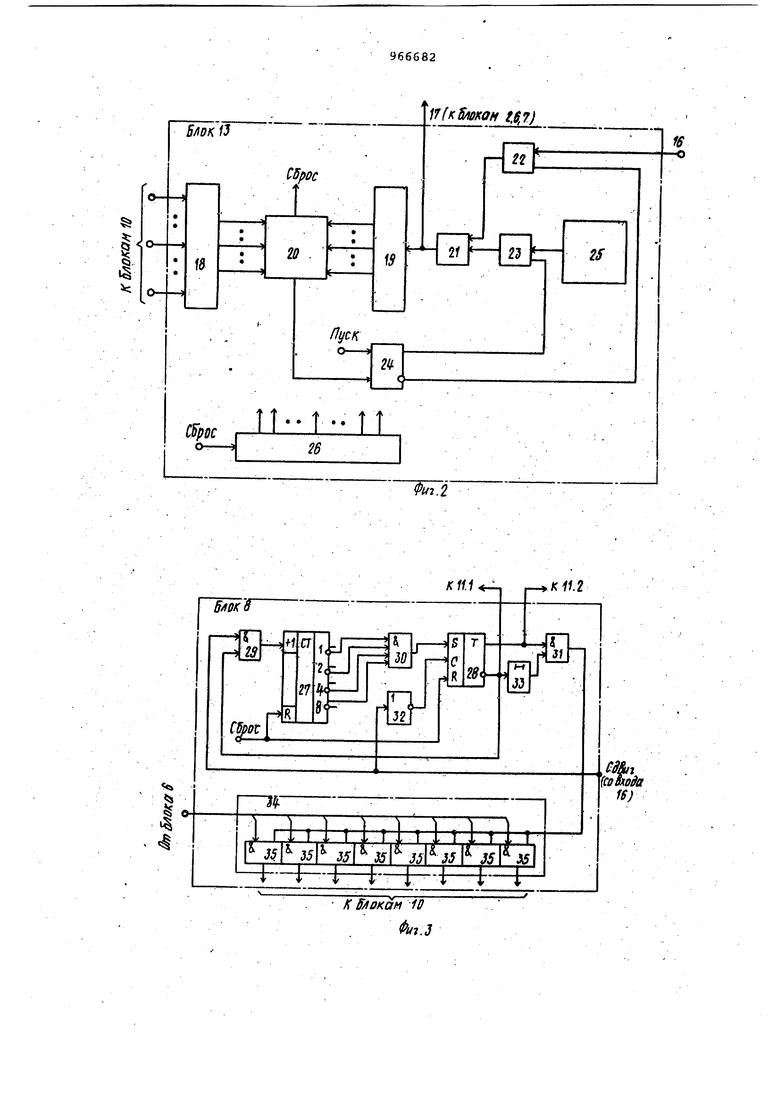

Блок 8 приема управляющего слова содержит (фиг.3) счетчик 27, триггер 28, элементы И 29-31, элемент НЕ 32, элемент задержки 33 и э лементы И 35 группы..

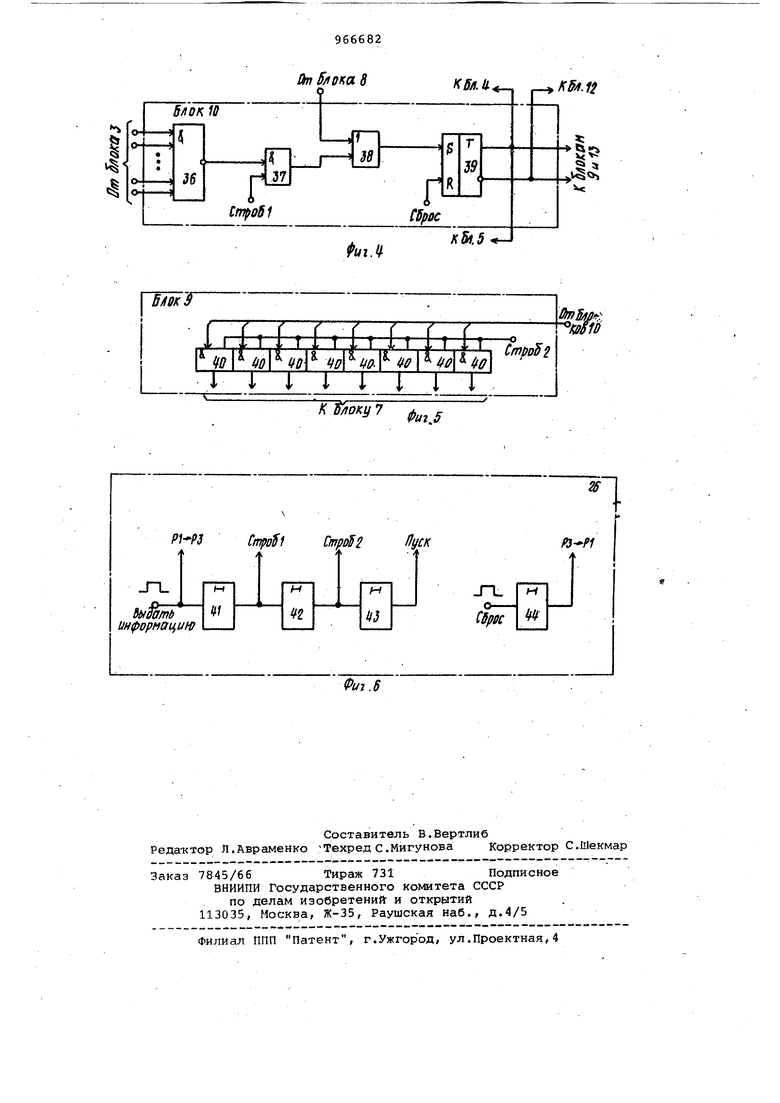

Блок 10 анализа состояния регистра содержит (фиг.4) элемент И-НЕ 36 и И 37, элемент ИЛИ 38 и триггер 39. Блок 9 коммутации выходного управляющего слова содержит (фиг.5) - элементы И 40 группы.

Узел 26 Начальных установок блока 13 управления содержит (фиг.6) элементы задержки 41-44 группы.

Блок 8 приема управляющего слова предназначен для приема управляющего слова в первый дополнительный регист 6 передачи признаков, содержащихся в управляющем слове, в соответствующие блоки 10. Блок 9 коммутации выходного управляющего слова предназначен для занесения кода управляющего слова во второй дополнительный регистр 7 в зависимости от результатов, полученных блоками 10.

Блоки 10 анализа состояния регистров предназначены для контроля за состоянием регистров 3 сдвига, выдачи управляющих сигналов на коммутаторы 4,5 и 13, а также для формирования признаков, поступающих на входы блока 9 и блока 13.

Известно, что в больших массивах структурной информации вероятность появления определенной кодовой комбинации подчиняется устойчивому статистическому распределению, отличающмуся от равномерного закона распределения .

Способ, который реализован в пред лагаемом устройстве, заключается в следующем.

Передаваемое слово информации разбивается на логически законченные фрагменты. Кодовая комбинация, обладакядая наиболее высокой частотой повторения в данном фрагменте, распознается в блоках 10. После чего вместо передачи такой кодовой комбинации в управляющем слове передается признак отсутствия новой информации в данном фрагменте слова.

Разбиение слова информации на фрагменты основано на предварительном исследовании статистических и структурных свойств класса передаваемой информации.

Устройство работает следующим образом.

Первоначально регистры 3, дополнительные регистры 6 и 7, триггеры и счетчики во всех блоках устанавливгиотся в нулевое состояние. В информационный регистр 1 принимается передаваемое слово информации.Рассмотрим работу устройства для следующего характерного случая.

Информация имеет байтовую структуру. Длина слова информации - 64 разряда, т.е. 8 байтов. В этом случае блок 2 состоит из 8 восьмиразрядных регистров 3. Разрядность дополнительных регистров 6 и 7 также равняется восьми..Наибольшую частоту повторения в байтах имеет комбинация 00000000 - отсутствие информации в данном байте.

В. режиме выдачи информаци передаваемое слово с информационного регистра 1 передается на регистры 3. Далее блок 10 производят анаЛИЗ на наличие или отсутствие информации в каждом байте. ПРИ появлении в каком-либо байте нулевой комбинации данный блок 10 закрывает соответствующие входные и выходные коммутаторы 4 и 5 и открывает соответствующий обходной коммутатор 12. В этом случае выдача информадии производится минуя данный регистр 3.

При наличии в байте информации отличной от нулевой данный блок 10 открывает соответствующие входной и выходной коммутаторы 4 и 5 и закрывает соответствукиций обходной коммутатор 12.

Признаки, сформированные блоками 10, поступают в блок 9 и блок 13. Блок 9 формируем позиционный код управляющего слова и заносит его во второй дополнительный регистр 7. Например, позиционный код управляющего слова 10011100 означает, что во 2,3,7 и 8 байтах слова содержится нулевая информация.

В блоке 13 признаки, сформированные блоками 10, поступают на узел 18 который преобразует позиционный код управляющего слова в двоичный код количества тактовых импульсов, необходимых для передачи данного слова информации с учетом разрядности управляющего слова. Например, управляющему слову 10011100 соответствует ДВОИЧНЫЙ, код 00101000, т,е, необходимо выдать 40 тактовых импульсов (вместо 64).

Анализ состояния регистров 3 сдвига и формирование управляющего слова осуществляется параллельно до начала передачи информации и не требует существенной задержки во времени.

Далее по сигналу Пуск (цепи не показаны на чертежах) производится запуск генератора 25 тактовых импульсов. При этом взводится в 1 управляющий триггер 24, единичное состояние которого разрешает прохождение тактовых импульсов с генератора 25 через элемент И 23 и-элемент ИЛИ 21 на входы регистров 3,6 и 7.Кроме того, тактовые импульсы поступают ка счетчик 19.

В системах обмена, включающих два устройства с выхода 17 передающего устройства тактовые импульсы поступают на вход 16 устройства, работающего в режиме приема информации.

Выдача информации осуществляется поразрядно, начиная с 1 разряда управляющего слова. После управляющего слова выдаются те байты информации, значение которых отличается от нулевого. Это обеспечивается тем, что первый вход и второй выход каждого регистра 3 с нулевой информацией блокируется с помощью входного и выходного коммутаторов 4 и 5, а открывается обходной коммутатор 12.

В процессе выдачи информации счетчик 19 подсчитывает количество выданных тактовых импульсов, которое с помощью схемы сравнения 20 сравнивается .с кодом на выходе узла 18.При появлении сигнала совпадения на выходе схемы сравнения 20 вырабатывается сигнал обнуления триггера 24, нулевое состояние которого запрещает выдачу тактовых импульсов.

Кроме того, сигнал сброса с выход схемы сравнения 20 выдается на вход узла 26 начальных установок, с помощью которого-все схемы приводятся в исходное состояние. После этого устройство готово для выдачи следующего слова информации.

В режиме приема информации устройство работает следующим образом.

Выданная передающим устройством информация с информационного выхода 15 поступает на информационный вход 14 приемного устройства. Вначале принимается управляющее слово в первый дополнительный регистр 6. При этом блок 8 открывает первый входной коммутатор 11 и закрывает второй входной комму.татор ll-j. Счетчик. 2 7 блока 8 подсчитывает количество принятых разрядов. После приема управляющего слова первый входной коммутатор закрывается, а второй входной коммутатор ll - открывается.

Признаки, содержащиеся в управляющем слове, через.блок В передаютс в соответствующие блоки 10, которые в зависимости от принятого признака либо разрешают прием информации в соответствующий регистр 3, либо вход и выход данного регистра 3 блокируется и открывается соответствующий обходной коммутатор 12. Тем самым стру ктура приемного устройства перестраивается в соответствии со структурой передающего устройства,, что обеспечивает прием ненулевых байтов информации в соответствующие регистры 3. Остальные регистры 3, в которые.должна быть принята нулевая информация, так и остаются в нулевом состоянии.

В случае, когда неинформативной является кодовая комбинация отличная от нулевой, такая кодовая комбинация аппаратно заносится в регистры 3

Прием разрядов слова информации осуществляется по тактовым импульсам, поступающим с выхода 17 передающего устройства на вход 16 приемного устройства. При этом нулевое состояние триггера 24 приемного устройства разрещает прохождение тактовых импульсов входа 16 через элемент И 22 и элемент ИЛИ 21 на входы регистров сдвига и 7. Кроме того, тактовые импульсы поступают на вход счетчика 19 приемного устройства.

Количество принятых тактовых импульсов сравнивается с помощью схемы сравнения 20 со значением принятого управляющего слова, поступающего через узел 18 с блоков 10. После окончания приема слова информации содержимое счетчика 19 должно со.впасть с кодом на выходе узла 18. При несовпадении вырабатывается сигнал сбоя и делается переспрос данного слова информации.

При отсутствии сбоя при передаче информации схема сравнения 20 выдает сигнал сброса на вход узла 26 начальных установок, с помощью которого все упр.авляющие схемы приводятся в исходное состояние. Принятое слово информации из регистров 3 передается в информационные регистр 1.

Для повышение достоверности принятой информации могут применяться схемы контроля по четности и по модулю. .

В режиме приема управляющего слова блок 8 работает следующим образом (фиг.3). ,

Первоначально счет.чик 27 и триггер 28 устанавливаются в нулевое состояние. При нулевом состоянии триггера 28 первый входной коммутатор 11 открыт, а второй входной коммутатор 112 закрыт. Информация выданная передающим устройством, поступает на информационный вход 14 приемного устройства, а управляющее слово, передаваемое перед словом информации, принимается в первый дополнительный регистр 6. Тактовце импульсы, поступающие на вход 16, поступают также на блок 8, где через открытьой вентиль 29 подаются навход счетчика 27 (импульсы Сдвига) который подсчитывает количество принятых разрядов. Когда содержимое счетчика 27 станет равно К, на выходе элемента И 30 вырабатывается сигнал совпадения, который по окончанию тактового импульса переключает в единичное состояние триггер 28, синхронизируемый сигналом с выхода элемента НЕ 32. При этом первый входной коммутатор 11 закрывается, второй входной коммутатор 11 открывается. На фиг.З входная логика по-казана для случая, когда длина управляк)щего слова равна восьми (К 8)

Кроме того, с помощью элемента И 31 и элемента задержки 33 вырабатывается одиночный импульс, который стробирует входы группы элементов И 35. При этом признаки, содержащиеся в управляющем слове, с первого дополнительного регистра 6 передаются в соответствующие блоки 10.

Блоки 10 анализа состояния регистра работают следующим образом (фиг.4) ,

Входная логика схемы элемента И-НЕЗб коммутируется таким образом чтобы сигнал совпадения .на выходе схемы вырабатывался при наличии в данном регистре 3 сдвига кодовой ко бинации, обладающей наибольшей частотой повторения в данной байте. Первоначально триггер 39 устанав ливается в. нулевое состояние. При этом соответствующий обходной .комму татор 12 открыт, а входной и выходной коммутаторы 4 и 5 закрыты. В режиме выдачи информации при отсутствии в д.нном регистре 3 сдви га нулевой комбинации по сигналу Строб 1, поступающего на вход эле мента И 37, через элемент ИЛИ 38 триггер 39 данного блока 10 устанав ливается в единичное состояние. При этом соответствующие обходной комму татор 12 закрывается, а открываются коммутаторы 4 и 5. Признаки, сформированные -на выхо дах триггеров 39, поступают на вход блоков 9 и 13. В режиме приема информации тригг ры 39 управляются сигналами, поступающими с блока 8 приема управляюще го слова. . . Блок 9 выдачи управляющего слова работает следующим образом. В режиме выдачи информации по си гналу Строб 2 признаки, сформированные блоками 10, позиционным кодо заносятся во второй дополнительный регистр 7. В процессе работы устройства узе 26 вырабатывает (фиг.6). вспомогательные управляющие сигналь, такие как сигнал передачи содержимого информационного регистра 1 в регистры 3 (), сигнал Строб 1, сигнал Строб 2, сигнал передачи содержимого регистров 3 в регистр 1 (РЗ-Р1). Причем сигналы , Строб 1 Строб 2 вырабатываются в режиме выдачи информации до запуска схемы выработки тактовых сигналов по сигналу Выдать информацию, а сигнал вырабатывается в режиме при ема информации послесигнала Сброс Таким образом предлагаемое устройство позволяет при снижении аппа ратурных затрат увеличить пропускну способность и повысить достоверност передаваемой информации за счет уме ньшения количества информационных разрядов. Формула изобретения 1. Устройство для ввода информации, содержащее информационный регистр,К блокрв анализа состояния регистров, блок управления и блок преобразования информации, включающий К входных -коммутаторов, К регистров сдвига и К выходных коммутаторов, причем первые выходы блоков анализа состояния регистров подключены к группе входой блока управления, вход которого соединен со входом тактовых импульсов устройства, а выход - с выходом тактовых импульсов устройства, в блоке преобразования информации выход i-ro (i IfK) входного коммутатора соединен с первым входом i-ro регистра сдвига, первый выход которого соединен с первым входом i--ro выходного коммутатора, о т л и ч аю щ е; е с я тем, что, с целью повышения пропускной способности устройства, в него введены два дополнительных регистра сдвига, блок коммутации выходного управляющего слова, два входных коммутатора информации, К обходных коммутаторов и блок приема управляющего слова, причем .первый вход, второй и третий выходы i-ro блока анализа состояния регистра подключены соответственно к второму выходу i-ro регистра сдвига, к первым входам i-x входного и выходного коммутаторов блока преобразования информации, вход-выход и -второй ход i-ro регистра сдвига блока преобразованияинформации подключены соответственно к i-му входу-выходу информационного регистра, к выходу блока управления И первым входам дополнительных регистров сдвига и блока коммутации выходного управляющего слова, а выход - ко второму входу i-ro выходного коммутатора блока преобразования информации, выход которого соединен со вторым входом (i+l)-ro вход-, ного коммутатора блока пр.еобразования информации и первым входом (i+l)-ro обходного коммутатора, второй и третий входы которого подключены соответственно к выходу i-ro обходного коммутатора и третьему входу (i+l)-ro входного коммутатора блока преобразования информации и к четвертому выходу (i+1)-ro блока анализа состояния регистра, второй вход и пятый выход которого соединены соответственно с первым выходом блока приема управляющего слова и вторым входом блока коммутации выходного управляющего слова,.первые входы первого и второго входных коммутаторов информации подключены к информационному входу устройства, вторые входы - соответственно ко второму и третьему выходам блока прит, ема управляющего слова первым и вторым входсции подключенного соответственно к входу тактовых импульсов устройства и выходу первого дополнительного регистра сдвига, второй вход которого соединен с выходом первЪго входного коммутатора информации, выход второго входного коммутатора информации подключен ко вторым входам первого входного коммутаторз блока преобразования информации и первого обходного коммутатора, второй вход второго дополнительного регистра сдвига соединен с выходом к-го выходного коммутатора блока преобразования информации и выходом К-го обходного коммутатйра, а третий вход и выход - соответствен но с выходом блока коммутещии выход ного управляющего слова и информационным выходом устройства. 2. Устройство по п.1, отличающееся тем, что блок приема управляющего слова содержит счет чик, три элемента И, триггер, элемент НЕ, элемент задержки и группу элементов И, причем счетный вход счетчика соединен с выходом первого элемента И, а выходы - с группой вхо дов второго элемента И, выход которого и выход элемента НЕ подключены соответствующим входам триггера. первым выходом соединенного с третьим выходом блока и первым входом третьего элемента И, второй вход которого является вторым входом блока и подключен через элемент задержки к вторым выходам триггера и блока и первому входу первого элемента И, второй вход которого соединен с первым входом блока и входом элемента НЕ, первые входы элементов И группы подключены ко второму входу блока, йторые входы - к выходутретьего элемента И, а выходы - к первому выходу блока. Источники информации,, принятые во внимание при экспертизе1.Авторское свидетельство СССР № 708342, кл.С Об F 3/04, 1980. 2.Авторское свидетельство СССР № 555395, кл.С 06 F 3/00, 1977 (прототип). 17{к5 кон t,S,7)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1985 |

|

SU1325453A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для аппаратурной трансляции языков программирования | 1985 |

|

SU1270766A1 |

| Устройство для преобразования форматов слов двоичной последовательности | 1988 |

|

SU1513436A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ АБОНЕНТОВ С ЦВМ | 1991 |

|

RU2018942C1 |

к ff/iOKaM -ID

&n S/ioKu 8

/r 7

Kff/i,

Авторы

Даты

1982-10-15—Публикация

1981-01-05—Подача