Известны устройства для перекодирования двоичного кода в двоичный код с постоянным весом, содержащие входной регистр, логические схемы И, ИЛИ, НЕ, дешифратор и выходной регистр.

Предложенное устройство отличается от известных тем, что в нем каждый единичный выход триггеров входного регистра, кроме триггера старшего разряда, соединен с одним из входов схем И, второй вход каждой схемы Я соединен с единичными выходами триггеров всех старших разрядов, а выходы схем И .соединены соответственно с дешифраторами, выходы которых через схемы И соединены с единичными входами триггеров выходного регистра.

Это упрошает устройство.

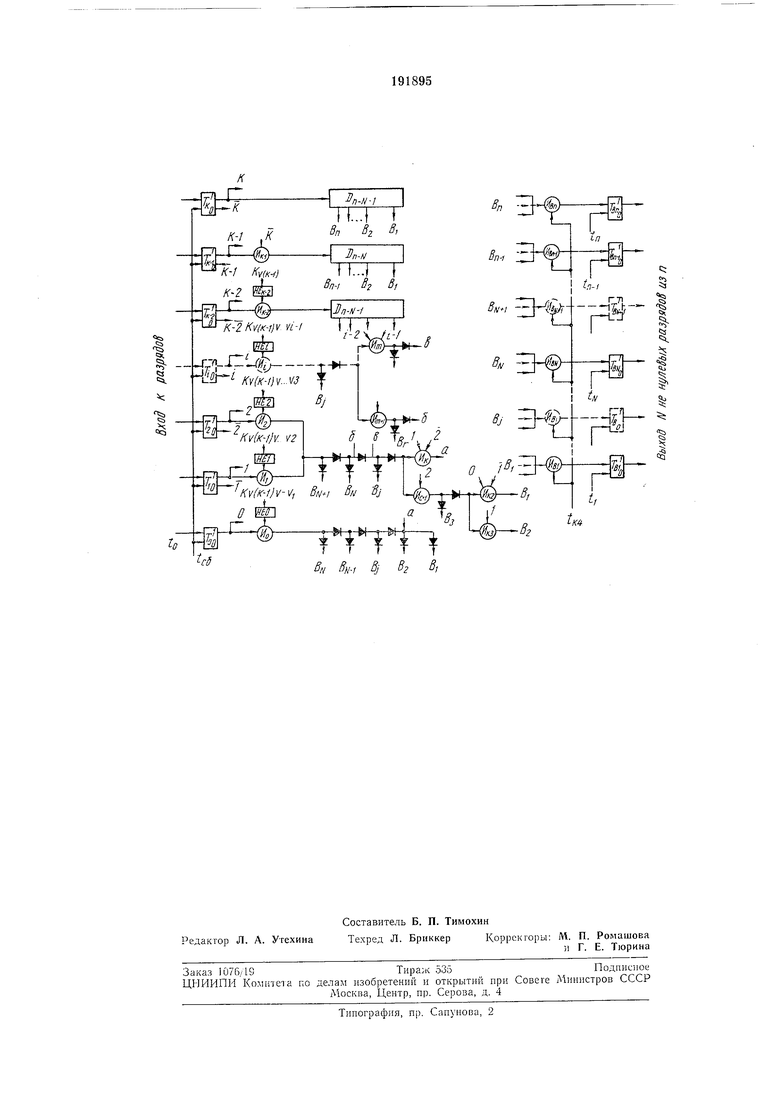

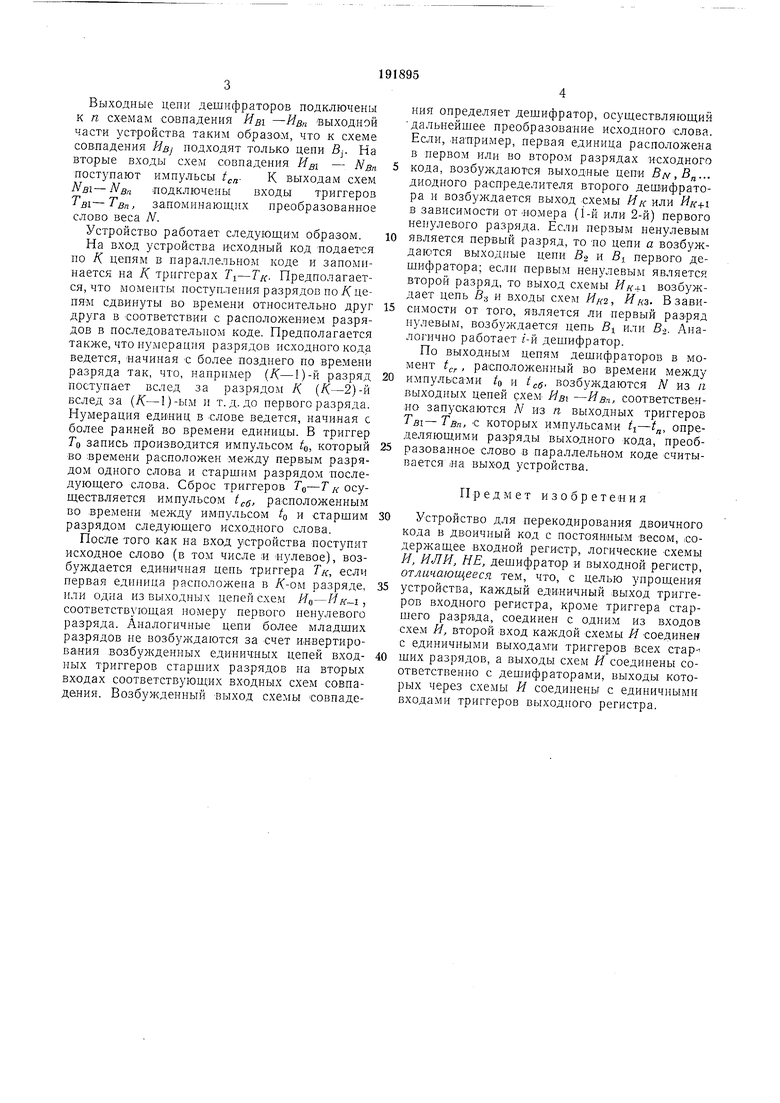

На чертеже показано предложенное устройство. Входная часть устройства состоит из К триггеров TI-TK, запоминающих /С-разрядное исходное слово, и триггера Го, фиксирующего отсутствие единиц на младших разрядах.

Выходные цепи /, 2,..., /С триггеров с нулевого по (К-i), соответствующие единичным состояниям триггеров, подсоединены к схемам Яо-Ик-1, на другие входы которых (кроме схемы ) через схемы подсоединены единичные цепи .всех старших разрядов по отиошению к данному. На второй

вход схемы подключен нулевой выход

К триггера Гд-. Схемы НЕо-НЕк-з. необходимы для фиксации номера первого по времени ненулевого разряда.

Каждая из выходных цепей схем совпадения Яо-Яд- 1 и единичная цепь триггера Т к подсоединены к соответствующему дешифратору Д, состоящему из диодного распределителя и анализатора.

Дешифратор имеет Л выходных цепей, подключенных к диодному распределителю и анализатору. Первая слева выходная цепь дешифратора соответствует первому пепулевому разряду в коде постоянного веса, вторая

цепь - второму разряду и т. д. до Л-й цепи. Первый дешифратор соответствует нулевому слову и состоит только из диодного анализатора, выходные цепикоторого устанавливают единицы Б разрядах с первого по

Л-й в преобразованном коде. Второй дешифратор соответствует располол ению первой единицы в первом пли во втором разрядах исходного кода. Выход а схемы Ял-второго дешифратора образует ветвь, совпадаюшую с ветвью первого дешифратора, поэтому они объединяются. АналогиЧ|НО выходы б, ... в, схем Я,„ , Я,„.ц и т. д. г-го дешифратора подсоединены к совпадающим ветвям младших дешифраторов

Выходные цепи дешифраторов подключены к п схемам совпадения Ив -Яд,, выходной части устройства таким образом, что к схеме совладения Ив, подходят только цепи Sj. На вторые входы схем совпадения Ив - Nвп поступают импульсы К выходам схем Nв1- вп. подключены входы триггеров ТBi-Твп, запоминающих преобразованное слово веса Л/.

Устройство работает следующим образом.

На вход устройства исходный код подается по К цепям в параллельном коде и запоминается на /С триггерах к- Предполагается, что моменты поступления разрядов по/С цепям сдвинуты во времени относительно друг друга в соответствии с расположением разрядов в последовательном коде. Предполагается также, что нумерация разрядов исходного кода ведется, «ачиная с более позднего по времени разряда так, что, например (К.-1)-й разряд поступает вслед за разрядом /С (К.-2)-и вслед за (К.-1)-ым и т. д. до первого разряда. Нумерация единиц в слове ведется, начиная с более ранней во времени единицы. В триггер Го запись производится импульсом 4, который во времени расположен между первым разрядом одного слова и старшим разрядом последующего слова. Сброс триггеров Т -Г/ осуществляется импульсом tcs, расположенным во времени между импульсом о и старшим разрядом следующего исходного слова.

После того как на вход устройства поступит исходное слово (в том числе и «злевое), возбуждается единичная цепь триггера Тк, если первая единица расположена в Д-ом разряде, или одна из выходных цепей схем Яо-ИK I , соответствующая номеру первого ненулевого разряда. Аналогичные цеии более младших разрядов не возбуждаются за счет инвертирования возбужденных единичных цепей входных триггеров старших разрядов на вторых входах соответствующих входных схем совладения. Возбужденный выход схемы совпадения определяет дешифратор, осуществляющий дальнейшее преобразование исходного слова. Если, .налример, первая единица расположена в первом или во втором разрядах исходного кода, возбуждаются выходные цепи BN,B... диодного распределителя второго дешифратора и возбуждается выход схемы И к или /-/л-+1 в зависимости от-номера (1-й или 2-й) первого ненулевого разряда. Если первым ненулевым является первый разряд, то цо цепи а возбуждаются выходные цепи В, и Si первого дещифратора; если первым ненулевым является второй разряд, то выход схемы Яя+1 возбуждает цепь Дз и входы схем Ял-а, Ялз. В зависимости от того, является ли первый разряд нулевым, возбуждается цепь В или В.. Аналогично работает г-й дешифратор.

По выходным цепям дешифраторов в момент t, расположенный во времени между импульсами /о и t , возбул даются Л из п выходных цепей схем HBI -Ив, соответственло запускаются N из п выходных триггеров TBI- Твп, С которых импульсами , определяющими разряды выходного кода, преобразованное слово в параллельном коде считывается .на выход устройства.

Предмет изобрете ния

Устройство для перекодирования двоичного кода в двоичный код с постоянным весом, содержащее входной регистр, логические схемы И, ИЛИ, НЕ, дешифратор и выходной регистр, отличающееся тем, что, с целью упрощения устройства, каждый единичный выход триггеров входного регистра, кроме триггера старшего разряда, соединен с одним из входов схем И, второй вход схемы И соединен с единичными выходами триггеров всех старших разрядов, а выходы схем Я соединены соответственно с дешифраторами, выходы которых через схемы Я соединены с единичными входами триггеров выходного регистра. K-2KV( 4L-I .It1 Iч7г -4)тKy(K-ijJ...V3 т т 4 лЛKv(, BN B/j Bj О --,- -fe4--j-. ТТт Sf, 4-/ 4 -V:: S ,12 -, ©-х Вп Э И--- -- 3Bj fek-J Г I . ,/.-Ibf+-i§- /о)--и, /a)

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ С ПОСТОЯННЫМ ЧИСЛОМ «ЕДИНИЦ» | 1969 |

|

SU241110A1 |

| УСТРОЙСТВО для ПЕРЕКОДИРОВАНИЯ ДВОИЧНОГО КОДА | 1967 |

|

SU204020A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО БЕЗЫЗБЫТОЧНОГО КОДА В ДВОИЧНЫЙ КОД ПОСТОЯННОГОВЕСА | 1970 |

|

SU282750A1 |

| Устройство для кодирования и декодирования последовательного кода с коррекцией одиночных ошибок | 1976 |

|

SU732877A1 |

| УСТРОЙСТВО для ПЕРЕКОДИРОВАНИЯ /г-РАЗРЯДНОГО | 1970 |

|

SU281897A1 |

| Преобразователь код-временной интервал | 1983 |

|

SU1106011A1 |

| Устройство для преобразования кодов с одного языка на другой | 1988 |

|

SU1522237A1 |

| Преобразователь сдвига фазы в код | 1983 |

|

SU1104565A1 |

| Преобразователь двоичного кода в перестановочный код | 1977 |

|

SU656053A1 |

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1270897A1 |

Даты

1967-01-01—Публикация