В вычислительной технике известны параллельные накапливающие сумматоры на трехвходовых параметронах с трехфазной системой синхронизации, имеющие раздельные входы для ввода двух с.тагаемых.

Предлагаемый сумматор имеет следующие отличия. Входы параметронов первой и второй фаз синхронизации соответственно триггеров первого и второго разрядов каждой трехразрядной группы соединены с щинами приема первого слагаемого и цепью гапиения сумматора. Вход нараметрона третьей фазы триггера третьего разряда каждой группы связан с цепью гащения. Один вход параметронов второй, третьей и первой фаз соответственно триггеров первого, второго и третьего разрядов соединен с щиной приема второго слагаемого в даппый разряд, а другой вход, инверсный с выходом параметрона образования переноса в данном разряде. Один вход параметрона третьей и первой фаз соответственно триггеров первого и второго разрядов группы через синхронизирующий параметрон подключен к выходу параметрона образования переноса в предыдущем разряде, а другой вход, инверсный, соединен с выходом параметрона образования переноса в данном разряде. Один вход параметропа второй фазы триггера третьего разряда каждой группы связан с выходом параметропа, выполняющего функцию

«ИЛИ, входы которого соединены с шиной ввода первого слагаемого в третий разряд и с выходом нараметрона образования переноса второго разряда группы, а инверсный вход иараметрона второй фазы триггера третьего разряда группы подсоединен к выходу параметрона образования переноса третьего разряда. Выходы параметронов образования переноса третьего разряда всех групп соединены со входами схемы «ИЛИ фиксации окончания сложения чисел в сумматоре.

Это позволяет сократить число параметронов и обеспечить высокое быстродействие.

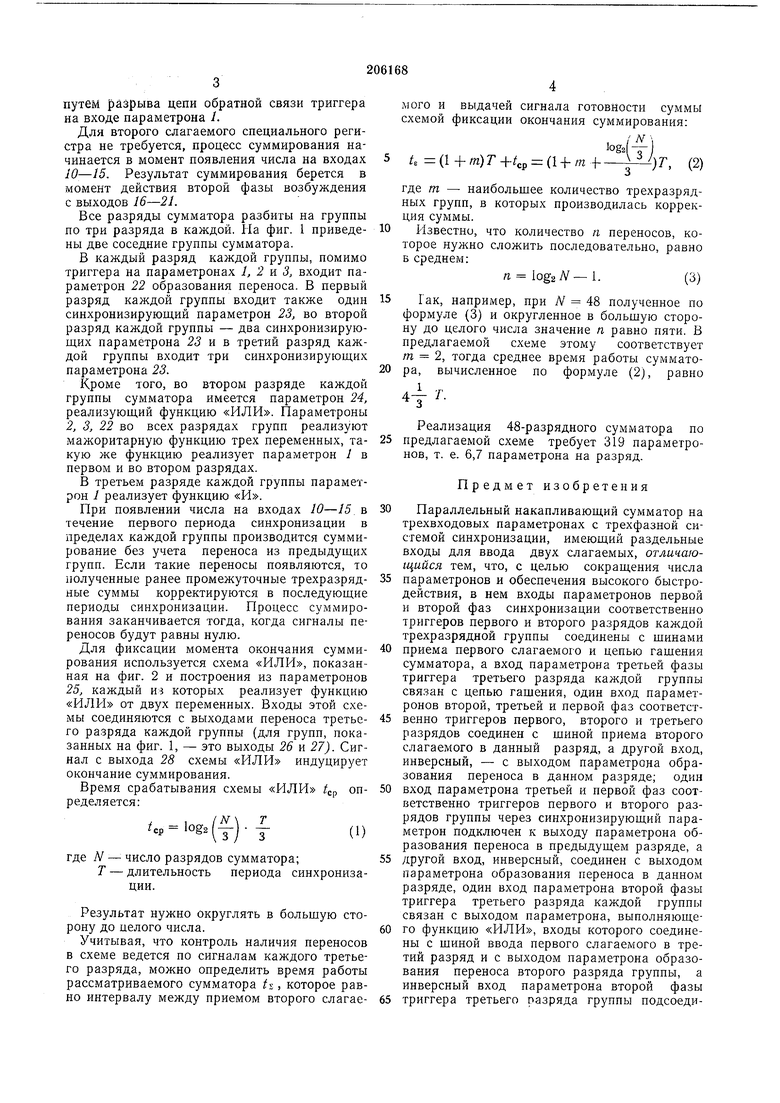

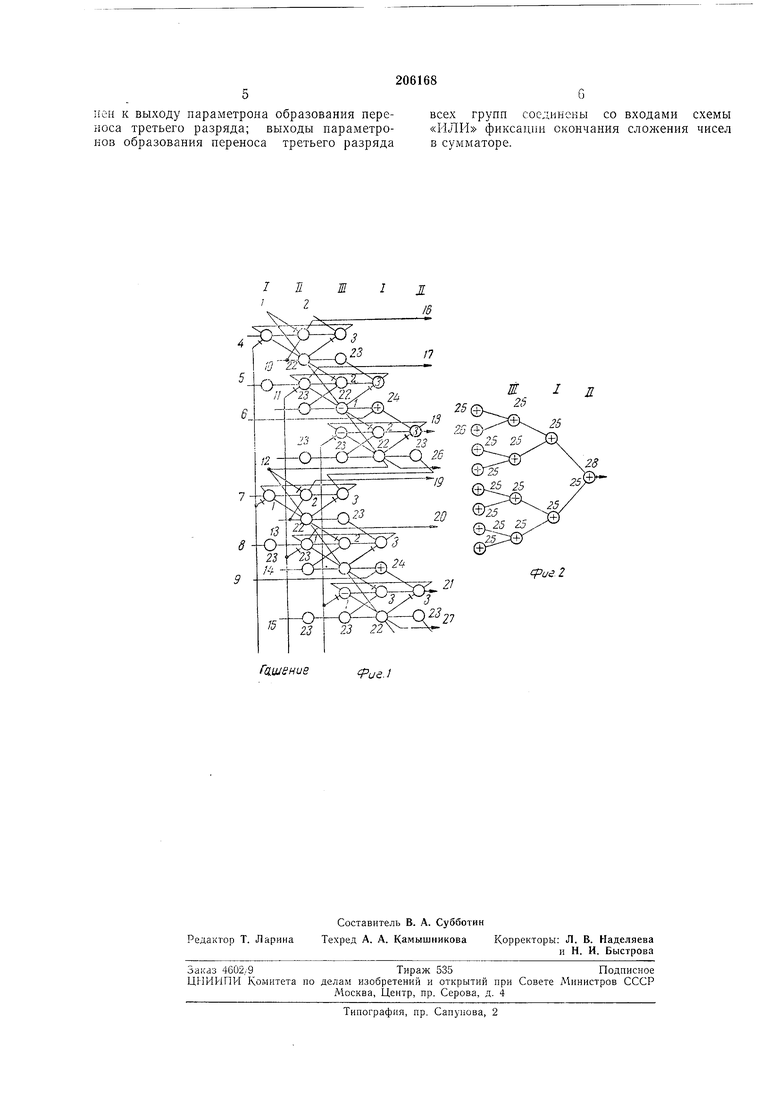

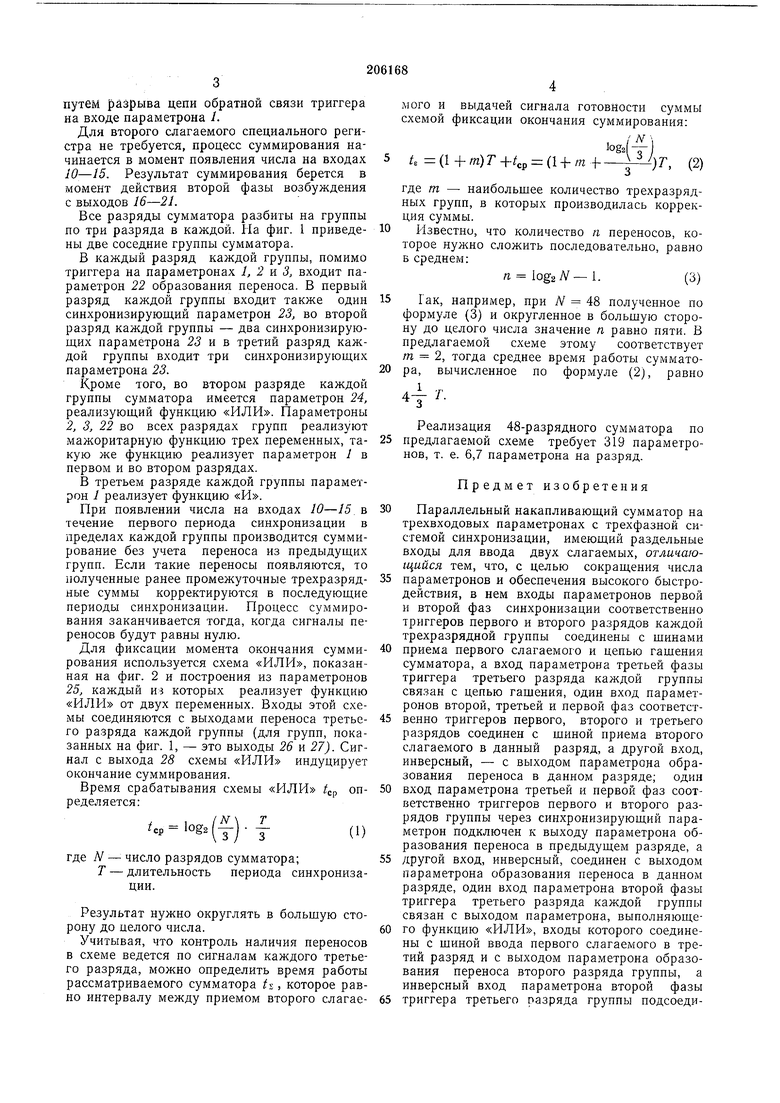

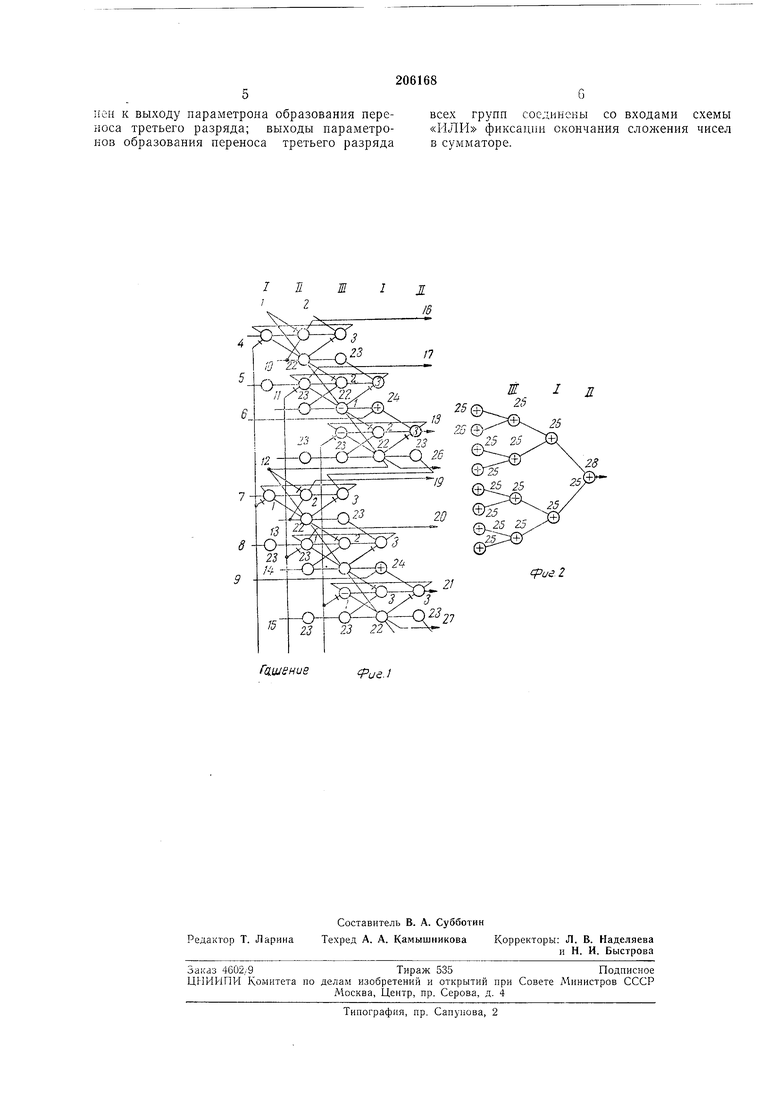

На фиг. I представлена блок-схема предлагаемого сумматора; на фиг. 2 - блок-схема дешифратора формирования сигнала окончания суммирования. Элементом схемы является нараметрон,

имеющий не более трех входных сигналов и допускающий нагрузку не более чем на пять входов. В схеме используют параметроны только одного типа; метод возбуждения трехфазный.

Хранение одного из слагаемых (или результата предыдущего суммирования) осуществляется в регистре, образованном триггерами на параметронах 1, 2 н 3. Ввод числа в этот регистр осуществлен через входы 4-9. Гашепутем разрыва цепи обратной связи триггера на входе параметрона /. Для второго слагаемого специального регистра не требуется, процесс суммирования начинается в момент появления числа на входах 10-15. Результат суммирования берется в момент действия второй фазы возбуждения с выходов 16-21. Все разряды сумматора разбиты на группы по три разряда в каждой. На фиг. 1 приведены две соседние группы сумматора. В каждый разряд каждой группы, помимо триггера на параметропах 1, 2 и 3, входит параметрон 22 образования переноса. В первый разряд каждой группы входит также один синхронизирующий параметрон 23, во второй разряд каждой груипы - два синхронизирующих параметрона 2 и в третий разряд каждой группы входит три синхронизирующих параметрона 23. Кроме того, во втором разряде каждой группы сумматора имеется параметрон 24, реализующий функцию «ИЛИ. Параметроны 2, 3, 22 во всех разрядах групп реализуют мажоритарную функцию трех переменных, такую же функцию реализует параметрон 1 в первом и во втором разрядах. В третьем разряде каждой группы параметрон 1 реализует функцию «И. При появлении числа на входах 10-15 в течение первого периода синхронизации в пределах каждой группы производится суммирование без учета переноса из предыдущих групп. Если такие переносы появляются, то полученные ранее промежуточные трехразрядные суммы корректируются в последующие периоды синхронизации. Процесс суммирования заканчивается тогда, когда сигналы переносов будут равны нулю. Для фиксации момента окончания суммирования используется схема «ИЛИ, показанная на фиг. 2 и построения из параметронов 25, каждый из которых реализует функцию «ИЛИ от двух переменных. Входы этой схемы соединяются с выходами переноса третьего разряда каждой группы (для групп, показанных на фиг. 1, - это выходы 26 и 27). Сигнал с выхода 28 схемы «ИЛИ индуцирует окончание суммирования. Время срабатывания схемы «ИЛИ 4р определяется: , , IN Т /ср Iog3 - - у где yV - число разрядов сумматора; Т - длительность периода синхронизации. Результат нужно округлять в большую сторону до целого числа. Учитывая, что контроль наличия переносов в схеме ведется по сигналам каждого третьего разряда, можно определить время работы рассматриваемого сумматора v , которое равно интервалу между приемом второго слагаеого и выдачей сигнала готовности суммы хемой фиксации окончания суммирования: -(fl 4 (1+т) (1-Ьяг+-)Т, (2) где т - наибольшее количество трехразрядных групп, в которых производилась коррекция суммы. Известно, что количество п переносов, которое нужно сложить последовательно, равно Б среднем: n ogzN-{.(3) Гак, например, при // 48 полученное по формуле (3) и округленное в большую сторону до целого числа значение п равно пяти. В предлагаемой схеме этому соответствует m 2, тогда среднее время работы сумматора, вычисленное по формуле (2), равно 4/. Реализация 48-разрядного сумматора по предлагаемой схеме требует 319 параметронов, т. е. 6,7 параметрона на разряд. Предмет изобретения Параллельный накапливающий сумматор на трехвходовых параметронах с трехфазной системой синхронизации, имеющий раздельные входы для ввода двух слагаемых, отличающийся тем, что, с целью сокращения числа параметронов и обеспечения высокого быстродействия, в нем входы параметронов первой и второй фаз синхронизации соответственно триггеров первого и второго разрядов каждой трехразрядной группы соединены с шинами приема первого слагаемого и цепью гашения сумматора, а вход параметрона третьей фазы триггера третьего разряда каждой группы связан с цепью гашения, один вход параметронов второй, третьей и первой фаз соответственно триггеров первого, второго и третьего разрядов соединен с шиной приема второго слагаемого в данный разряд, а другой вход, инверсный, - с выходом параметрона образования переноса в данном разряде; один вход параметрона третьей и первой фаз соответственно триггеров первого и второго разрядов группы через синхронизирующий параметрон подключен к выходу параметрона образования переноса в предыдущем разряде, а другой вход, инверсный, соединен с выходом параметрона образования переноса в данном разряде, один вход параметрона второй фазы триггера третьего разряда каждой группы связан с выходом параметрона, выполняющего функцию «ИЛИ, входы которого соединены с шиной ввода первого слагаемого в третий разряд и с выходом параметрона образования переноса второго разряда группы, а инверсный вход параметрона второй фазы

иен к выходу параметрона образования переноса третьего разряда; выходы параметроиоз образования переноса третьего разряда

всех групп соединены со входами схемы «11ЛИ фиксации окончания чисел в сумматоре.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| ДИНАМИЧЕСКИЙ СЧЕТЧИК НА ПАРАМЕТРОНАХ | 1970 |

|

SU279702A1 |

| ЭЛЕМЕНТ ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙСТРУКТУРЫ | 1972 |

|

SU432679A1 |

| "Одноразрядный десятичный сумматор в коде "5421" | 1988 |

|

SU1658143A1 |

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| Конвейерное вычислительное устройство | 1984 |

|

SU1213475A1 |

| Генератор циклов | 1981 |

|

SU995289A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

Гашениг

cpue.Z

fue.t

Даты

1967-01-01—Публикация