(54) ГЕНЕРАТОР ЦИКЛСШ

I

Изобретение относится к импульсной технике и предназначено для генерирования и 4пyльcныx сигналов с заданньм периодом следования..

Известно устройство для генерации пачек импульсов,содержащее многотактный генератор импульсов-, выполненныйна мультивибраторе, двоичнс счетчике и дешифраторе, коммутатор в виде кнопочного переключателя, генератор так- товых импульсов, двоичные счетчики. импульсов, задержки с дешифраторами,. датчик задержки, вьшолненный на мультивибраторе с синхронизирующим входом для внешнего запуска, ключи, тригге- tS ры, элементы И, ИЛИ II.

Существенны- недостатком устройства является то, что нмпульсы в пачке вырабатываются на частоте генератора 20 тактовых импульсов, т.е. диапазон перестройки периода следования выходных импульсов ограничбЕН.

Цель изобретения - расширение функциональных возможностей за счет рас-. 25 ширения диапазона перестройки периода следования импульсов.

Поставленная цель достигается тем, что в генератор циклов, содержащий блок синхронизации, основной регистр 30

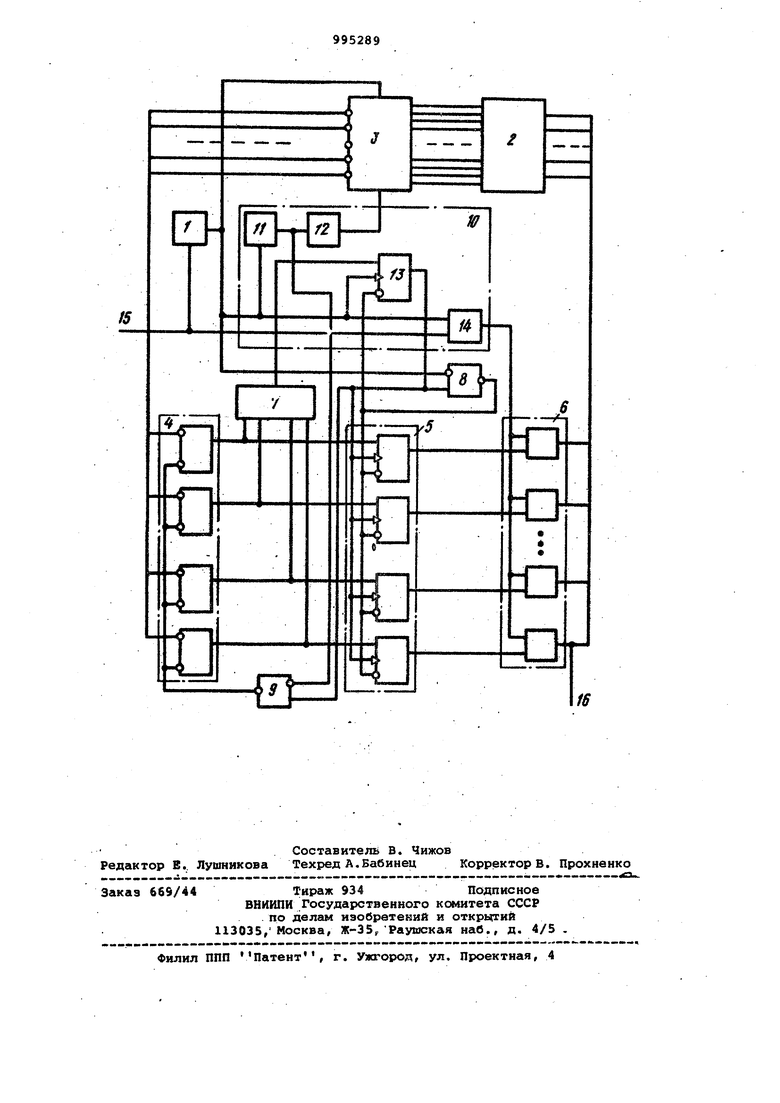

памяти, блок перестройки кодов, элемент ИЛИ, генератор эталонной частоты, вход которого соединен с первым входом блока синхронизации, второй вход которого соединен с выход(1 генератора эталонной частоты, третий вход блока синхронизации соединен с выходом элемента ИЛИ, введены накапливающий параллельный сумматор, дополнительный регистр памяти, блок элементов ИЛИ, два элемента И-НЕ, причем входы накапливающего параллельного суьматрра соединены с выходами блока перестройки кодов, входы которого соединены через блок элементов ИЛИ с выходами дополнительного регистра памяти, информационные входы которого соединены поразрядно с выходами основного регистра памяти и входами элемента ИЛИ, информационные входы основного регистра памяти соединены с выходами накапливающего параллельного сумматора, вход синхронизации накапливающего параллельного сумматора соединен с первым выходом блока синхронизации, второй выход которого соединен с вторыми входамиблока элементов ,ИЛИ, третий выход соединен с первым входсм первого элемента И-НЕ, выход :которого соединен с входом сброса,основного регистра памяти, второй вход соединен с четвертым выходом блока синхсониэации, входом синхронизации дополнительного регистра памяти и пер вым входом второго .элемента И-НЕ, вто рой вход которого подключен к выходу генератора эталонной частоты и входу переноса накап-ливающего параллельного сумматора, а выход соединен с -четвертым входом блока синхронизации и входом сброса дополнительного регистра памяти. На чертеже представлена структурная схема генератора циклов. Генератор циклов содержит генераTOD I эталонной частоты, блок 2 перестройки кодов, состоящий из га десятичных клавиЫных гребенок, каждая из которых имеет десять клавиш, один вход и четыре вьгхода, накапливающий параллельный сумматор 3, имеющий m инвертированных выходов переноса изстаршего разряда каждой тетрады, основной регистр 4 сдвига на КЗ-триггерах, дополнительный регис- р 5 сдви га на D-триггерах, блок 6 элементов ИЛИ, элемент ИЛИ 7, элементы И-НЕ 8 и 9,. блок 10 синхронизации, который состоит из элементов 11 и 12 задержки, D-триггера 13, блока 14 выделения одиночного импульса. На чертеже также показана шина 15 пуска и выход ная шина 16. Принцип работы генератора циклов заключается в следугадем. ( Генератор 1 эталонной частоты выр батьшает сигналы с частотой, f, которые поступают на входы синхронизации D-триггера 13 и блока 14 выделения одиночного импульса блока 10, инверс ный вход элемента И-НЕ 8, через элемент 11 задержки на инверсный вход элемента И-НЕ 9, на вход переноса су маторе 3 и через элементы 11 и 12 за держки на вход синхронизации суммато ра 3. Величина задержки элементов 11 и 12 обусловлена временем установлёНИИ Переходных процессов в сумматоре 3 и его входных цепях. Сумматор 3 вы полнен в частном случае по схеме параллельного двоичного сумматора комб национно-накапливающего типа, имеющег группу входов для приема двоичного кода второго слагаемого, сформирован ного потетрадно в блоке 2 перестройки на основании сигналов с выходов блока 6 элементов ИЛИ.Первое слагаемое хранится в сумматоре 3, Блок 2 перестройки обеспечивает установку десятичного кода К разрядностью m с целью перестройки генератора циклов на заданную частоту f, отличающуюся от эталонной частоты f на величину, определяемую выражением .n Uo-Ki) где К - цифра в 1-м разряде десятичного кода К. Установка десятичного кода К производится с помощью соответствующих клавиш на клавишных гребенках блока 2, на выходе которых образуются тетрады двоично-десятичного Кода. Соответствие между десятичным обозначением клавиш и получаемым двоичным кодом в тетраде следующее. Генератор 1 эталонной частоты запускается в работу сигналом пуска, подаваемым по шине 15 устройства в виде логической единицы в течение всего времени работы генератора циклов. После поступления сигнала пуска на управляющий вход блока 14 блока 10, на выходе последнего вырабатывается одиночный импульс на основании первого сигнала эталонной частоты f, который через блок б элементов ИЛИ в соответствии с установленными значениями на клавишах блока 2 перестройки формирует начальный код двоичнодесятичных тетрад, передаваемый по параллельным шинам на вход сумматора 3. Сумматор 3, ранее установленный в нулевое состояние, производит двоичное суммирование поступившего начального кода с единичным значением с входа переноса по сигналу на входе синхронизации и запоминает результат суммирования. По второму и последующим сигналам от генератора 1 эталонной частоты при сохранившемся сигнале пуска блок 14 не вырабатывает импульсов на выходе, поэтому при условии отсутствия переноса из старшего разряда любой тетрады в предыдущем такте суммирования начальный код с выхода блока 2 на вход сумматора 3 поступать не будет, а будет производиться суммирование числа, находящегося в сумматоре, с единичным значением с входа переноса и накопление результата в сумматоре 3. Так будет продолжаться до тех пор, пока не переполнится хотя бы одна из тетрад. При этом сигнал переноса из старшего разряда данной тетрады поступает череэ соответствующий инверсный выход сумматора 3 на вход установки в единичное состояние соответствующего триггера регистра 4 запоминается в нем и передается на информационный вход соответствующего р-триггера регистра 5, а через зглемент ИЛИ 7 на информационный вход Ь-триггера 13 блока 10.

, Следующим сигналом от генератора 1 р-триггер 13 устанавливается в еди ничное состояние, выходной сигнал ко торого переписывает сигнал .переноса в соответствующий D-триггер регистра

5, а через элемент И-НЕ 9, на инверсном входе которого сигнал от генератора 1 задерживается элементом 11 запержки, установив RS-триггеры регистра 4 в нулевое состояние, тем самьам подготовив их для приема следукмцих сигналов переноса or сумматора 3. Си нал с выхода соответствующего D-т йггера регистра 5 поступает через блок 6 элементов ИЛИ в блок 2 перестройки на формирование начального кода для восстановления переполненной тетрады По сигналу на входе.синхронизации сумматор 3 производит двоичное суммирование накопленного в нем результата с сигнале на входе переноса и войстановленньм начальным кодом соответству ющей тетрады в качестве второго слагаемого, производя дальнейшее накопление результата. ПЬ окончаний действия вышеуказанного сигнала с выхода генератора 1 выходной сигнал элемента И-НЕ 8 производит установку в нулевое состояние D-триггеров регистра 5 и. D-триггера 13 блока 10. Процесс накопления результата в сумматоре 3 продолжается до тех пор, пока не цереполнится все m двоично-десятичные тетрады при этом /сумматор 3 устанавливается в нулевое состояние, сигналы п ереноса из всех тетрад готовят цепи для восстановления начального кода второго слагаемого, а на шине 16 устройства появляется выходной сигнал, сформированными на последних триггерах регистров 4 и 5, на осно- . ваний сигнала переноса из старшей тетрады. .

В следующем цикле генерации выходного сигнала генератор циклов работает аналогичным образом.

После снятия,сигнала пуска, с шины 15 все узлы генератора циклов, содержащие запоминающие элементы, устанавливаются в нулевое состояние. Цепи установки в начальное нулевое состояние на схеме не показаны.

Предлагаемый генератор обеспечивает надежное восстановление начального кода- любой тетрады или комбинации тетрад, комплектующих заданный- блоком перестройки десятичный код К, в соответствии с сигналами переноса cy

Матора, при этом перестррйка частоты следования выходных сигналов весьма проста и обеспечивается установкой десятичного кода К в блоке перестройки. Сигнал на выходе генератора циклов может быть получен во всем диапазоне перестройки, начиная с значения эталонной частоты f до установленного с помощью блока перестройки значения. Так устраняется.существенный недостаток известных генераторов циклов, у которых в диапазоне частот (f -f/4m) выходной сигнал не может быть получен.В предлагаемом генераторе расширены функциональные возможности.

Формула изобретения

Генератор циклов, содержащий блок синхронизации, основной регистр памяти, блок перестройки кодов, элемент ИЛИ, генератор эталонной частоты, вход которого соединен с первым входом блока синхронизации,- второй вход которого соединен с выходом генератора эталонной частоты, третий вход блока синхронизации соединен с выходом элемента ИЛИ, отличающис я тем, что, с целью расширения функциональных возможностей, в него введены накапливающий параллельный сумматор, дополнительный регистр памяти, блок элементов ИЛИ, два элемента И-НЕ, причем входы накапливающего параллельного сумматора соединены с выходами блока перестройки кодов, входы которого соединены через блок элементов ИЛИ с выходами дополнительного регистра памяти, информационные входы которого соединены поразрядно с выходами основного регистра памяти и входами элемента ИЛИ, информационные входы основного регистра памяти соединены с выходами накапливающего параллельного сумматора, вход синхронизации накапливающего параллельного сумматора соединен с первым выходом блока синхронизации, второй выход которого соединен с вторьми входами блока элементов ИЛИ, третий выход соединен, с первьм входом первого элемента И-НЕ, выход которого соединен с входом сброса основного регистра памяти, а второй вход соединен с четвертым выходом блока синхронизации, входом синхронизации дополнительного регистра памяти и первым входом второго элемента И-НЕ, второй вход которого подклк«ен к выходу генератору эталонной частоты и входу переноса накапливающего параллельного сумматора, а выход соединен с четвертым в одом блока синхронизации и входом сброса дополнительного регистра памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 822325, кл. Н 03 К 3/64, 1979.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор циклов | 1978 |

|

SU744531A1 |

| Генератор циклов | 1981 |

|

SU964616A1 |

| Генератор циклов | 1979 |

|

SU877511A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Устройство для допускового контроля объекта | 1984 |

|

SU1246060A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Дискретное устройство синхронизации | 1979 |

|

SU786034A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

Авторы

Даты

1983-02-07—Публикация

1981-04-24—Подача