В известных многоканальны.х цифровых корреляторах, содержащих аналого-цифровые преобразователи, устройство умножения, группу коммутируемых накопительных элементов и устройство синхронизации, требуются более длинные реализации случайного процесса, чем это принципиально необходимо.

Для повышения быстродействия в предлагаемом корреляторе использован комбинированный способ задержки: путем запоминания дискреты сигнала и ее перемещения в сдвиговом регистре. При этом сдвиговый регистр имеег число каскадов больше одного, но меньше числа накопительных элементов.

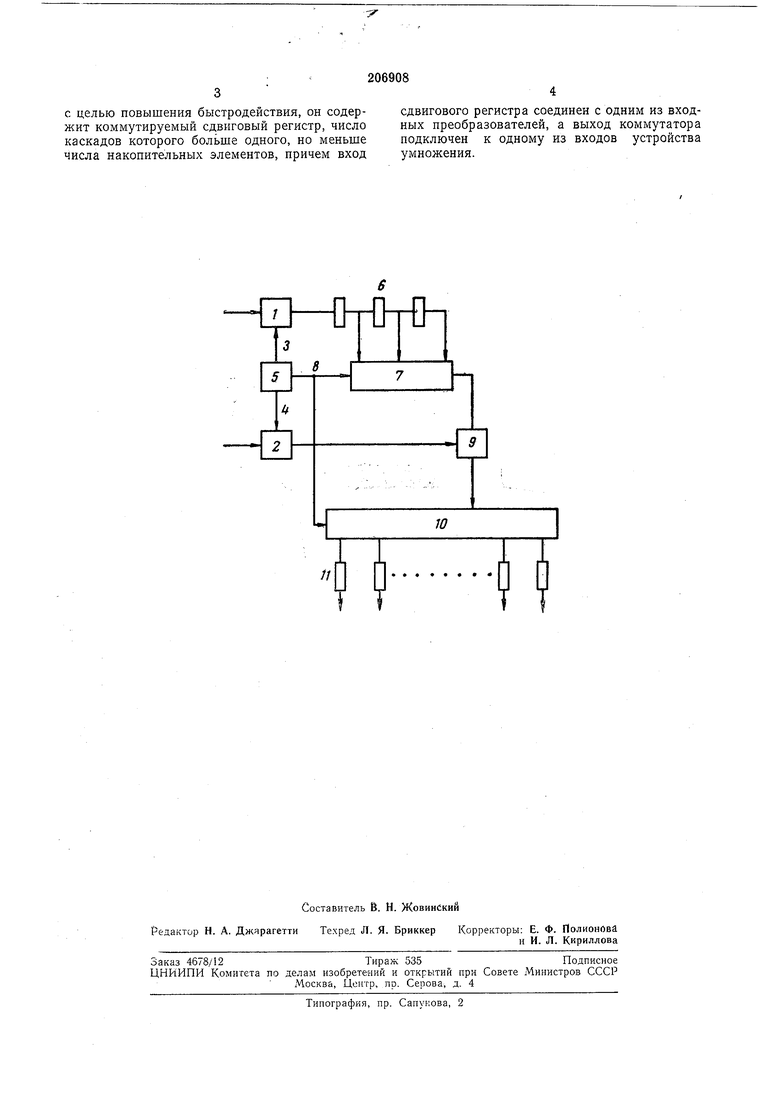

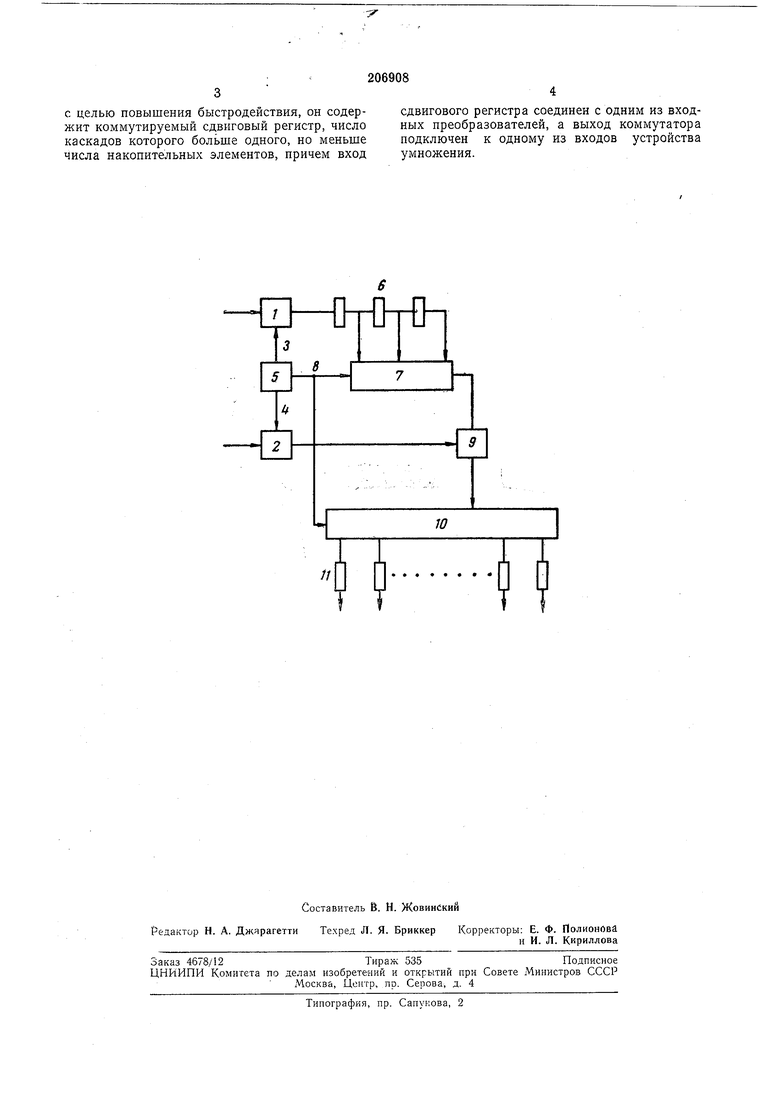

Па чертеже показана блок-схема описываемого коррелятора.

Он содержит два входных аналого-цифровых преобразователя 1 н 2, к которым подключены выходы 3 и 4 синхронизатора 5. Выход преобразователя связан с первым каскадом сдвигового регистра 6, выходы всех каскадов которого переключаются коммутатором 7. Его управляющий вход соединен с выходом 8 синхронизатора 5, а выход подключен к уетройству 9 перемножения, связанному вторы.м входом с аналого-цифровым преобразователем 2. Устройство перемножения через дополнительный коммутатор 10 связано с накопителями 11, число которых равно числу вычисляемых точек корреляционной функции.

Последняя вычисляется в течение определенного числа циклов работы. В начале каждого цикла происходит измерение входного сигкала преобразователем 1, измерение второго сигнала преобразователем 2 и сдвиг в регистре 6, причем в первый каскад регистра записывается измеренное значение сигнала. Одновременно открываются первые каналы коммутаторов 7 и 10. Вследствие этого на умножитель поступают измеренные значения сигналов с одинаковыми аргументами, а их произведения накапливаются в первом накопителе.

В последующих циклах работа протекает аналогично, но второй сигнал подается на умножитель с фиксированным аргументом, а первый благодаря срабатыванию регистра каждый цикл передается задержанным на время, пропорциональное количеству циклов.

Предмет изобретения

Многоканальный цифровой коррелятор с непосредственным вводом .данных для стационарных на интервале наблюдения процессов, содержащий аналого-цифровые преобразователи, уетройство умножения, группу коммутируемых накоиительных элементов и устройство синхронизации, отличающийся тем, что,

с целью повышения быстродействия, он содержит коммутируемый сдвиговый регистр, число каскадов которого больше одного, но меньше числа накопительных элементов, причем вход

сдвигового регистра соединен с одним из входных преобразователей, а выход коммутатора подключен к одному из входов устройства умножения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1970 |

|

SU275542A1 |

| АНАЛИЗАТОР СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU364944A1 |

| Цифровой коррелятор | 1976 |

|

SU610117A1 |

| Фурье-коррелятор | 1983 |

|

SU1164731A1 |

| КОРРЕЛЯТОР | 1972 |

|

SU424153A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1970 |

|

SU273524A1 |

| Устройство для вычисления спектра сигналов | 1986 |

|

SU1383392A1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

| Цифровой коррелятор | 1990 |

|

SU1824642A1 |

Даты

1968-01-01—Публикация