1

Предлагаемое изобретение относится к области специализированных средств вычислительной техники и предназначено для нахождения оценок корреляционных функций случайных процессов.

Известны параллельные цифровые корреляторы, содержащие регистр сдвига, первый коммутатор, синхронизатор, первый и второй выходы которого подключены к управляющим входам соответственно первого и второго аналого-цифровых преобразователей, входы которых подключены к соответствующим входам коррелятора, выход второго преобразователя соединен с информационным входом умножителя, третий выход синхронизатора соединен с управляющими входами умножителя и второго коммутатора, инфор,мационный вход которого соединен с выходом умножителя, а выходы второго комутатора подключены через соответствующие накопители к выходам коррелятора.

Подобные корреляторы имеют тот недостаток, что число входов первого коммутатора равно числу каскадов регистра сдвига. Такой коммутатор сложен, особенно, если он коммутирует многоразрядные числа и имеет больщое число входов.

Целью изобретения является упрощение коррелятора путем сокращения числа входов

первого коммутатора до двух независимо от числа каскадов регистра сдвига.

Эта цель достигается за счет изменения места включения первого коммутатора.

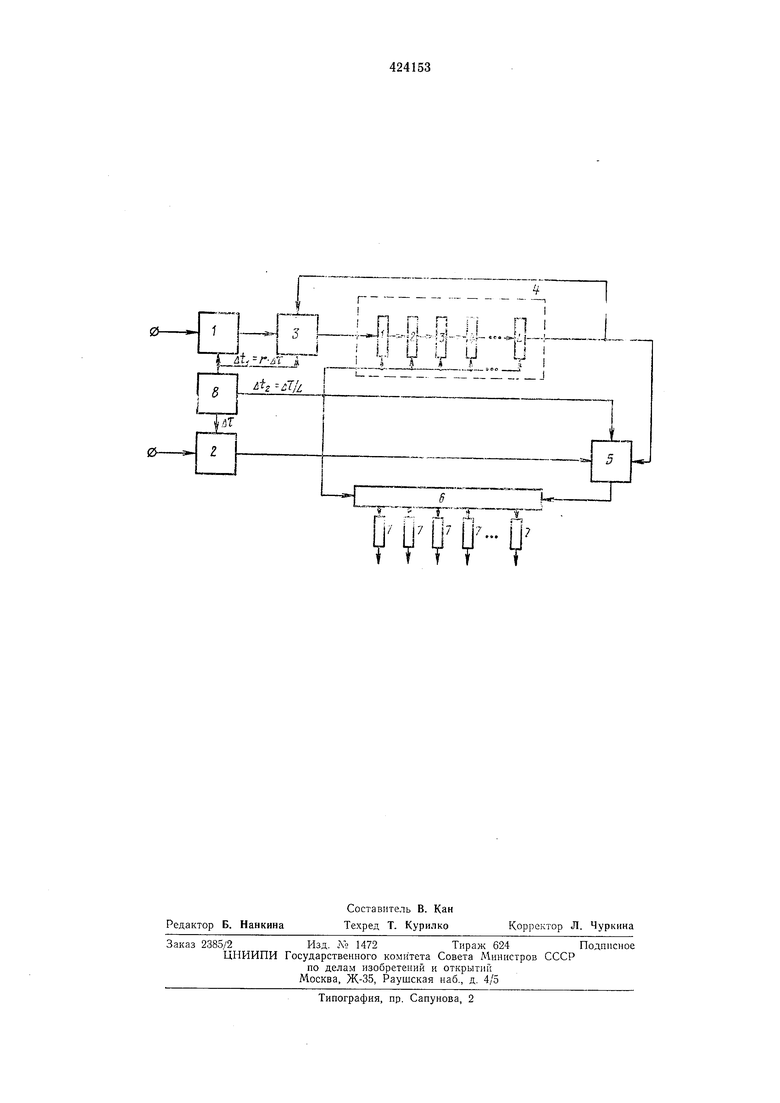

В предлагаемом устройстве выход первого аналого-цифрового преобразователя подключен к первому информационному входу первого коммутатора, второй вход которого соединен с выходом регистра сдвига и с соответствующим входом умножителя, управляющий вход первого коммутатора соединен с управляющим входом первого аналого-цифрового преобразователя, а выход соединен со входом регистра сдвига, управляющий вход которого соединен с третьим выходом синхронизатора.

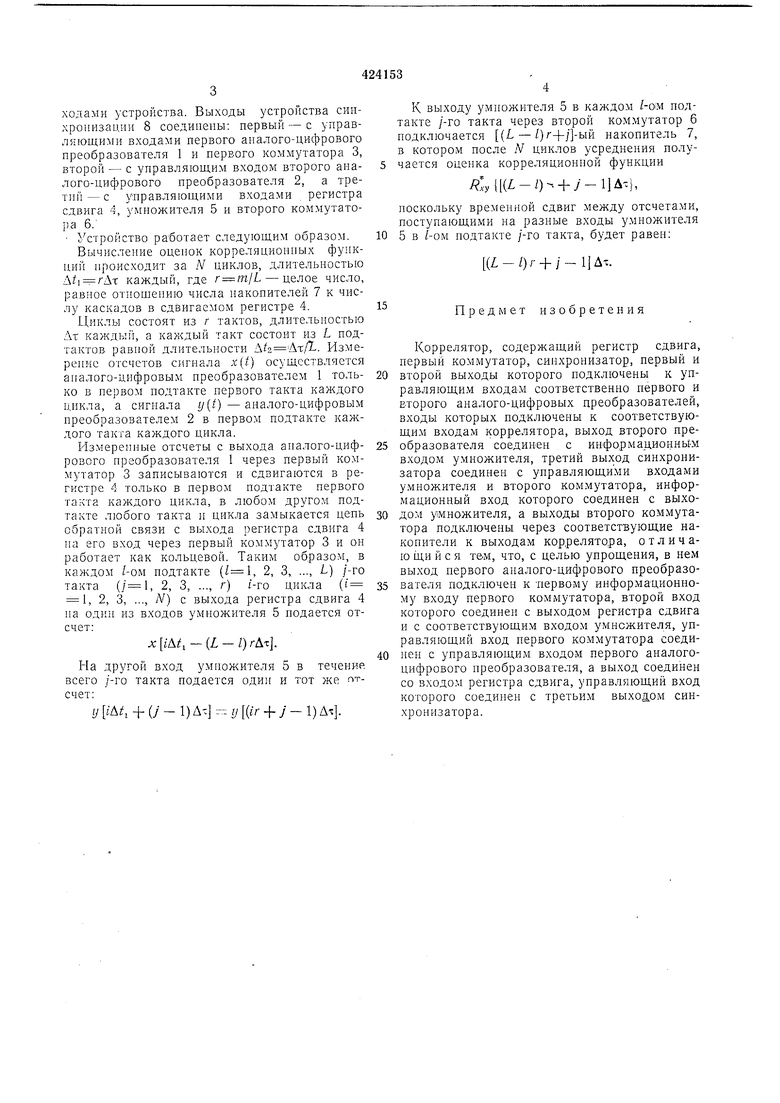

Блок-схема устройства изображена на чер1еже.

Сигналы x(t и ij(t) подаются на входы аналого-цифровых преобразователей 1 и 2. Выход первого аналого-цифрового преобразователя через первый коммутатор 3 соединен со входом регистра сдвига 4, выход которого соединен со вторым информационным входом первого коммутатора и соответствующим входом умножителя 5, другой информационный вход которого соединен с выходом второго аналого-цифрового преобразователя 2. Выход умножителя 5 через второй коммутатор 6 подключен к соответствующим входам группы накопителей 7, выходы которых являются выходами устройства. Выходы устройства синхронизации 8 соедипеиы: первый - с управляющими входами первого аналого-цифрового преобразователя 1 и первого коммутатора 3, второй - с управляющим входом второго аиалого-цпфрового преобразователя 2, а третий- с управляющими входами регистра сдвига 4, умножителя 5 и второго коммутатора 6. Устройство работает следующим образом.

Вычисление оценок корреляционных функций происходит за N циклов, длительностью Д/, гДт каждый, где - целое число, равное отнощению числа накопителей 7 к числу каскадов в сдвигаемом регистре 4.

Циклы состоят из / тактов, длительностью Дт каждый, а каждый такт состоит из L подтактов равпой длительности L tz AtfL. Измерепие отсчетов сигнала x(t) осуществляется аналого-цифровым преобразователем 1 только в первом подтакте первого такта каждого цикла, а сигнала y(t)-аналого-цифровым преобразователем 2 в первом подтакте каждого такта каждого цикла.

Измеренные отсчеты с выхода аналого-цифрового преобразователя I через первый коммутатор 3 записываются и сдвигаются в регистре 4 только в первом подтакте первого такта каждого цикла, в любом другом подтакте любого такта и цикла замыкается цепь обратной связи с выхода регистра сдвига 4 на его вход через первый коммутатор 3 и он работает как кольцевой. Таким образом, в каждом ом подтакте (, 2, 3, ..., L) /-го такта (, 2, 3, ..., г) 1-го цикла (( 1, 2, 3, ..., /V) с выхода регистра сдвига 4 на один из входов умножителя 5 подается отсчет:

л гАг- - (L -/) гАт.

На другой вход умножителя 5 в теченкк всего /-ГО такта подается одии и тот же - тсчет:

У iAA + (у - 1) Д- -- и (ir + У - 1) А.

К выходу умножителя 5 в каждом подтакте /-ГО такта через второй коммутатор 6 подключается (L -/) накопитель 7, в котором после N циклов усреднения получается оценка корреляционной функции

.ИКА-/)- +

поскольку временной сдвиг между отсчетами, поступающими на разные входы умножителя 5 в /-ОМ подтакте /-го такта, будет равен:

(Л-/)/- + /-11Ат.

Предмет изобретения

Коррелятор, содержащий регистр сдвига, первый коммутатор, синхронизатор, первый и

второй выходы которого подключены к управляющим входам соответственно первого и второго аналого-цифровых преобразователей, входы которых подключены к соответствующим входам коррелятора, выход второго преобразователя соединен с информационньш входом у.множителя, третий выход синхронизатора соединен с управляющими входами умножителя и второго коммутатора, информационный вход которого соединен с выходом умножителя, а выходы второго коммутатора подключены через соответствующие накопители к выходам коррелятора, отличаю 1ци и с я тем, что, с целью упрощения, в нем выход первого аналого-цифрового преобразователя подключен к тшрвому информационпому входу первого коммутатора, второй вход которого соединен с выходом регистра сдвига и с соответствующим входом умножителя, управляющий вход первого коммутатора соедииен с управляющим входом первого аналогоцифрового преобразователя, а выход соединен со входо.м регистра сдвига, управляющий вход которого соединен с третьим выходом синхронизатора.

i Гi

IMUJt.-. Al nrj.j. -,C-

.-J 3 I.:JuU-Ji-Jl..JLi

±,JIAJLLJ I

/. 7// i

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛИЗАТОР СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU364944A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1970 |

|

SU275542A1 |

| Цифровой коррелятор | 1976 |

|

SU610117A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛЯТОР | 1968 |

|

SU206908A1 |

| Цифровой коррелятор | 1983 |

|

SU1130875A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1986 |

|

SU1320900A1 |

| Многоканальный статистический анализатор | 1977 |

|

SU732890A1 |

| Коррелометр | 1988 |

|

SU1550532A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

Даты

1974-04-15—Публикация

1972-10-26—Подача