(54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 2016 |

|

RU2632411C1 |

| Арифметическое устройство | 1976 |

|

SU703804A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| Арифметическое устройство для цифровой фильтрации с автоматической регулировкой усиления | 1979 |

|

SU881987A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Арифметическое устройство | 1979 |

|

SU849206A2 |

| Арифметическое устройство | 1985 |

|

SU1305662A2 |

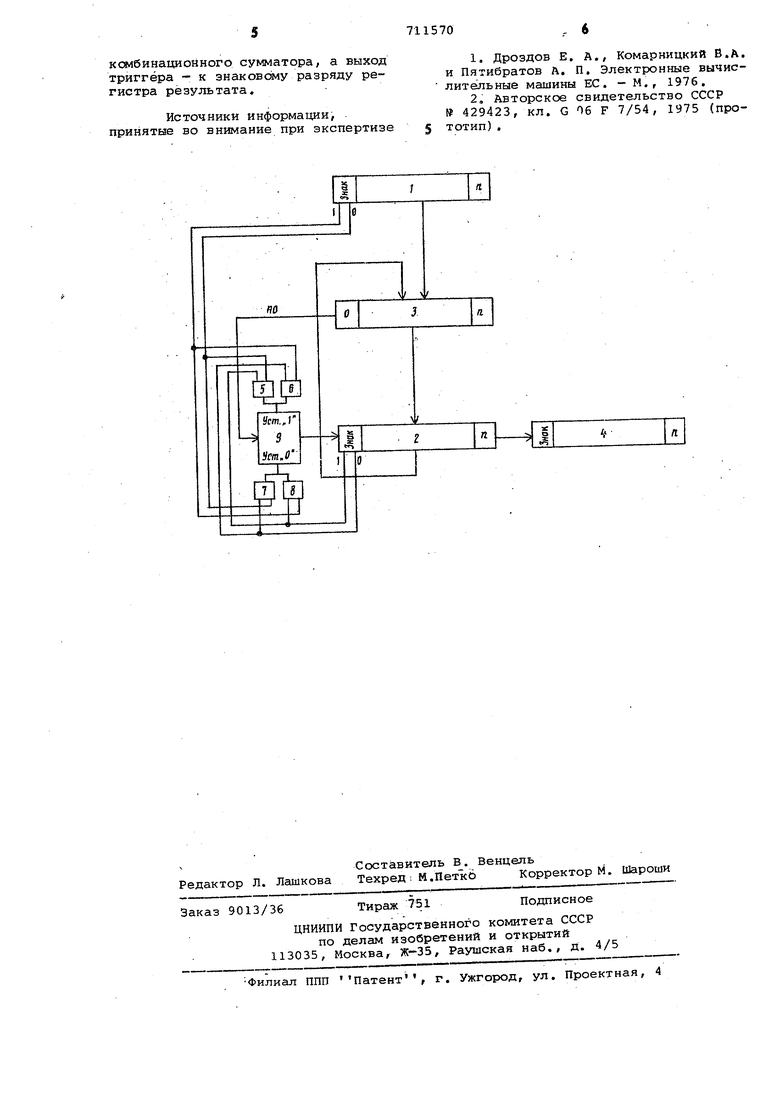

Изобретение относится к вычислительной технике и может использовать ся в специализированных цифровых вычислительных машинах, работающих в двоичной системе .счисления с числами с фиксированной запятой. Известны арифметические устройства для сложения и умножения, содержа щие регистры, комбинационный сумматор, устройство управления и устройство анализа переполнения разрядной сетки. В процессе умножения в таких устройствах для исключения потерь единиц, возникающих при переполненит ях, либо осуществляют предварительный сдвиг множимого вправо на один разряд., либо применяют специальные схемы анализа и коррекции 1 и 2. Недостатками таких устройств является неоднозначность определения переполнения при сложении и умножении и сложная структура. Наиболее близким техническим реше нием к изобретению является арифмети ческое устройство, содержащее регист слагаемого и регистр результата, одноразрядный сумматор, линию задержки схему анализа перепрлнения разрядной сетки и блок управления 2. Недостатком этого устройства является сложность проведения коррекции знака результата в случае переполнения разрядной сетки и организации а:рифметических модифицированных сдвигов в операциях умножения и деления. Цель изобретения - снижение аппаратурных затрат при организации коррекции результата. Это достигается тем, что в арифметическое устройство, содержащее первый и второй регистры, регистр результата и комбинационный сумматор, причем выход первого регистра и выход регистра результата подключены к входам комбинационного сумматора, выход которого соединен с входом регистра результата, младший разряд которого подключен к знаковому разряду второго регистра, дополнительно введены первый, второй, третий и четвертый элементы И и триггер, причем первые входы первого и четвертого, второго и третьего злементов И подключены соответственно к единичноИУ и нулевому выходам знакового разряда регистра результата, вторые входы первого и третьего, второго и четвертого элемента И соединены соответственно с нулевым и единичным выходами знакового разряда первого регистра, выходы первого и второго, третьего и четвертого элементов И подключены соответственно к установленным в. единицу и нуль входам триггера, первый вход которого подключен к нулевому выходу сигнала переноса комбинационного сумматора, а выход триггера - к знаковому разряду регистра результата. . На чертеже представлена структурная схема предлагаемого арифметического устройства. Арифметическое устройство имеет первый регистр 1, регистр реэульта;та 2, комбинационный сумматор 3, в1о рой регистр 4, элементы И 5-8 и триг гер 9. Перед началом выполнения операции сложения в регистре. хранится одно слагаемое, в регистре 2 - второе, причем разрядные шины первого и второго регистров подключены к входным шинам комбинационного сумматора 3, выходные шины которого подключены к регистру результата 2, Оба операнда представляют собой двоичные числа с фиксированной запятой, записанные в дополнительном коде. Для заплети знака чисел в регистрах 1 и 2 и в Комбинационном сумМаг торе 3 используется по одному знаковому разряду. Установка триггера 9 перед сложением производится по следующему правилу: если знаковые разряды регис гров, 1 и 2 совпадают, то триггер-устанавливается в нуль если знаковые разряды регистров 1 и 2 отличаются, то триггер устанавливается в единицу.. Если в конце сложения возникает перенос из нулевого разряда цумматора, то со{1ержимое триггера инвертируется. Результат суммирования записывает ся в регистре результата 2. В случав переполнения разрядной .сетки арифметического устройства, содержимое TpHrtepoB 9 и знакового разряда регистра результата 12 не совпадает. При выполнении операции умножения в исходном состоянии в регистре 1 хранится множимое, в,,регистре 4 Множитель. Промежуточная сумма частичнйх произведений накапливается в регистре 2 и при сдвиге вправо младшая йасть ее переходит в старшие раз рядьГ регистра 4. Триггер 3 участвует в накоплении сумм частичных произведений в модифицированном дополнительнее коде и используется для осуществления моди. фицироваиного сдвига вправо. Знак произведения вырабатывается автомати чески в ходе перемножения сомножите лей и произведение получается в коде со;ответстйуимем его знаку. Перед началом умножения обнуляется триггер 3 и регистр 2 частичных произведений. В каждом такте умножения анализируется младший разряд множителя . Если он равен единице, то множимое, расположенное в регистре 1, складывается с содержимым регистра 2, как при операции сложений, где накапливается сумма частичных произведений. Далее осуществляется операция сдвига.. .. Содержимое триггера 9 регистров ч:астичных произведений и множителя 4 сдвигается арифметически вправо на один разряд. Циклический процесс умножения повторяется до выполнения заданного количества итераций. После п-го сдвига, где п число двоичных разрядов сомножителей, знаковый разряд множителя переместится в младший его разряд, по которому осуществляется корректирующий шаг. Если младший разряд множителя равен нулю, то коррекции нет. В противг ном случае имеет место корреляция: инвертированное содержимое регистра множимого 1, увеличенное на единицу, суммируется с содержимым регистра 2 частичных произведений. После окончания умножения старшие разряды произведения располагаются в регистре 2, младглие разряды - в старших разрядах регистра 4. Формула изобретения Арифметическое устройство, содержащее первый и второй регистры, регистр результата и комбинационный сумматор, причем выход первого регистра и выход регистра результата подключены к соответствующим входам комбинационного сумматора, выход которого соединен с входом регистра результата, младший разряд.которого подключен к знаковому разряду второго регистра, отличающееся тем, что, с целью снижения аппаратурных затрат, в устройство дополнительно введены первый, второй, третий и четвертый элементы И и триггер, причём первые входы первого и четвертого, второго и третьего элементов И подключены соответственно к единичному и нулевому выходам знакового разряда регистра результата, вторые входы первого и третьего, второго и четвертого элементов И соединены соответственно с нулевым и единичным выходами знакового разряда первого регистра, выходы первого и второго, третьего и четвертого элементов И подключены соответственно к установленным в единицу и нуль входам триггера, первый вход которого подключен к нулевому выходу сигнала переноса

кс 1бинационного сумматора, а выход триггера - к энаковту разряду регистра результата.

Источники информации, принятые во внимание при экспертизе

1,Дроздов Е. А., Комарницкий В.А, и Пятибратов А. П. Электронные вычислительные машины ЕС. - М., 1976.

2,Авторское свидетельство СССР

№ 429423, кл. G Об F 7/54, 1975 (прототип) .

Авторы

Даты

1980-01-25—Публикация

1978-10-23—Подача