Известные частотно-импульсные множительНо-делительные устройства, построенные с исйользозанием реверсивного регистра, управляемого делителя частоты и логических триггерных схем, обладают недостаточным быстродействием.

Предлагаемое устройство обладает лучшими динамическими характеристиками, по сравнению с известными аналогичными схемами, благодаря использованию в устройстве логических триггерных схем, чьи коэффициенты передачи зависят от двух аргументов.

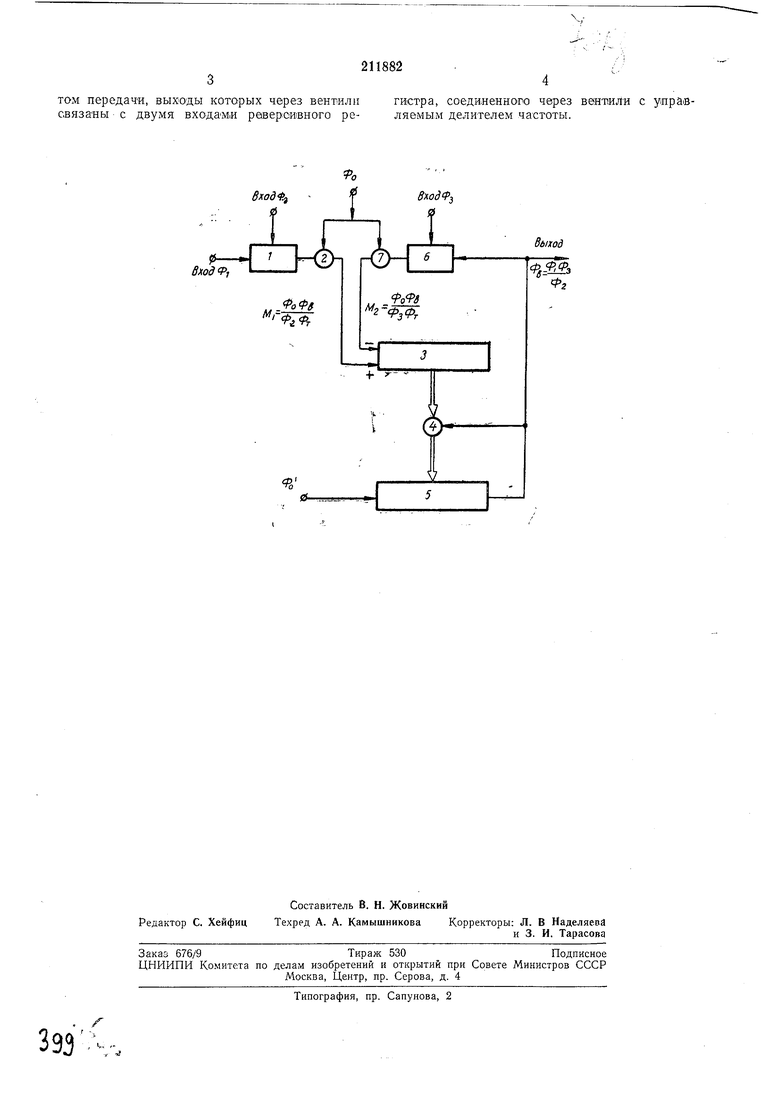

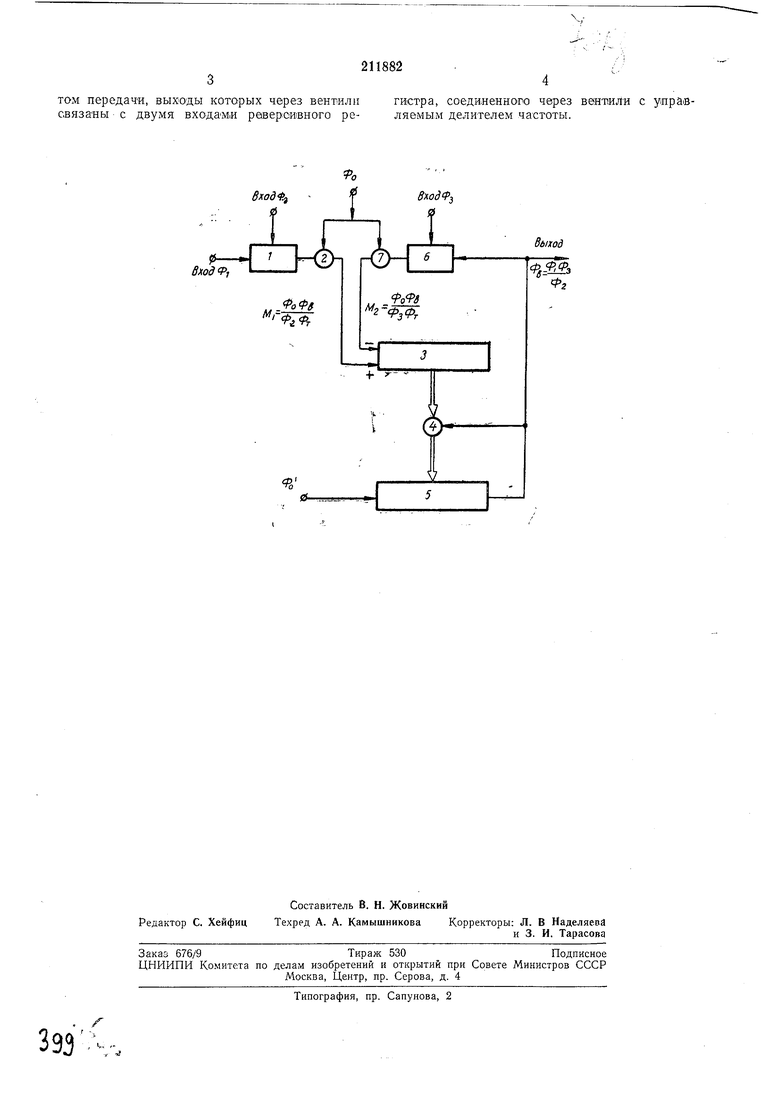

Блок-схема устройства показана на чертеже.

Поеледовательность импульсов с частотой

01подается на вход логического триггерного кольца 1, связанного через вентиль 2 с Ш|ИНОЙ сложения реверсивного регистра 3. Вентиль

2уп1ра1вляется по второму входу импульсами постоянной частоты Фо таким образом, что количество импульсов на его выходе составляет в единицу времени

Ж, ,

Ф2ФТ

где Фо, Фт - постоянные частоты;

тором импульсов постоянной частоты Фо; а выход, являющийся выходом всего устройства, подключен ко второму логическому триггерному кольцу 6, которое через вентиль 7 связано с шиной вычитания регистра 3, на которую ноступают имнульсы со средней частотой

м.|,

ФзФт

где Фв - частота выходных импульсов,

Фз -частота импульсов на третьем

входе.

В вентилях 2 и 7 предусмотрена блокировка совпадающих импульсов. Цепь обратной обеспечивает равенство , откуда следуег выражение для частоты выходных импульсов:

Ф1ФЗ

Фв Ф2

Предмет изобретения

Частотно-импульсное множительно-делительное устройство, содержащее реверсивный регистр, управляемый делитель частоты и логические триггерные схемы, отличающееся тем, что, с целью повышения быстродействия, в нем во входную цепь и в цепь обратной связи включены логические триггерные схемы с зависимым от двух аргументов коэффициен34

том передачи, выходы которых через вентили гистра, соедиденното через веннияи с улравсвязаяы с двумя входами раверсиеного ре- ляемым делителем частоты.

211882

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1968 |

|

SU217047A1 |

| Частотно-импульсное делительное устройство | 1978 |

|

SU763914A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО- ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217070A1 |

| Частотно-импульсное множительно-дЕлиТЕльНОЕ уСТРОйСТВО | 1979 |

|

SU813426A1 |

| Множительно-делительное устройство | 1977 |

|

SU788128A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО- ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1972 |

|

SU432498A1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1973 |

|

SU407317A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1995 |

|

RU2097829C1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU425182A1 |

hi

ВходР,

м- Р Рг

Snodf,

Выход

1-$&

2

.

Jf т-

Даты

1968-01-01—Публикация