1

Изобретение относится к области аналоговой вычислительной техники и может быть использовано при построении специализированных вычислителей и устройств функциональной обработки частотной информации.

Известны частотно-импульсные множительно-делительные устройства, содержащ,ие двоичный умножитель частоты, одни входы схем совпадения которого подключены к выходам делителя частоты, а другие - к выходам реверсивного счетчика. Суммирующие и вычитающие входы реверсивного счетчика через схемы совпадения соединены с выходами двух логических триггерных колец, причем оба входа первого и один вход второго логических триггерных колец подключены к входам множительно-делительного устройства, а другой вход второго логического триггерного кольца соединен с выходом двоичного умножителя. Такие устройства имеют пониженную точность при выполнении деления и не могут выполнять множительно-делительные операции, если число входных величин больще трех.

В целях устранения указанных недостатков в множительно-делительное устройство введены дополнительные вычислительные блоки. Каждый вычислительный блок имеет логическое триггерное кольцо, выход которого через схему совпадения подключен к вычитающему входу реверсИВного счетчика. Выходы реверсивного счетчика соединены с входалМи схем совпадения двоичного умножения, выход которого подключен к входу вычислительного блока. Вычислительные блоки включены последовательно, т. е. выход каждого предыдущего вычислительного блока соединен с суммирующим входом реверсивного счетчика последующего вычислительного блока, кроме выхода последнего вычислительного

блока, который соединен с входами логических триггерных колец всех вычислительных блоков.

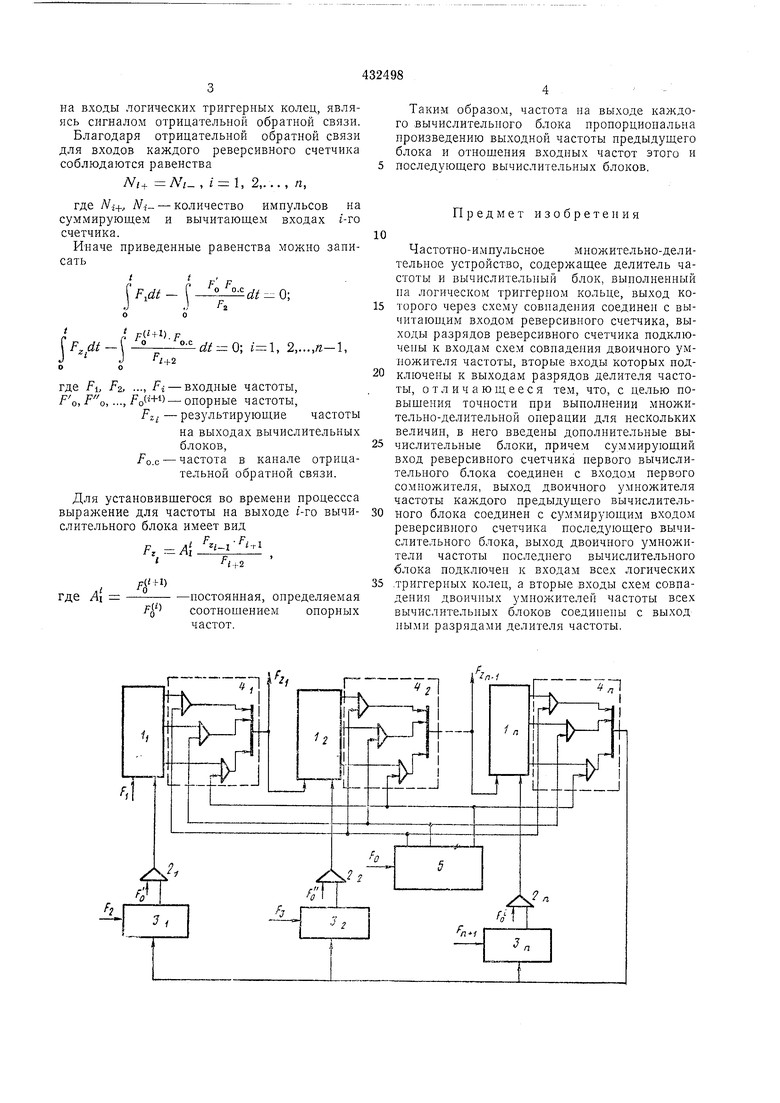

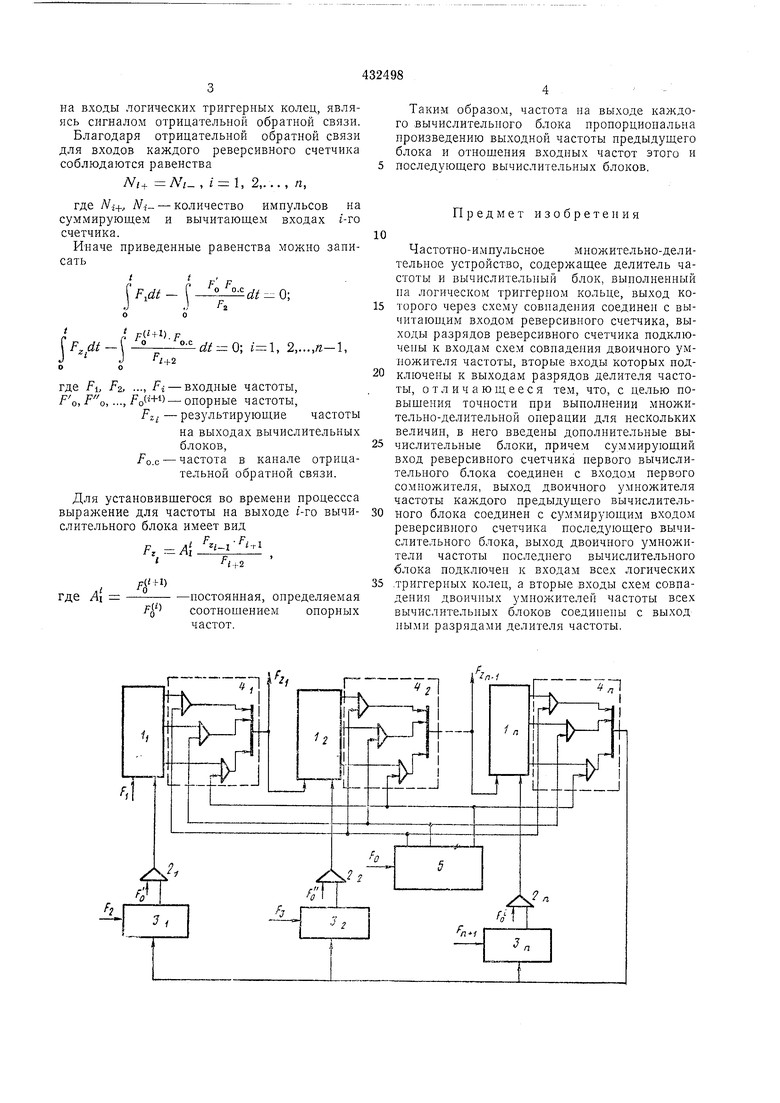

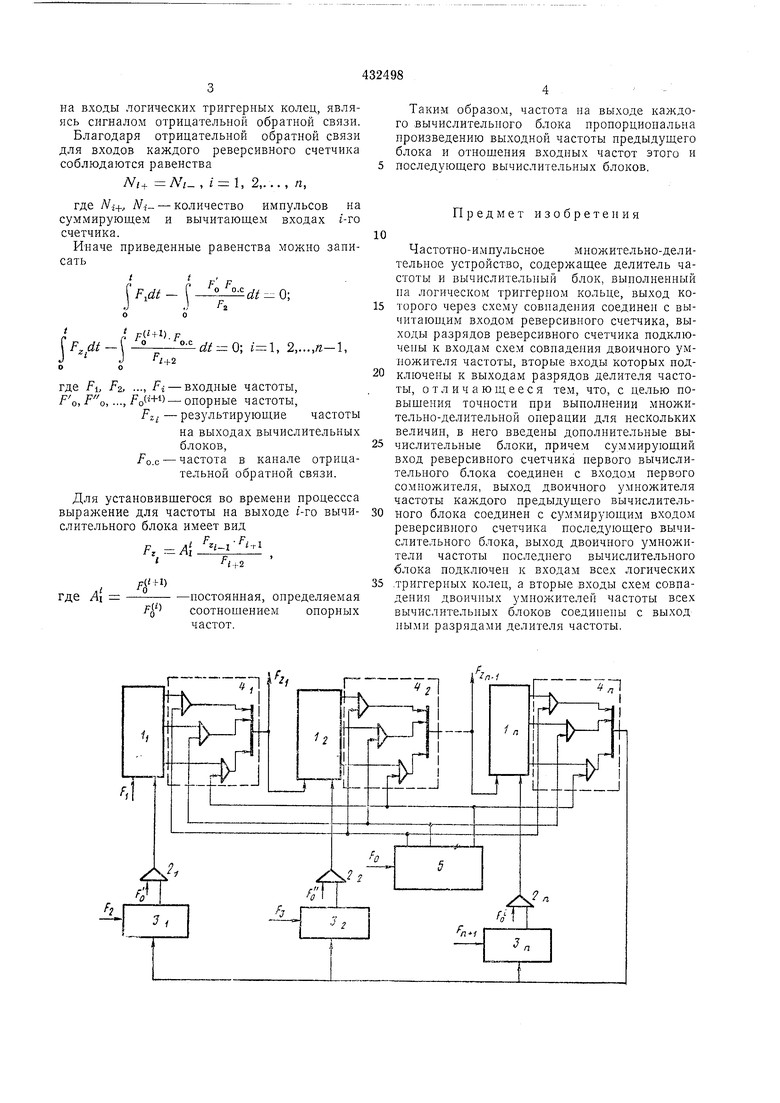

На чертеже показана блок-схема предлагаемого устройства.

Входная частота FI поступает на суммирующий вход реверсивного счетчика Ь,. На вычитаюн1ие входы реверсивных счетчиков Ь, la, . . ., In через схемы 2, 29, .... 2„ совнадепия с логических триггерных колец 3i, За, .. .,

Зп проходят соответственно входные частоты FZ, FB, . . ., Fn+i.

Выходы реверсивных счетчиков управляют работой двоичных умножителей 4i, 42. . . ., 4,г, на импульсные входы схем совпадения которых поступает частота с делителя 5 частоты. Частота с выхода схемы «ИЛИ умножителя 4i подается на суммирующий вход счетчика Ь, с выхода умнолсителя 42 поступает на суммирующий вход счетчика Ь и т. д., причем

частота с вы.хода умножителя 4„ поступает

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1977 |

|

SU788128A1 |

| Частотно-импульсное множительно-дЕлиТЕльНОЕ уСТРОйСТВО | 1979 |

|

SU813426A1 |

| Частотно-импульсное делительное устройство | 1978 |

|

SU763914A1 |

| ВРЕМЯ-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU363990A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1968 |

|

SU217047A1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU399865A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1995 |

|

RU2097829C1 |

| Устройство для перемножения двух частотно-импульсных сигналов | 1979 |

|

SU920723A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2008 |

|

RU2389065C1 |

| Множительно-делительное устройство | 1987 |

|

SU1451732A2 |

Даты

1974-06-15—Публикация

1972-06-26—Подача