Известные вспомогательные блоки к цифровым вычислительным машинам позволяют несколько сократить основное машинное время при решении ряда статистических задач.

Предлагаемое устройство позволяет получить существенно больший выигрыш по времени счета, так как представляет собой специализированную цифровую машину, включаюш,ую генератор случайных двоичных чисел, устройство управления, устройство проверки логических условий, блок памяти, буферное и арифметическое устройства.

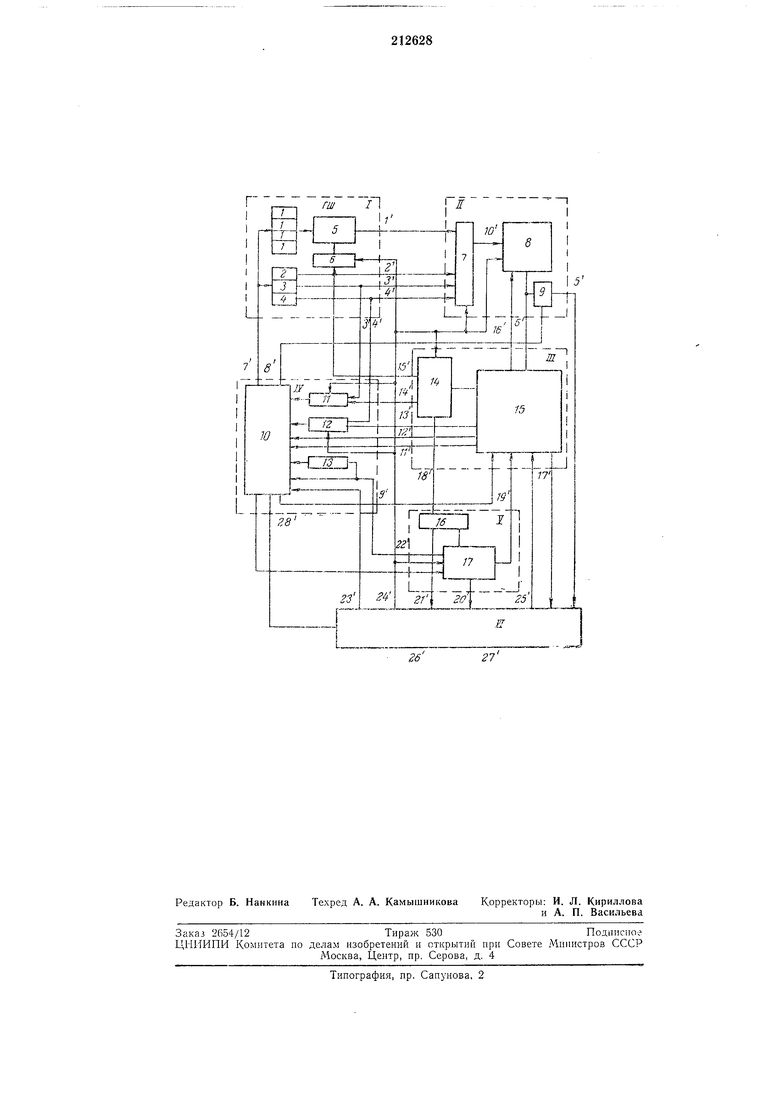

Па чертеже показана блок-схема предлагаемой приставки, где приняты следуюш,ие обозначения:

/ - генераторы случайно распределенных импульсов;

2, 3, 4 - сменные генераторы случайных импульсов с фиксированными законами распределения;

5- логический преобразователь;

6- регистр;

7- коммутатор;

8- многоразрядный сумматор;

9- вентильная схема;

10- блок разрешения; 11, 12, 13 - счетчики;

16- набор вентилей;

17- сумматор арифметического устройства; позициями г, 226, 27, 28 обозначены

взаимосвязи между блоками. Б л о к I.

Управляемый генератор случайных величин ГШ для получения на каждом такте работы приставки случайного кода с распределением вероятностей, зависящим от управляющего входа ГШ. Блоки 1 являются стандартными генераторами случайных стандартизованных импульсов, выдающих в каждый момент «нуль или «единицу с вероятностью 1/2. Блоки 2, 3 vi 4 являются сменными генераторами случайных импульсов с фиксированными законами распределения. От блока 4 может потребоваться имитация нуассоновского процесса, в частности, при моделировании систем массового обслуживания. Блоки 2, 3, 4 идентичны блокам ). Блок 5 является логическим преобразователем с четырьмя случайными входами, двадцатью четырьмя управляющими входами и шестью случайными выходами. Значения управляющих входов определяются

регистром 6.

Управляющий вход блока 5 (или регистр 6} разбивается на группы следующим образом: Регистр 6 имеет также управляющий вход 24 со значениями «О или «1. В зависимости от программы настройки содержимое регистра либо не изменяется в процессе моделирования после заполнения в момент пастройки, когда вход 15 блокирован, лнбо вход 15 не блокирован, и тогда вход 7 определяет пуск и останов генератора случайных величин. Блок II. Условный преобразователь служит для нреобразования случайного кода в значение случайной величины с локальным распределением вероятностей. Он представляет собой коммутатор 7, двенадцатиразрядный сумматор 3 с устройством переноса, обеспечивающим гашение единицы переноса из любых трех разрядов сумматора, определяемых программой настройки, и вентильную схему 9. Вход / доставляет в блок II комбинацию вида 000100, которая истолковывается коммутатором 7 следующим образом: единица на четном месте - прибавить, единица на нечетном месте - вычесть (прибавить в обратном коде) в один разряд сумматора единицу, если она встречается в первой паре входного кода, соответственно в другой разряд для второй пары и в третий разряд для третьей пары (например, комбинация 000100 истолковывается как прибавить «1 во второй разряд). Входы 2, 3 и 4 доставляют в блок II на каждом такте «О или «1, которые в зависимости от значений констант программы настройки либо блокированы, либо прибавляются коммутатором 7 в упомянутые разряды сумматора, либо операция определяется тем, прибавлялась или вычиталась в соответствующий разряд единица, поступивщая по управляемому входу Г (при этом сработаег только один из входов - соответствующий работавшему в этом такте управляемому входу). Вход 10 служит для занесения в сумматор начального значения, хранящегося в определенной ячейке блока памяти, например «01. Вход 24 служит для настройки условного преобразователя в начале работы. Вход 8 является управляющим - по нему производится считывание значения сумматора по выходу 5 при некоторых остановах приставки. Выход 6 является основным - по этому выходу содержимое сумматора поступает в блок памяти III и по нему, как по адресу, происходит выбор информации из некоторой ячейки. Выход 5 служит для передачи в буферное устройство БУ (блок VI) содержимого сумматора 8 по сигналу устройства управления (вход 8). Блок III. Это блок памяти, который служит для кодирования начального состояния системы и управляющей и вычислительной частей схемы моделирования. Блок 14 является коммутатором, обеспечивающим сопряжение ключевого входа блока I с группой разрядов ячейки памяти, отведенной для кодирования распределения вероятностей. Блок 15 представляет собой собственно стандартньш куб памяти в 4096 ячеек по 45 двоичных разрядов. По программе настройки часть объема запоминающего устройства в 1, 64, 256 и 1024 ячеек отводится под буферную память и служит для записи информации, поступающей из буферного и арифметического устройств. Я1 П.2 Пз П Пг, Яо - означают код распределения вероятностей, которое будет имитироваться генератором блока I на следующем шаге испытаний. В зависимости от условий задачи этот код может занимать максимально 24 разряда (6X4). Нулевой код, например, воспринимается приставкой как сигнал о том, что блок I постоянно работает с одним и тем же распределением, определенным содержанием ячейки памяти, например «00, По входу 6 поступает адрес ячейки, из которой произойдет считывание информации, если поступит разрешающий сигнал на считывание из блока IV по входу 9. Вход 25 служит для записи информации в память из буферного устройства (блока VI). Вход 19 служит для записи информации в память из арифметического устройства (блока V). Выход 16 служит для записи в сумматор 8 начального значения, хранящегося в ячейке «01 блока памяти. Выход 17 служит для считывания в буферное устройство и в ЭВМ содержимого ряда ячеек памяти. Группа входов //, 12, 14, 15 передает по назначениям содержимое той ячейки, по которой произошло считывание, если оно состоялось. Блок IV. Устройство управления служит для организации работы приставки в основных режимах. Блок 10 - разрешающий блок, распределяющий сигналы разрешения на срабатывание блоков приставки в зависимости от своих входных сигналов. Блоки 11, 12, 13 - счетчики, определяющие цикличность работы приставки. Счетчик 11 при единичном сигнале в одном из разрядов программы настройки заполняется по входу 14 при считывании из памяти в рабочем режиме, а при нулевом сигнале заполняется по входу 3 случайным кодом. Счетчик 12 при наличии единицы во втором разряде кода программы настройки заполняется по входу 13 каждый раз после срабатывания арифметического устройства к импульсами, число которых задано содержимым ячейки «10 блока памяти, а при наличии сигнала заполняется раз после своего срабатывания на сравнение случайным кодом по входу 4. Счетчик 13 обеспечивает одно срабатывание на заданное число срабатываний арифметического устройства. Это число постоянно и принято равным 4096 (двенадцатиразрядный счетчик). При наличии «1 в третьем разряде кода программы настройки счетчик 13 нересчитывает все срабатывания арифметического устройства (блок V), при наличии «О - только отдельные срабатывания. По входу 22 в блок IV подается сигнал о срабатывании арифметического устройства, а вход

ставки либо в начале работы, либо после останова приставки с передачей управления буферному устройству. Выход Т выдает пусковые сигналы блока / постоянно, если был сигнал пуска приставки и не поступил сигнал останова по какой-либо причине. Причинами останова может быть работа блоков III, V и VI. Выход 8 выдает сигнал на передачу содержимого сумматора блока II в. блок VI, который появляется после каждого останова блока I. По выходу 9 поступают разрешающие сигналы срабатывание блока (разрешение на считывание). Такой сигнал появляется при срабатывании счетчика // на сравнение, то есть когда число срабатываний ГШ равно значению счетчика 11. Выход 10 выдает разрешение на срабатывание блока V. Такой сигнал появляется при срабатывании счетчика 12.

Блок V.

Арифметическое устройство (ЛУ) служит для суммирования содержимого ячеек памяти, передачи в буферное устройство содержимого сумматора и для групповой обработки содержимого группы ячеек памяти - в зависимости от кода операции, определяемого программой настройки. Блок 16 представляет собой вентильное устройство, блок П-сумматор арифметического устройства. По входу 18 в блок V поступает функциональная часть содержимого выбранной ячейки памяти. По входу 10 поступает разрешение из блока IV на выполнение операции. По входу 22 в блок V поступает программа настройки, - именно код операции и код настройки коммутатора 14. Выход 19 выдает результат операции в основную часть памяти - в ту же ячейку, содержимое которой обрабатывалось. Выход 20 передает результат в буферное устройство - для записи в буферную часть памяти. Выход 21 передает функциональную часть содержимого ячейки непосредственно в буферное устройство без обработки в Л У. Выход 22 выдает сигнал о завершении выполнения операции в ЛУ. Значения кода операций могут быть следующими;

А - блок I обработки не производит - функциональная часть содержимого каждой выбранной ячейки по разрешению «1 передается в буферное устройство;

Б - функциональная часть содержимого каждой выбранной ячейки памяти по разрешению «1 прибавляется к содержимому следующей по порядку ячейки буферной памяти (начиная с первой ячейки). Этот процесс идет до заполнения буферной памяти, когда появляется разрешение «2, и процесс начинается рновь с первой ячейки буферной памяти. Еслн появилось разрешение «3 (оно может появиться только ранее разрешения «2), то во все остальные, еще не участвовавшие в процессе суммирования ячейки буферной памяти, прибавляется содержимое последней выбранной ячейки, процесс вновь возвращается к началу, как после разрешения

ной ячейки памяти суммируется в сумматоре ЛУ блока V. По разрешению «4 содержимое сумматора выдается в буферное устройство; Г - по каждому разрешению «2 или 3

функциона.ьная часть содержимого выбранной ячейки памяти складывается с единицей и результат записывается снова в ту же ячейку. Прекращение работы блока V с передачей Зправления буферному устройству происходит

в режиме Л по разрешению «2 или «3, в режимах Б, В и Г по разрешению «4. Блок VI.

Буферное устройство служит для связи приставки с ЭВЛ1 управления в режимах записи

и считывания информации, настройки блоков приставки на основе программы настройки, поступающей из ЭВМ, управления началом и продолжением работы приставки. По входам 21 и 22 поступает результат обработки из

блока V, по входу 17 производится считывание содержимого части памяти, по входу 5 поступает значение сумматора блока II, по входу 27 поступает информация из ЭВМ, по входу 28 поступает управляющая информация

из блока IV. Выход 23 служит для пуска приставки, выход 24 разносит по соответствующим блокам программу настройки приставки, выход 25 обеспечивает запись информации в намять приставки, выход 26 для передачи в ЭВМ управляющей и числовой информации. Буферное устройство работает в четырех режимах:

1) запись информации из ЭВМ в память приставки;

2) ввод программы настройки;

3)запись текущей информации о решении в буферную часть памяти;

4)считывание информации в ЭВМ из памяти приставки.

В режимах Л, Б и В арифметического устройства информация, поступающая в буферное устройство, немедленно переписывается в буферную часть памяти. В режиме Г буферное устройство не участвует. В режиме Л по разрешению «2 или «3 буферное устройство передает в ЭВМ команду обращения.

В зависимости от блока V и программы настройки производится обработка получаемой траектории случайного процесса. В

буферной части памяти накапливается либо сама траектория или система значений функции на ней (режим Л), либо средняя некоторой функции цепи одновременно для всех точек моделируемого интервала процесса ( Б}, либо средняя некоторой случайной величины, определенной цепью (режим В. В режиме Г вычисляется абсолютное распределение вероятностей состояний моделируемой цепи на некотором шаге, которое накапливается непосредственно в ячейках, кодирующих состояния цепи.

В режиме В решаются, например, следующие задачи; вычисление определенных интехле для уравнения в частных производных 2-го порядка эллиптического типа общего вида; краевая задача для уравнения теплопроводпости; моделирование прохождения частицы через слой вещества; моделирование систем массового обслуживания; решение систем нелинейных уравнений больших порядков. В режиме А мояшо получать решения систем линейных алгебраических уравнений высоких порядков и значения континуальных интегралов; обрабатывая в ЭВМ траектории функций цепей Маркова, выдаваемые приставкой, моделировать процессы распределения ресурсов в ходе производства и строительства; моделировать течение цепной реакции. В режиме Б весьма эффективно решается краевая задача для уравнения теплопроводности, а в режиме Г возможно прогнозирование эволюции производственно-экономических систем с точки зрения распределения материальных ресурсов на определенном этапе времени.

Предмет изобретения

Приставка к цифровым вычислительным машинам для решения статистических задач, содержащая генераторы случайных двоичных чисел с равномерным распределением, регистры, блок памяти, дешифраторы, вентили, буферное устройство, устройство управления и условный преобразователь, отличающаяся тем, что, с целью повышения быстродействия при

моделировании произвольных однородных цепей Маркова высоких порядков в режиме многопрограммной работы, часть генераторов случайных чисел в зависимости от программы

непосредственно, а другая часть через управляемый кодовый преобразователь и через управляемый коммутатор соединена с управляемым составным сумматором, выход которого через вентиль подключен ко входу буферного

устройства, связанного выходами через управляемый коммутатор с кодовым преобразователем генератора случайных чисел, с арифметическим устройством, со счетчиками сравнения устройства управления и с буферным устройством, причем выходы арифметического устройства соединены с блоком памяти, буферным устройством, с дешифратором устройства управления, а выходы буферного устройства подключены к дешифратору устройства

управления, к регистру генератора случайных чисел, к коммутатору и составному сумматору условного преобразователя, к коммутатору блока памяти и арифметическому устройству, к автономной системе управления блока намяти и непосредственно к внешнему входу цифровой вычислительной машины, выходы регистров сравнения связаны с дешифратором устройства управления, выходы которого соединены с генератором случайных двоичных чисел, с вентилями условного преобразователя, с системой управления блока памяти и с сумматором арифметического устройства.

г i:

27

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для предварительной обработки информации | 1991 |

|

SU1837274A1 |

| Устройство для ввода информации | 1991 |

|

SU1800452A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Устройство для синтеза речи | 1982 |

|

SU1095167A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

Авторы

Даты

1968-01-01—Публикация