Известны устройства для моделирования сетевых графиков, содержащие модели работ и модели событий, соединенные согласно сетевому графику, тактовый генератор, коммутатор, устройство управления и арифметическое устройство.

Предлагаемое устройство собрано по упрощенной схеме. Отличается оно тем, что модели событий содержат схемы «PI, «ПЛР и сдвигающий регистр, разрядность которого равна числу входящих в событие работ. Тактовый вход регистра соединен с выходом первой схемы «ИЛИ, входы которой соединены с выходами моделей входящих в событие работ, а также со входами схем «PI. Выход регистра соединен со вторыми входами схем «И. Третий, потенциальный, вход последних подсоединен к одному из выходов устройства управления. Выходы схем «Pi соединены со входами устройства управления, а также второй схемы «ИЛИ, один из входов которой соединен с выходом коммутатора. Выход схемы «ИЛР1 соединен с выходами моделей исходящих из события работ.

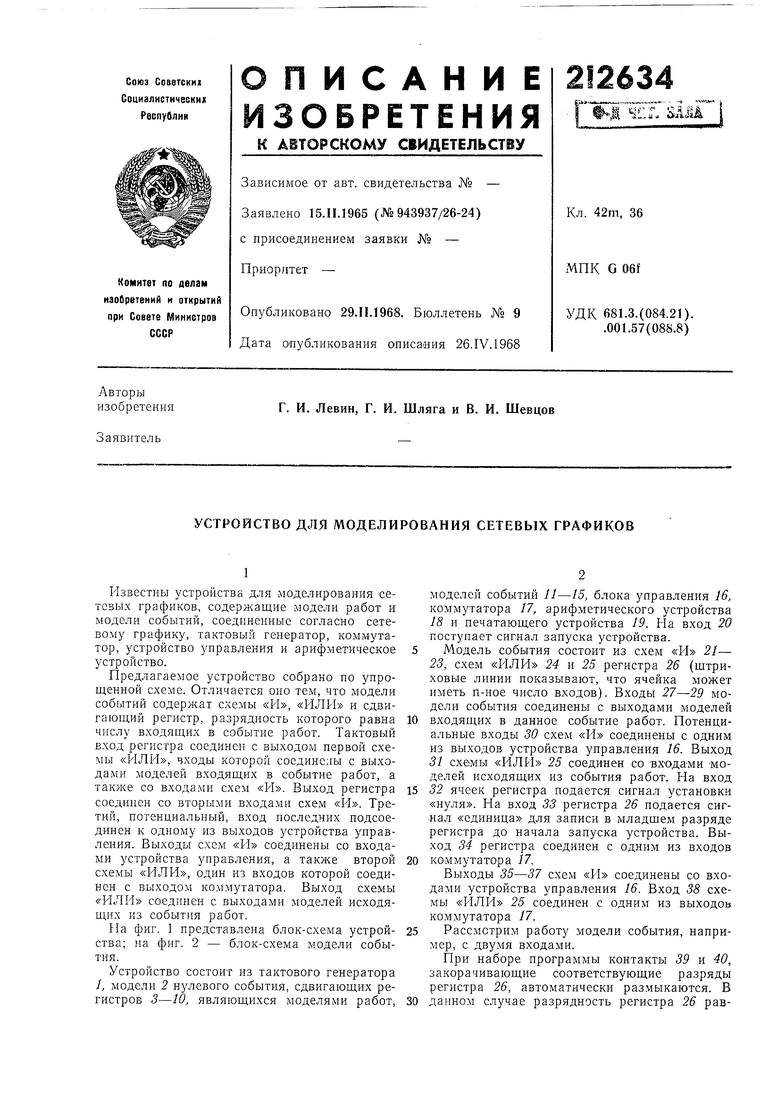

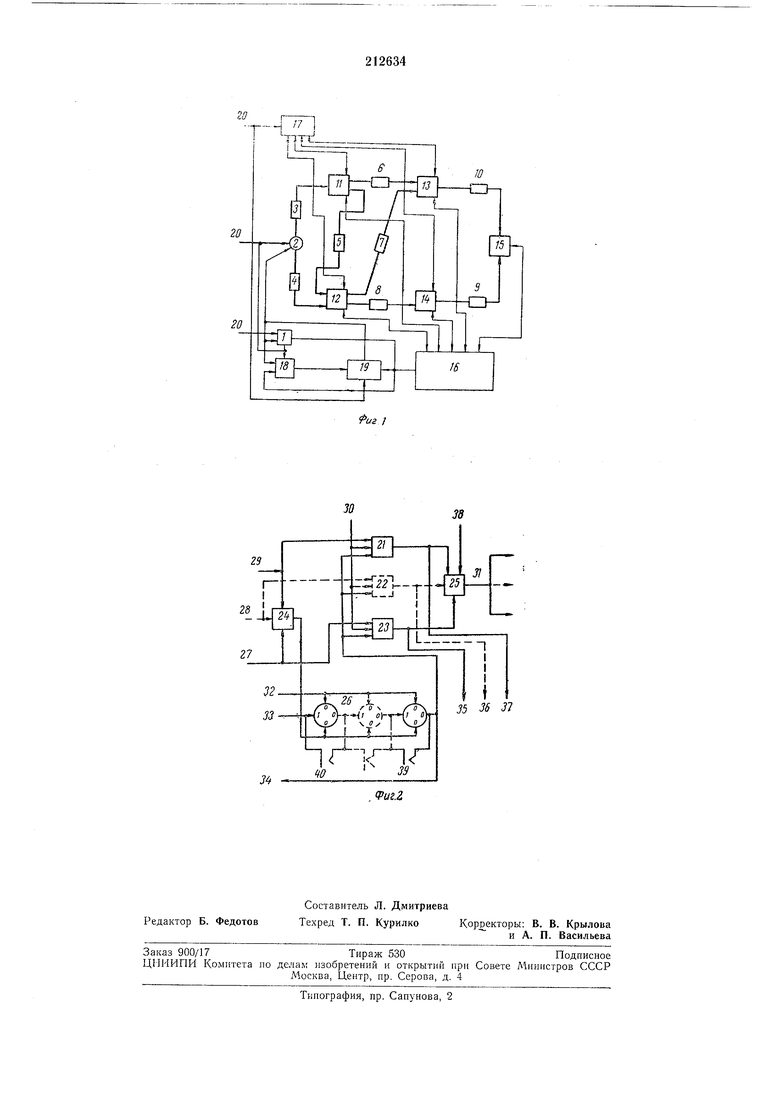

Иа фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схема модели события.

моделей событий 11-15, блока управления 16, коммутатора 17, арифметического устройства 18 и печатающего устройства 19. Па вход 20 поступает сигнал запуска устройства.

Модель события состоит из схем «И 21- 23, схем «ИЛИ 24 и 25 регистра 26 (щтриховые линии показывают, что ячейка может иметь п-ное число входов). Входы 27-29 модели события соединены с выходами моделей

входящих в данное событие работ. Потенциальные входы 30 схем «И соединены с одним из выходов устройства управления 16. Выход 31 схемы «ИЛИ 25 соединен со входами моделей исходящих из события работ. На вход

32 ячеек регистра подается сигнал установки «нуля. На вход 33 регистра 26 подается сиг.нал «единица для записи в младшем разряде регистра до начала запуска устройства. Выход 34 регистра соединен с одним из входов

коммутатора 17.

Выходы 35-37 схем «И соединены со входами устройства управления 16. Вход 38 схемы «Р1ЛИ 25 соединен с одним из выходоь коммутатора 17.

Рассмотрим работу модели события, например, с двумя входами. на двум. На потенциальные входы 30 схем 21-23 подана «единица, на остальных входах сигнал отсутствует. Импульсом, поданным на вход 33, в младший разряд регистра 26 записывается «единица (младшим при любом количестве входов является первый незакороченный разряд). При поступлении одного импульса на один из входов, например на вход 27, «единица, записанная в регистре 26, продвигается на един разряд. С приходом последнего импульса, в данном случае второго, на вход 29 схемы «Р1ЛИ 24 перемагничизается последний ферритовый тор регистра 26, импульс с которого поступает на все входы схем «И 21-23. Длительность импульса на входе 29 и импульса с последнего разряда регистра 26 выбрана такой, что они действуют на входы схемы «П 21 в течение времени, необходимого для срабатывания этой схемы. Таким образом импульс, поступающий на входы 31 последующих регистров сдвига, подключенных через схему «ИЛИ 25 к данной модели события, одновременно подается с выхода 37 в блок управления 16 и указывает вход, на который поступил последний импульс с соответствующего регистра, в данном случае вход 29. Так как модель события выдает имиульс только после поступления последнего импульса с указанием входа, на который поступил этот импульс, это значит, что данная модель пропускает импульс, прищедщий с пути наибольщей продолжительности. Такое построение модели события позволяет найти критический путь при предварительной записи «единиц в младщие разряды регистра 3 W. 4, выходящих из нулевого события 2, в младщие разряды регистров 26 модели события и арифметическое устройство, и последующем запуске всего устройства. Тактовый генератор 1 обеспечивает последовательное продвижение записанных «единиц по регистрам и счет числа импульсов, соответствующих длительности критического пути в арифметическом устройстве, до момента прихода последнего импульса с выхода модели 15 конечного события. Одновременно блок управления 16 выдает сигнал, снимающий запрет с той модели события, с которой поступил последний импульс (например, с модели /), в конечную ячейку 15. Во время работы устройства с блока управления 16 подаются сигналы, запрещающие прохождение импульсов со всех моделей сооытий, кроме контролируемой, на блок управлеВ первом цикле работы устройства контролируется модель конечного события. Конец печати является началом следующего цикла работы. В этом цикле контролируется модель события, с которой снят запрещающий сигнал (в данном случае модель 13). Во второл цикле определяется модель собыия, с которой поступил последний импульс на модель 13, н т. д. Печатающее устройство 19 выдает длину ритического пути, затем длину пути от нз леого события до каждого из событий, лежаих на критическом пути, и их номера. При нахождении резервов времени с потенциального выхода 30 контролируемой модели события снимается «единица и тем самым запрещается проход последнего импульса с выхода 31 этой модели в последующие регистры. Однако, пройдя через регистр 26, импульс с выхода 34 подается в коммутатор, который через выдержку времени подает «единицу на вход 38 схемы «ИЛИ 25 для выдачи ее в последующие регистры. Рассмотрим работу устройства в режиме нахождения резервов времени. Резервы времени г находят по формуле fe Ткр - Те - Те , где: ; кр - длина критического пути; Ге -ранний срок сверщения события; Тс -поздний срок сверщения события. Длина ранее найденного критического пути хранится в арифметическом устройстве 18. Резервы времени находятся автоматически для всех событий в заданном порядке с помощью коммутатора 17. Для нахождения наименьшего возможного срока сверщения данного события коммутатор J7 снимает с потенциального входа 30 схем «PI (см. фиг. 2) «единицу, тем самым запрещая выход импульса с этой модели сооытия в последующие регистры. Перед запуском устройства «единица заносится во все младщие разряды всех регистров и вычитается из арифметического устройства 18. Затем включается тактовый генератор 1, и «единица продвигается тактовыми импульсами по разрядам регистров. Одновременно с каждым тактом вычитается «единица из арифметического устройства 18. При поступлении последнего импульса на контролируемое (по резерву) событие прекращается поступление вычитающих импульсов .на арифметическое устройство 18. Эта пауза выдерживается в течение времени, пока последний импульс, не проходящий через данную модель события, достигнет модели конечного события. Далее находят наиболее позднее время сверщения данного события. Для этого после заданной выдержки с коммутатора 17 на входы регистров, подключенных к выходу контролируемого события, подается «единица. Эта «единица продвигается тактовыми импульсами к конечной модели событий 15. Последним к конечному событию поступает импульс, прощедщий через критический путь между данным и конечным событиями. Кощий вычитание единиц из арифметического устройства 18, причем в данном случае число вычтенных единиц равно наиболее иозднему возможному времени свершения данного события. Результат, полученный в арифметическом устройстве, выдается на печать вместе с номером события.

Данное устройство позволяет также отыскивать так называемые «циклы, т. с. логические ошибки при составлении графика.

При наличии такой ошибки обсчет графика прекращается на некотором такте. В силу описанной выше работы модели события импульсы поступают не на все входы модели конечного события. Для обнаружения событий, входящих в «цикл, включается коммутатор 17, последовательно подающий импульсы на выходы всех моделей событий.

При нодаче импульса на выход любой из моделей событий, входящих в «цикл, работа продолжается. С конечного события поступает выходной и: шульс, который останавливает коммутатор 17 на данном событии (импульсы подаются с некоторым интервалом, достаточным для их прохождения их от начального до конечного событий). Проверив таким

образом оставшиеся события, выявляют все события, образующие «цикл.

Предмет изобретения

Устройство для моделирования сетевых графиков, содержащее модели работ и модели событий, соединенные согласно сетевому графику, тактовый генератор, коммутатор, устройство управления и арифметическое устройство, отличающееся тем, что, с целью упрощения схемы устройства, модели событий содержат схемы «PI, «ИЛИ и сдвигающий регистр, разрядность которого равна числу работ, входящих в событие, причем тактовый

вход регистра соединен с выходом первой схемы «Р1ЛИ, входы которой соединены с выходами моделей входящих в событие работ, а также со входами схем «И, выход регистра соединен со вторыми входами схем «И, третий, потенциальный, вход которых подсоединен к одному из выходов устройства управления, выходы схем «И соединены со входами устройства управления, а также со входами второй схемы «ИЛИ, один из входов

которой соединен с выходом коммутатора, выход схемы «ИЛИ соединен с выходами моделей исходящих из события работ.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СЕТЕВЫХ ГРАФИКОВ | 1972 |

|

SU358707A1 |

| УСТРОЙСТВО для МОДЕЛИРОВАНИЯ СЕТЕВОГО ГРАФИКА | 1969 |

|

SU254895A1 |

| Устройство для определения характеристик сетей | 1984 |

|

SU1282151A1 |

| УСТРОЙСТВО для МОДЕЛИРОВАНИЯ СЕТЕВОГО ГРАФИКА | 1971 |

|

SU311277A1 |

| Устройство для формирования синхроимпульсов | 1979 |

|

SU777652A1 |

| Устройство для определения характеристик сетей | 1984 |

|

SU1242980A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Устройство для регулирования передачи данных | 1975 |

|

SU595872A1 |

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ НАДЕЖНОСТИ ФУНКЦИОНИРОВАНИЯ СИСТЕМ | 1969 |

|

SU255657A1 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

23

Даты

1968-01-01—Публикация