В известных функциональных преобразователях с комбинированной формой представления переменных выходная величина представляется в аналоговой форме, что связано с ограничением точности.

Для повышения точности при работе в комбинированных вычислительных системах с представлением переменных раздельно аналоговой и цифровой частями предлагаемый преобразователь содержит цифровой и аналоговый интерполяторы и блок оценки. Входы цифрового интерполятора подключены к старшим разрядам значений функции в узлах интерполирования, хранящихся в регистрах запоминающего устройства, входы аналогового интерполятора соединены с младшими разрядами значений функции в узлах, а блок оценки подключен к входным и выходным регистрам.

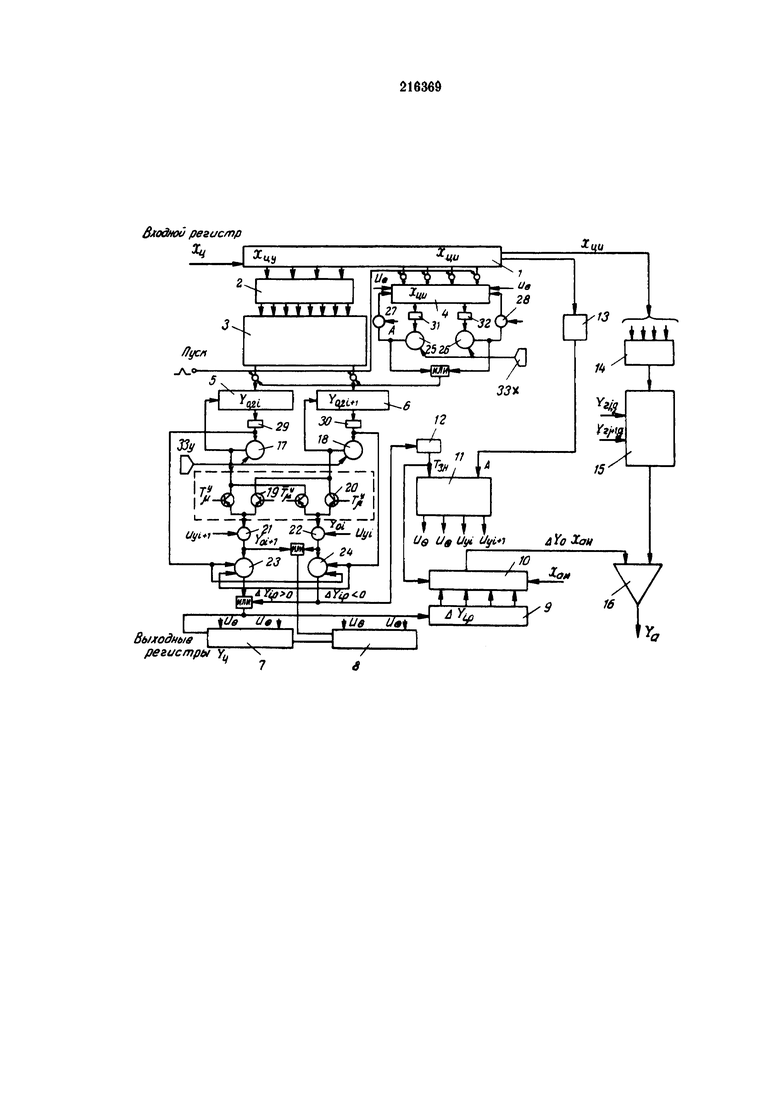

На приведенной схеме устройства приняты следующие обозначения:

1 - входной регистр; 2 - дешифратор адреса числа; 3 - запоминающее устройство; 4 - регистр Xци цифрового интерполятора; 5, 6 - регистры Y0,2i, Y0,2i+1; 7, 8 - выходные регистры Yц; 9 - регистр ΔYi,0; 10 - цифро-аналоговый преобразователь; 11 - блок оценки; 12 - триггер знака; 13 - пороговая схема; 14 - цифро-аналоговый преобразователь; 15 - аналоговый интерполятор; 16 - выходной усилитель-сумматор Ya; 17-28 - вентили; 29-32 - диодные схемы; 33х и 33y - генераторы импульсов.

Функциональный преобразователь состоит из входного регистра 1 для запоминания Xц, который связан через дешифратор 2 адреса числа с запоминающим устройством 3, цифрового интерполятора, аналогового интерполятора 15 и выходных регистров 7, 8.

Цифровой интерполятор состоит из генераторов импульсов 33x и 33y, регистров 5 и 6 (для хранения величин Y0,2i и Y0,2i+1), которые через диодные схемы 29 и 30 и систему вентилей 17-24 соединены с выходными регистрами, а также регистра 4 (для запоминания Хци), соединенного с регистрами 5, 6 через диодные схемы 31 и 32 и через вентили 25-28 регистра 9 (для запоминания разности ΔYi,0, связанного через цифро-аналоговый преобразователь 10 с суммирующим выходным усилителем 16, блока оценки 11, триггера знака 12 и пороговой схемы 13, служащих для сокращения времени интерполяции в цифровом интерполяторе.

Цифровой интерполятор осуществляет интерполяцию между старшими разрядами значений функции в узлах, а аналоговый интерполятор - между младшими разрядами значений функции в узлах.

Устройство работает следующим образом.

Для определенности предполагается, что значения Хцу, Y0 и Yц представлены двоично-десятичным кодом.

По команде начала преобразования из запоминающего устройства 3 на счетчики-регистры 5, 6 в параллельной форме поступают двоично-десятичные коды старших разрядов значений функции в двух соседних узлах интерполяции, адрес которых определяется кодом Хцу.

Регистр 5 хранит значение функции, заданное в четном узле (2i), регистр 6 - в нечетном (2i+1).

Цифровая интерполяция между выбранными значениями кодов Y0,2i и Y0,2i+1 происходит следующим образом. Коды, записанные на счетчиках регистров 5, 6, преобразуются в последовательность импульсов при помощи схемы, состоящей из генератора импульсов 33y, вентилей 17 и 18 и диодных схем 29 и 30, фиксирующих нулевое состояние.

Вентиль 17 представляет собой собирательную схему для сигналов с генератора 33y и выходов 29; вентиль 18 представляет собой собирательную схему для сигналов с генератора 33y и выходов 30.

Последовательности импульсов, соответствующие записанным в регистры 5 и 6 кодам, поступают с выходов вентилей 17, 18 на вентили 19-20. На выходе 20 всегда появляется последовательность импульсов, соответствующая значению функции в узле интерполяции i, а на выходе 19 - в узле (i+1).

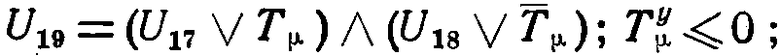

Вентили 19, 20 реализуют следующие логические формулы:

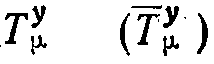

где U17-U20 - выходные напряжения вентилей 17-20;

- младший двоичный разряд двоично-десятичного кода Хц.упр (несет информацию о четности или нечетности выбранного интервала интерполяции).

- младший двоичный разряд двоично-десятичного кода Хц.упр (несет информацию о четности или нечетности выбранного интервала интерполяции).

Какую последовательность импульсов Yi или Yi+1 следует записать в старшую декаду 8 выходного регистра, хранящего Yц, определяет блок оценки 11, управляющий вентилями 21, 22. Работа блока оценки пояснена ниже.

Разность ΔYi,0=(Yi+1,0-Yi,0) определяется с помощью вентилей 23, 24.

Если ΔYi,0>0, то последовательность импульсов, соответствующая разности ΔYi,0, появляется на выходе 23.

Если ΔYi,0<0, то эта последовательность импульсов появляется на выходе 24.

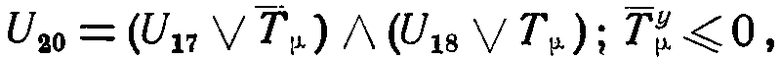

Вентили 23, 24 реализуют следующие логические формулы:

где U23; U24 - выходные напряжения вентилей 23, 24;

a29; a30 - выходные напряжения диодных схем 29, 30.

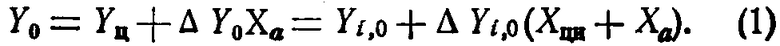

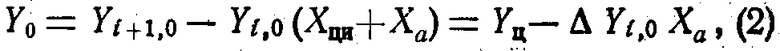

Последовательность импульсов, соответствующая ΔYi,0, записывается в счетчик-регистр 9 и хранится там до следующей команды начала функционального преобразования. С помощью цифро-аналогового преобразователя 10 образуется произведение ΔYi,0·Хан, входящее в основную формулу интерполяции

Знак аналогового произведения ΔY0·X0 определяется триггером знака 12, включенным на выход вентиля 24. Величина произведения ΔYi,0·Хци, входящего в состав формулы (1), образуется путем многократного определения ΔYi,0 и записи этой величины в накапливающий регистр (7, 8).

Для этого код Хци преобразуется в последовательность импульсов, при этом каждый импульс этой последовательности служит командой на начало преобразования.

Преобразования кода Хци в последовательность импульсов выполняет схема, в состав которой входит счетчик-регистр 4, вентили 25-28, диодные схемы, фиксирующие код 0 и код 10 в регистре (31 и 32), а также генератор импульсов 33х.

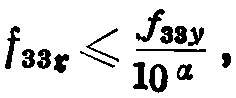

При этом частоты находятся в следующем соотношении:

где α - число разрядов в коде Yi,0.

После окончания цикла преобразования на выходном регистре образуется величина Yц=Yi,0+ΔY0Xци, а на выходе цифро-аналогового преобразователя 10 образуется величина ΔYi,0·Xa, которая суммируется с Ya на аналоговом сумматоре 16.

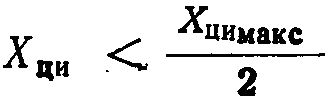

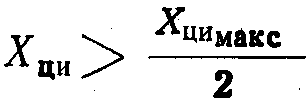

Для сокращения максимального времени функционального преобразования предназначен блок оценки 11, который в зависимости от величины Хци управляет записью в старшую декаду 8 выходного регистра последовательности импульсов, соответствующей Yi или Yi+1, а также направлением счета в выходном счетчике-регистре так, что при  интерполяция осуществляется по формуле (1), а при

интерполяция осуществляется по формуле (1), а при  по формуле

по формуле

где ΔYi,0=Yi+1,0-Yi,0; Xцимакс - максимальное значение кода Хци.

На вход блока оценки воздействует триггер знака 12, несущий информацию о знаке разности ΔYi,0, и схема 13, реагирующая на величину Хци.

Схема 13 реализует формулу

где А - выходное напряжение схемы 13.

Предлагаемый функциональный преобразователь обеспечивает более высокую точность по сравнению с известными функциональными преобразователями с аналоговым выходом, что достигается путем включения в схему функционального преобразователя цифрового интерполятора.

При этом быстродействие предлагаемого функционального преобразователя не хуже, чем быстродействие известных функциональных преобразователей, так как в предлагаемом функциональном преобразователе аналоговый и цифровой интерполяторы работают параллельно во времени.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1972 |

|

SU458004A1 |

| Нелинейный интерполятор | 1985 |

|

SU1267446A1 |

| Устройство для отображенияиНфОРМАции | 1976 |

|

SU798961A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| Генератор векторов для системы отображения графической информации | 1974 |

|

SU525980A1 |

| Линейный интерполятор | 1989 |

|

SU1674064A1 |

| Устройство цифроаналогового преобразования | 1985 |

|

SU1361716A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU395875A1 |

| Нелинейный интерполятор | 1984 |

|

SU1265809A1 |

Функциональный преобразователь для комбинированных вычислительных систем, в которых машинные переменные представлены раздельно цифровой и аналоговой частями, содержащий выходной и входной регистры, запоминающее устройство и устройство для интерполяции, отличающийся тем, что, с целью повышения точности и повышения быстродействия, устройство содержит цифровой и аналоговый интерполяторы и блок оценки, причем входы цифрового интерполятора подключены к старшим разрядам значений функции в узлах интерполирования, хранящихся в регистрах запоминающего устройства, входы аналогового интерполятора соединены с младшими разрядами значений функции в узлах, а блок оценки подключен к входным и выходным регистрам.

Авторы

Даты

1968-07-22—Публикация

1966-11-11—Подача