Ячейки памяти, содержащие элемент памяти на двух последовательно включенных туннельных диодах, транзистор записи и дифференцирующую цепь, известны.

Предлагаемая ячейка отличается тем, что она содержит транзистор считывания, эмиттер которого подключен к точке соединения туннельных диодов, коллектор подсоединен к дополнительному источнику питания, а база через резистор - к генератору тактовых импульсов, причем коллектор транзистора записи подключен к эмиттеру транзистора считывания и к точке соединения туннельных диодов.

Это позволяет увеличить помехоустойчивость, нагрузочную способность генератора тактовых импульсов и значительно уменьшить потребляемую мощность.

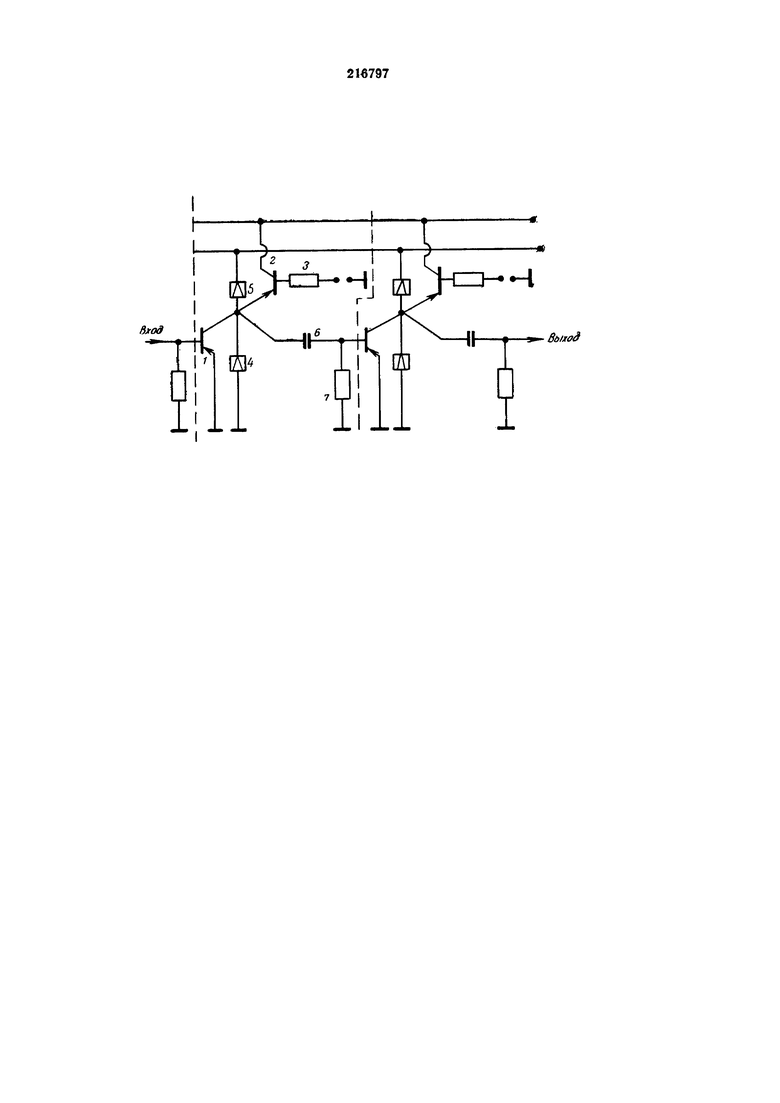

На чертеже приведена принципиальная схема ячейки памяти.

Ячейка состоит из транзистора 1, выполняющего функцию развязки ячеек, записи и усиления сигнала; транзистора 2 с сопротивлением 3, выполняющих функцию считывания информации с элемента памяти и усиления тактового сигнала; элемента памяти на включенных последовательно туннельных диодах 4 и 5 и дифференцирующей цепи 6 и 7.

Наличие сигнала в базе транзистора 1 приводит к отпиранию этого транзистора и переключению коллекторным током элемента памяти из состояния «0» (низковольтное состояние туннельного диода 5 и высоковольтного диода 4) в состояние «1» (высоковольтное состояние туннельного диода 5 и низковольтное диода 4), т.е. происходит запись «единицы» и ее хранение до прихода тактового сигнала. Тактовый импульс отрицательной полярности, подаваемый через сопротивление 3 в базу транзистора 2, отпирает его и током, протекающим в эмиттерной цепи, считывает «единицу», переключая элемент памяти в «0».

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ | 1968 |

|

SU219632A1 |

| УНИВЕРСАЛЬНАЯ ЛОГИЧЕСКАЯ ЯЧЕЙКА | 1968 |

|

SU211880A1 |

| Туннельно-диодно-транзисторная ячейка памяти | 1972 |

|

SU466550A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU347797A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1970 |

|

SU268492A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1973 |

|

SU389548A1 |

| Ячейка памяти | 1973 |

|

SU545007A1 |

| Распределительное устройство | 1982 |

|

SU1083233A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

Ячейка памяти, содержащая элемент памяти на двух последовательно включенных туннельных диодах, транзистор записи и дифференцирующую цепь, отличающаяся тем, что, с целью увеличения помехоустойчивости, нагрузочной способности генератора тактовых импульсов и значительного уменьшения потребляемой мощности, она содержит транзистор считывания, эмиттер которого подключен к точке соединения туннельных диодов, коллектор подсоединен к дополнительному источнику питания, а база через резистор - к генератору тактовых импульсов, причем коллектор транзистора записи подключен к эмиттеру транзистора считывания и к точке соединения туннельных диодов.

Авторы

Даты

1968-07-09—Публикация

1967-01-14—Подача