диоды, аноды которых подключены к шине постоянного напряжения, катоды диодов соединены с базами нагрузочных транзисторов и с третьими эмиттерами м«огоэмиттерных транзисторов.

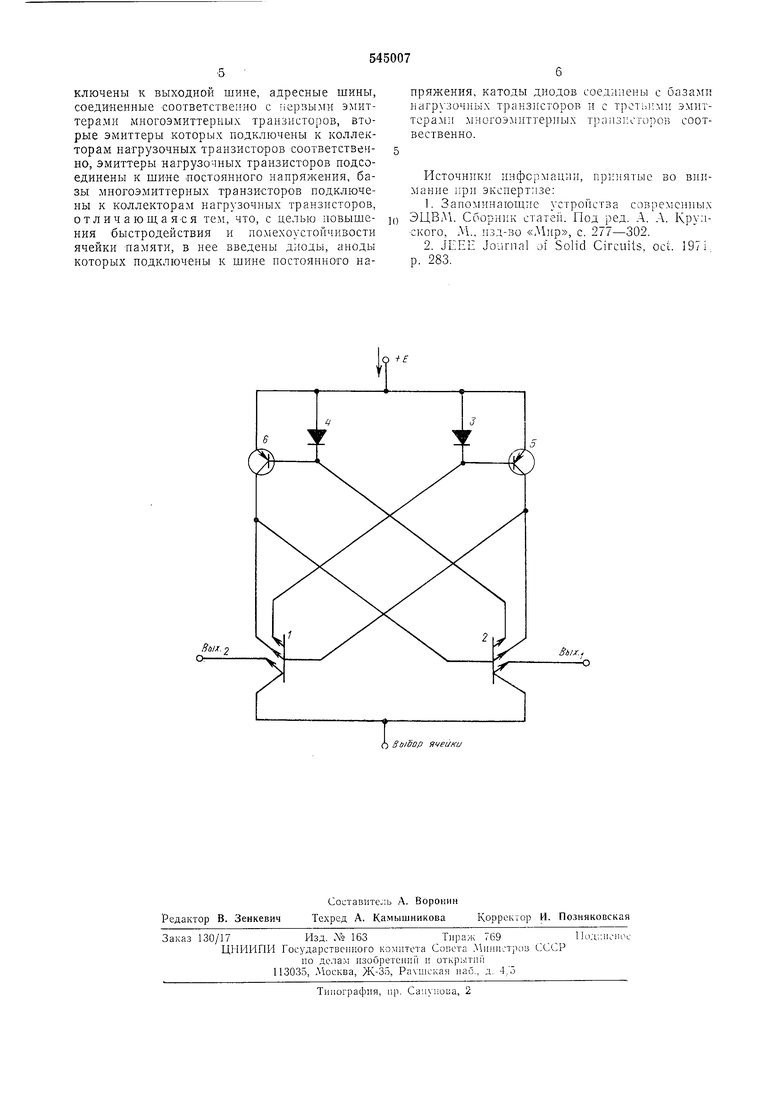

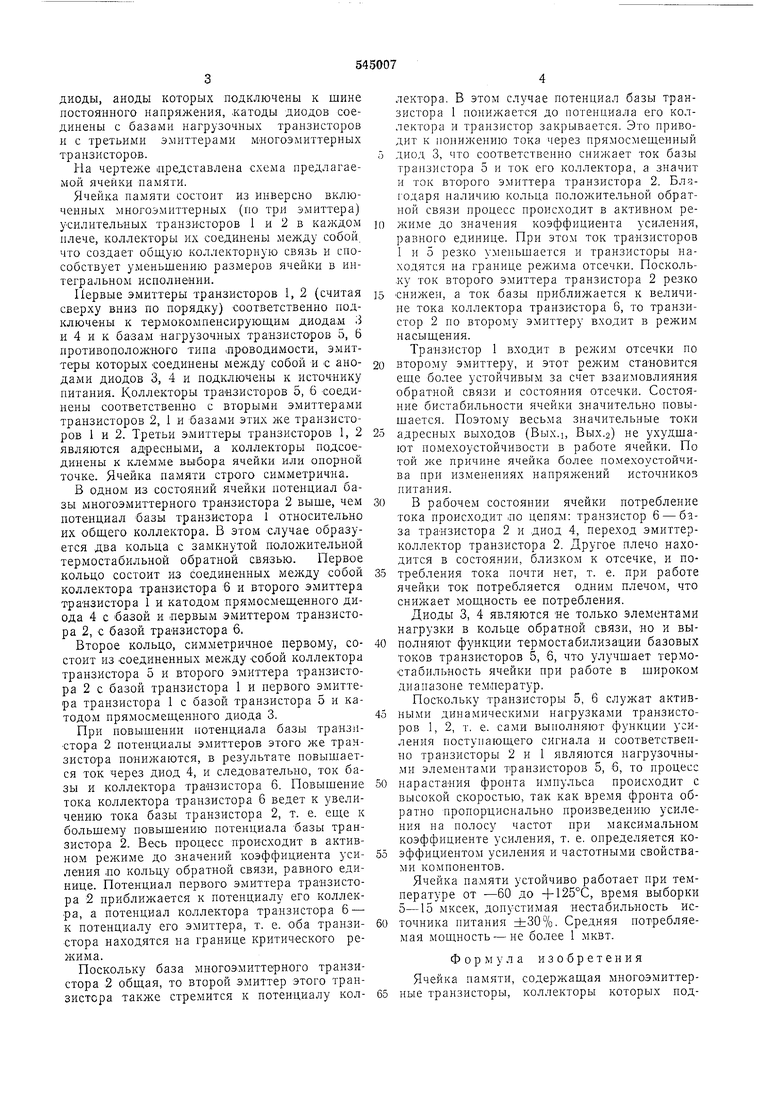

На чертеже представлена схема предлагаемой ячейки памяти.

Ячейка памяти состоит из инверсно включенных многозмиттерных (по три эмиттера) усилительных транзисторов 1 и 2 в каждом плече, коллекторы их соединены между собой что создает общую коллекторную связь и способствует уменьшению размеров ячейки в интегральном исполнении.

Первые эмиттеры транзисторов 1, 2 (считая сверху вниз по порядку) соответственно подключены к термокомпенсируюш,им диодам 3 и 4 и к базам нагрузочных транзисторов 5, 6 противоположного типа .проводимости, эмиттеры которых соединены меладу собой и с анодами диодов 3, 4 и подключены к источнику питания. Коллекторы транзисторов 5, 6 соединены соответственно с вторыми эмиттерами транзисторов 2, 1 и базами этих же транзисторов 1 и 2. Третьи эмиттеры транзисторов 1,2 являются адресными, а коллекторы подсоединены к клемме выбора ячейки или опорной точке. Ячейка памяти строго симметрична.

В одном из состояний ячейки нотенциал базы многоэмиттерного транзистора 2 выше, чем потенциал базы транзистора 1 относительно их обш.его коллектора. В этом случае образуется два кольца с замкнутой положительной термостабильной обратной связью. Первое кольцо состоит из соединенных между собой коллектора транзистора 6 и второго эмиттера транзистора 1 и катодом прямосмещенного диода 4 с базой и -первым эмиттером транзистора 2, с базой транзистора 6,

Второе кольцо, симметричное первому, состоит из соединенных между собой коллектора транзистора 5 и второго эмиттера транзистора 2 с базой транзистора 1 и первого эмиттера транзистора 1 с базой транзистора 5 и катодом прямосмещенного диода 3.

При повыщении потенциала базы транзистора 2 потенциалы эмиттеров этого же транзистора понижаются, в результате повышается ток через диод 4, и следовательно, ток базы и коллектора транзистора 6. Повыщение тока коллектора транзистора 6 ведет к увеличению тока базы транзистора 2, т. е. еще к большему повышению потенциала базы транзистора 2. Весь процесс происходит в активном режиме до значений коэффициента усиления по кольцу обратной связи, равного единице. Потенциал первого эмиттера транзистора 2 приближается к потенциалу его коллекра, а потенциал коллектора транзистора 6 - к потенциалу его эмиттера, т. е. оба транзистора находятся на границе критического режима.

Поскольку база многоэмиттерного транзистора 2 общая, то второй эмиттер этого транзистора также стремится к потенциалу коллектора. В этом случае потенциал базы транзистора 1 понижается до потенниала его коллектора и транзистор закрывается. Это приводит к понижению тока через прямосмещенный диод 3, что соответственно снижает ток базы транзистора 5 и ток его коллектора, а значит и ток второго эмиттера транзистора 2. Благодаря наличию кольца положительной обратной связи процесс происходит в активном режиме до значения коэффициента усиления, равного единице. При этом ток транзисторов 1 и 5 резко уменьшается и транзисторы находятся на границе режима отсечки. Поскольку ток второго эмиттера транзистора 2 резко снижен, а ток базы приблим;ается к величине тока коллектора транзистора 6, то транзистор 2 но второму эмиттеру входит в режим насыщения.

Транзистор 1 входит в режим отсечки по второму эмиттеру, и этот режим становится еще более устойчивым за счет взaи roвлияния обратной связи и состояния отсечки. Состояние бистабильности ячейки значительно повышается. Поэтому весьма значительные токи адресных выходов (Вых.ь Вых.г) не ухудшают помехоустойчивости в работе ячейки. По той л-се причине ячейка более помехоустойчива при изменепиях напряжений источников питания.

В рабочем состоянии ячейки потребление тока происходит .по цепям: транзистор 6 - база транзистора 2 и диод 4, переход эмиттерколлектор транзистора 2. Другое плечо находится в состоянии, близком к отсечке, и потребления тока почти нет, т. е. при работе ячейки ток потребляется одним плечом, что снижает мощность ее потребления.

Диоды 3, 4 являются не только элементами нагрузки в кольце обратной связи, но и выполняют функции термостабилизации базовых токов транзисторов 5, 6, что улучшает термостабильность ячейки при работе в широком диапазоне температур.

Поскольку транзисторы 5, б служат активными динамическими нагрузками транзисторов 1, 2, т. е. сами вынолняют функции усиления поступающего сигнала и соответственно транзисторы 2 и 1 являются нагрузочными элементами транзисторов 5, 6, то процесс нарастания фронта импульса происходит с высокой скоростью, так как время фронта обратно пропорционально произведению усиления на полосу частот при максимальном коэффициенте усиления, т. е. определяется коэффициентом усиления и частотными свойствами компонентов.

Ячейка намяти устойчиво работает при температуре от -60 до +125°С, время выборки 5-15 мксек, допустимая нестабильность источника питания ±30%. Средняя потребляе мая мощность - не более 1 мквт.

Формула изобретения

Ячейка памяти, содержащая многоэмиттерные транзисторы, коллекторы которых подключены к выходной шине, адресные шины, соединенные соответственно с ерзыми эмиттерами многоэмиттерных транзисторов, вторые эмиттеры которых подключены к коллекторам нагрузочных транзисторов соответственно, эмиттеры нагрузочных транзисторов подсоединены к шине постоянного напряжения, базы многоэмиттерных транзисторов подключены к коллекторам нагрузочных транзисторов, отличающаяся тем, что, с целью повышения быстродействия и помехоустойчивостн ячейки Памяти, в нее введены диоды, аноды которых подключены к шине ностоянного Haб

пряжения, катоды днодов соединены с базами нагрузочных транзисторов и с троть.ими эмнтTcpa- iu многоэмиттерных трлнзиоторов соотвественно.

Источники информации, принятые во в)1Имание при экспертизе:

1.Запоминаюшие устройства современных ЭЦВМ. Сборник статей. Под ред. А. А. Крупского, М.. нзд-во «Aiiip, с. 277-302.

2.JIiEc Journal of Solid Circuits, oct. 197i p. 283.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ясейка памяти | 1974 |

|

SU521605A1 |

| Ячейка памяти | 1974 |

|

SU536527A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| Ячейка памяти | 1973 |

|

SU444245A1 |

| Логическое устройство | 1977 |

|

SU738171A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Ассоциативный запоминающий элемент | 1983 |

|

SU1130900A1 |

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

| Операционный усилитель | 1973 |

|

SU470815A1 |

SbiSap ячеики

Авторы

Даты

1977-01-30—Публикация

1973-11-28—Подача