Универсальные лопические ячейки, содержа Щие элемент па1мяти на двух последо вательно включенных туннельных диодах и транэлсгоры считывания, иавастны, требуют строгих допусков на параметры туннельных диодов и источников питания.

Предложенная ячейка содержит дополнительные транзисторы сброса, включенные по схеме с общим эмиттером, коллекторы которых соединены вместе и подключены к точке соединения туннельных диодов элемента памяти, а базы через резисторы - к источникам сигналав сброса.

Такое иаполнение позволяет расшир-ить допуски на параметры туннельных диодов и источники питания.

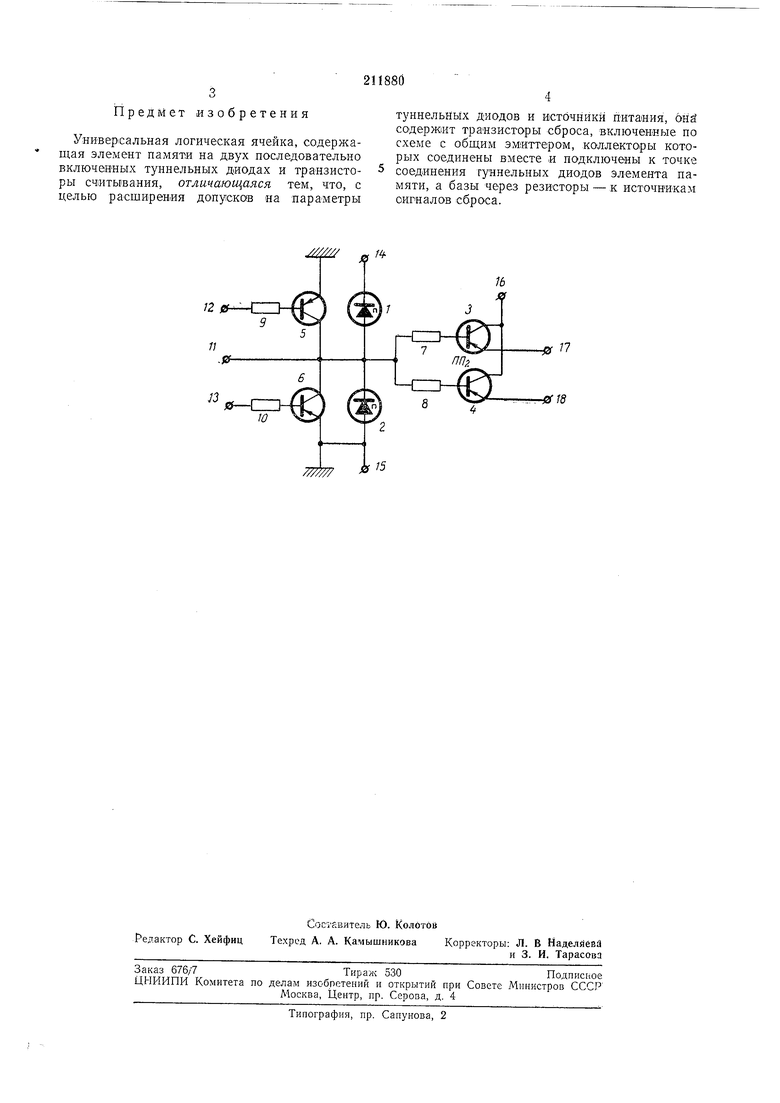

Универсальная логическая ячейка, представленная на чертеже, состоит из узла ламяти на двух последовательно включенных туннельных диодах / « 2, узла считывания на транзисторах 5 и 4 и резисторах 7 ,и 8, узла сброса на транзисторах 5 и 5 и резисторах Р и 10.

Узел памяти имеет два устойчивых состояния, одно из которых условно принимается за «едашичное (низковольтное состояние туннельного диода 2 и высоковольтное - д;иода 1, а другое - за «нулевое (высоковольтное состояние туннельного диода I и низ1ковольтное - диода 2).

Пусть в исходном состоянии в ячейке записан «нуль, т. е. туннельный диод 2 на.ходится в низкоБОльтнОМ состоянии. При этом напряжение на выходе узла памяти практически равно нулю.

Поэтому считывающие цранзисторы имеют нулевой потенциал базы и их коллектсрные переходы закрыты. В коллекторы считывающих транзисторов подают короткие тактовые импульсы от генератора.

Так как транзисторы считывания закрыты, то ток в эмиттерах от этих импульсов мал и незначительно превыщает обратный ТОК коллекторного перехода. При записи информации Е ячейку туннельный диод I перейдет Б высоковольтное состояние, транзисторы 3 и 4 войдут в насыщение и к приходу тактового импульса будут представлять собой замкнутые ключи, через которые импульс тока будет нроходить на выход ячейки 17 н 18. Сброс информации осуществляется путем подачи сигналов сброса на заж1имы 12 или 13.

Предмет изобретения

Универсальная логическая ячейка, содержащая элемент памяти на двух последовательно включенных туннельных диодах и транзисторы считывания, отличающаяся тем, что, с целью расширения долускав на параметры

туннельных диодов и источники питания, они содержит транзисторы сброса, включенные по схеме с общим эмиттером, коллекторы которых соединены вместе и подключены к точке соединения туннельных диодов элемента памяти, а базы через резисторы - к источникам сигналов сброса.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ | 1967 |

|

SU216797A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU347797A1 |

| ЯЧЕЙКА ПАМЯТИ | 1968 |

|

SU219632A1 |

| РЕГИСТР СДВИГАПйТЕН t iiu* Ii:AJi г.: .:- ?:.a\! | 1972 |

|

SU350048A1 |

| ПАТ?Ш'Ш-[1ХСГ'Е^:чДП | 1973 |

|

SU362487A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «НЕ-ИЛИ» | 1971 |

|

SU305588A1 |

| ВСЕСОЮЗНАЯ ПЛТгеТ1Ш-ТГШ:^;Е;л?= | 1973 |

|

SU363194A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| ПЕРЕКЛЮЧАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU371686A1 |

-сй я f

0 77

018

;5

Авторы

Даты

1968-01-01—Публикация