Известны запоминающие устройства с непосредственной выборкой числовых линеек.

Предлагаемое запоминающее устройство (ЗУ) отличается тем, что снабжено дополнительным устройством выборки числовых линеек со входами разрещения логического сложения и логического умножения, выходы которого через балластные резисторы соединены с дополнительными числовыми шинами соответствующих линеек.

Это позволяет выполнять логические операции «ИЛИ, «И в каждой линейке ЗУ.

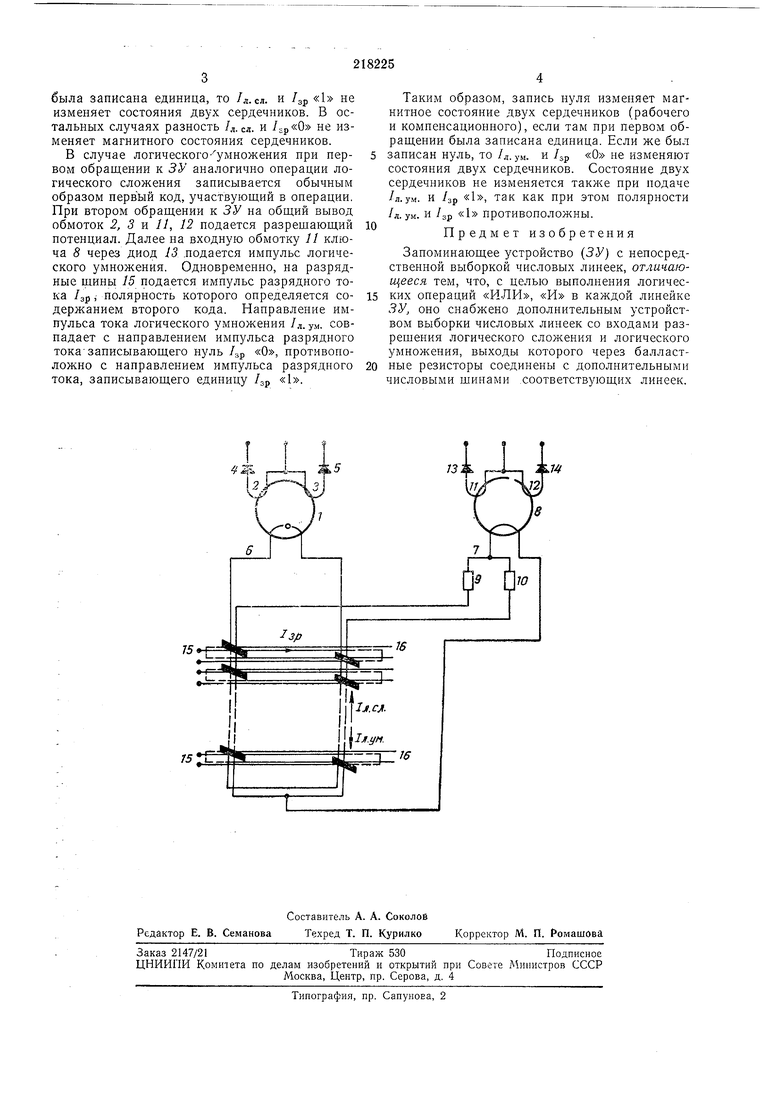

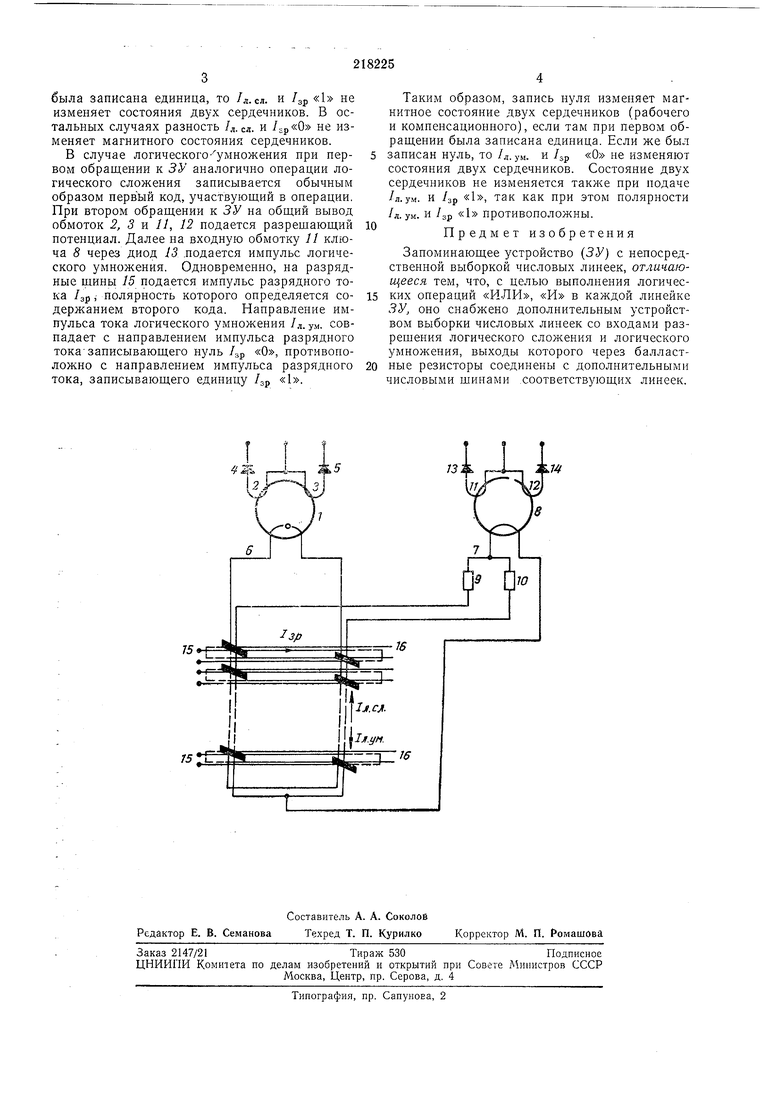

На чертеже показана схема числовой линейки описываемого оперативного запоминающего устройства с двумя сердечниками на знак.

Схема выборки числовой линейки представляет собой диодно-трансформаторный ключ /, на первичные обмотки 2 н 3 которого через диоды 4 и 5 подаются соответственно импульсы чтения и записи.

Выходная обмотка 6 ключа / образует числовую шину. Выходная обмотка 7 дополнительной схемы выборки, выполненная также на диодно-трансформаторном ключе 5, через балластные резисторы 9 н 10 образует дополнительную числовую шину.

На первичные обмотки 11 и 12 ключа 8 через диоды 13 и 14 подаются соответственно импульсы логического умножения и логического сложения. На общий вывод обмоток 2,

3 и //, 12 подается потенциал, разрещающий выборку ключей / и 8.

Помимо числовых шин через сердечники проходят также разрядные шины 15 и шины считывания 16.

Схема работает следующим образом.

Онерации логического сложения и логического умнолсения выполняются за два обраще ния к оперативному ЗУ. При первом обращении в данную числовую линейку записывается первый код, участвующий в операции обычным образом, как это принято в схемах ЗУ, с непо средственной выборкой использующих разнополярную запись «1 и «О.

При логическом сложении на входную обмотку 12 ключа 8 через диод 14 подается импульс логического сложения. Одновременно с этим на разрядные шины 15 подается импульс разрядного тока /зр, полярность которого определяется содержимым второго кода. Направление импульса тока логического сложения /.л.сл. совпадает с направлением импульса разрядного тока, записывающего единицу /зр «1, и противоположно с направлением импульса разрядного тока, записывающего нуль

/зр «О.

Таким образом, запись единицы изменяет магнитное состояние двух сердечников (рабочего и компенсационного), если там при нервом обращении был записан нуль. Если же

была записана единица, то /л. ел. и /зр «1 не изменяет состояния двух сердечников. В остальных случаях разность /л. ел. и /sp«0 не изменяет магнитного состояния сердечников.

В случае логического умножения при первом обращении к ЗУ аналогично операции логического сложения записывается обычным образом первый код, участвующий в операции. При втором обращении к ЗУ на общий вывод обмоток 2, 3 я 11, 12 подается разрешающий потенциал. Далее на входную обмотку 11 ключа 8 через диод 13 .подается импульс логического умножения. Одновременно, на разрядные щины 15 подается импульс разрядного тока /зр,- полярность которого определяется содержанием второго кода. Направление импульса тока логического умножения /л. ум. совпадает с направлением импульса разрядного токазаписывающего нуль /зр «О, противоположно с направлением импульса разрядного тока, записывающего единицу /зр «1.

Таким образом, запись нуля изменяет магнитное состояние двух сердечников (рабочего и компенсационного), если там при первом обращении была записана единица. Если же был записан нуль, то /л. ум. и /зр «О не изменяют состояния двух сердечников. Состояние двух сердечников не изменяется также при подаче /л. ум. и /зр «1, так как при этом полярности

/л. ум. и /зр «1 противоположны.

Предмет изобретения

Запоминающее устройство (ЗУ) с непосредственной выборкой числовых линеек, отличающееся тем, что, с целью выполнения логических операций «ИЛИ, «И в каждой линейке ЗУ, оно снабжено дополнительным устройством выборки числовых линеек со входами разрешения логического сложения и логического умнол ения, выходы которого через балластные резисторы соединены с дополнительными числовыми шинами .соответствующих линеек.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU341083A1 |

| ЬИЬЛИО', ЕКА | 1973 |

|

SU365707A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| ЧИСЛОВАЯ ЛИНЕЙКА ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1973 |

|

SU375677A1 |

| УСТРОЙСТВО ПАМЯТИ и РЕГИСТРАЦИИ | 1968 |

|

SU217463A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU295143A1 |

4J

75

Даты

1968-01-01—Публикация