Известны устройства для управлений цифровым дифференциальным анализатором последовательного типа, содержащее долговременное запоминающее устройство (ДЗУ), регистры, счетчики и логические схемы.

Предлагаемое устройство отличается тем, что оно содержит сдвигающие регистры с логическими обратными связями, входы которых через логические схемы соединены с выходом регистра считывания долговременного запоминающего устройства, а выходы подключены ко входам схемы «И».

Это позволяет сэкономить память долговременного запоминающего устройства.

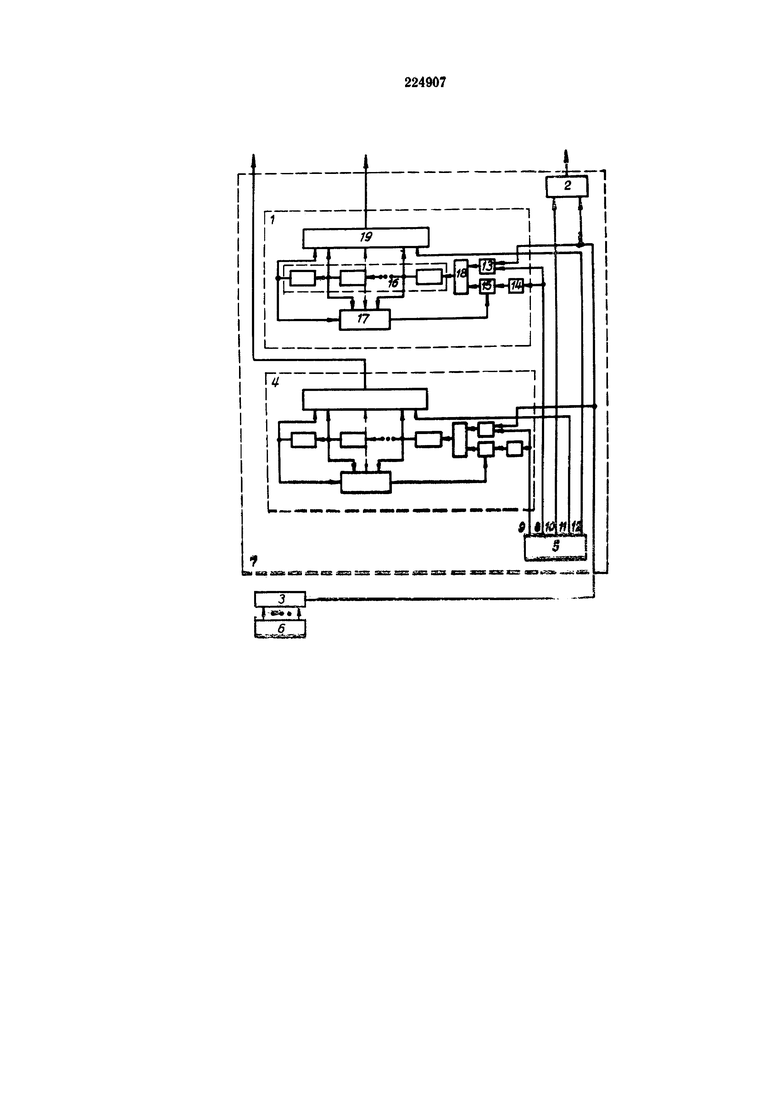

Структурная схема предлагаемого устройства управления цифровым дифференциальным Анализатором (ЦДА) последовательного типа на основе памяти с произвольным обращением изображена на чертеже.

Формирователь адреса записи 1 (AΔZ) предназначен для преобразования K-разрядного кода адреса AΔZ в n-разрядную кодовую последовательность с одной единицей (n - количество приращений, записанных в регистре хранения приращений РХП), на чертеже не показан. По адресу AΔZ приращения с выходов интеграторов записываются в РХП. Кодирование адреса AΔZ рассмотрено ниже. Формирователь адреса 2 (АΔУ) предназначен для выделения адреса АΔУ в информации, поступающей из регистра считывания 3 ДЗУ. По адресу АΔУ считываются приращения из РХП на вход ΔУ интегратора. Формирователь адреса 4 (АΔХ) предназначен для преобразования K-разрядного кода адреса AΔX в n-разрядную кодовую последовательность с одной единицей. По адресу АΔХ считывания приращения из РХП подаются на вход ΔX интегратора.

Кодирование адреса AΔX рассмотрено ниже.

Схема тактирования 5 предназначена для выработки последовательности синхронизирующих и управляющих импульсов для отсчета интеграторов в пределах одной итерации, пуска и останова ЦДА, включения различных режимов работы. Долговременное запоминающее устройство 6 на магнитных сердечниках предназначено для хранения адресов АΔУ и кодов адресов AΔX, AΔZ.

Регистр считывания 3 ДЗУ предназначен для преобразования параллельного кода, в котором считывается информация из ДЗУ в последовательный код.

Рассмотрим работу формирователей адресов приращений в течение одного цикла интегрирования.

Коды адресов АΔХ, AΔZ и адрес АΔУ записаны в AΔУ 6. Они считываются из ДЗУ в регистр. 3 параллельным кодом. Из регистра считывания 3 информация выдается в устройство управления 7 последовательным кодом. Вначале поступает код адреса AΔZ, В это время на выходе 8 схемы тактирования 5 появляются одна за другой K единиц, а на выходах 9, 10, 11 и 12 этой схемы устанавливаются нули. В формирователе, адреса AΔZ единицы с выхода 8 схемы тактирования открывают схему «И», 13 и закрывают с помощью схемы «НЕ» 14 схему «И» 15. Таким образом, цепь обратной связи 16 регистра 17 разомкнута, и формирователь адреса 1 AΔZ работает в режиме ввода кода адреса. Код адреса AΔZ при этом вводится последовательно через схемы «И» 13 и «ИЛИ» 18 в регистр 17. Затем из регистра считывания 3 начинает поступать код адреса AΔX. В это время на выходе 9 схемы тактирования 5 появляются одна за другой K единиц, на выходе 12 - n единиц, а на выходах 8, 10 и 11 устанавливаются нули.

Формирователь адреса 4 (АΔХ) работает в режиме ввода кода адреса.

Формирователь адреса 1 [AΔZ) начинает работать в режиме декодирования, за кодом адреса AΔX из регистра считывания 3 начинает поступать n-разрядный адрес AΔУ. В это время на выходах 10 и 11 схемы тактирования 5 появляются одна за другой n единиц, а на выходах 8 и 9 устанавливаются нули. На выходе 12 продолжают появляться единицы. Адрес AΔУ проходит в РХП. Формирователь адреса 1 (АΔZ) продолжает работать в режиме декодирования, Декодирование в каждом из формирователей длится n тактов. Поэтому процесс декодирования в формирователе 1 заканчивается раньше, чем выдача АΔУ из регистра 3. Когда выдача адреса АΔУ закончена, формирователь 1 готов к вводу кода адреса AΔZ для следующего интегратора.

В следующем цикле интегрирования формирователи адресов работают аналогично.

Рассмотрим работу формирователя 1 в режиме декодирования. В этом режиме на выходе 8 схемы тактирования установлены нули, а на выходе 12 появляются n единиц подряд.

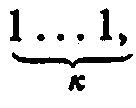

Цепь обратной связи регистра 17 замкнута через схемы «И» 15 и «ИЛИ» 18. Информация в регистре 17 сдвигается влево на один разряд в каждом такте. При этом образуется новая K-разрядная комбинация. Если это - комбинация  то на выходе схемы «И» 19 появляется единица; в противном случае на выходе схемы «И» 19 появляется нуль. Схема «И» 19 открыта в течение n тактов единицами с выхода 12 схемы тактирования 5. За это время комбинация

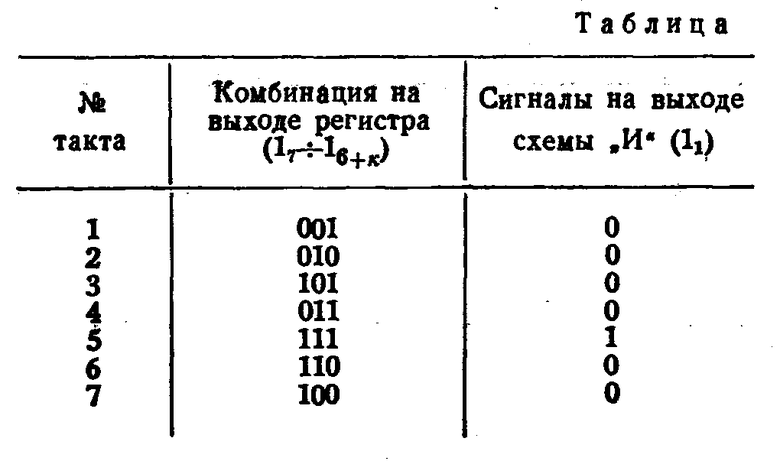

то на выходе схемы «И» 19 появляется единица; в противном случае на выходе схемы «И» 19 появляется нуль. Схема «И» 19 открыта в течение n тактов единицами с выхода 12 схемы тактирования 5. За это время комбинация  появится только один, раз, так как n≤2к-1 где (2к-1) количество различных комбинаций, вырабатываемых регистром 17. Следовательно, на выходе схемы «И» 19 действительно вырабатывается n-разрядная последовательность с одной единицей. Причем единица в этой последовательности будет именно на j-ом месте, где (2к-j) - номер K-разрядной комбинации, с которой формирователь начал свою работу в режиме декодирования (т.е. номер введенного кода-адреса). Пусть, например, (см. табл.) в формирователь 1 введена комбинация 001, представляющая собой код адреса 0000100. Тогда регистром (17÷16+к) комбинации будут выработаны в порядке, указанном в столбце 2 таблицы, а последовательность сигналов на выходе схемы «И» (11) будет иметь вид, указанный в столбце 3 этой таблицы.

появится только один, раз, так как n≤2к-1 где (2к-1) количество различных комбинаций, вырабатываемых регистром 17. Следовательно, на выходе схемы «И» 19 действительно вырабатывается n-разрядная последовательность с одной единицей. Причем единица в этой последовательности будет именно на j-ом месте, где (2к-j) - номер K-разрядной комбинации, с которой формирователь начал свою работу в режиме декодирования (т.е. номер введенного кода-адреса). Пусть, например, (см. табл.) в формирователь 1 введена комбинация 001, представляющая собой код адреса 0000100. Тогда регистром (17÷16+к) комбинации будут выработаны в порядке, указанном в столбце 2 таблицы, а последовательность сигналов на выходе схемы «И» (11) будет иметь вид, указанный в столбце 3 этой таблицы.

Из таблицы видно, что введя в формирователь комбинацию с номером (23-5), действительно получаем на выходе схемы «И» (11) семиразрядную последовательность с одной единицей, расположенной в пятом разряде. Формирователь адреса АΔХ в режиме декодирования работает аналогично. Схема тактирования 5 в предлагаемом устройстве управления работает так же, как и в известных устройствах.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ЦИФРОВОЙ МОДЕЛИ | 1967 |

|

SU223472A1 |

| Долговременное запоминающее устройство | 1979 |

|

SU860136A1 |

| Долговременное запоминающее устройствоСО ВСТРОЕННыМ КОНТРОлЕМ | 1979 |

|

SU830588A1 |

| ДОЛГОВРЕМЕННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU343306A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU335718A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| УСТРОЙСТВО для ОБРАБОТКИ СЕЙСМИЧЕСКОЙ ИНФОРМАЦИИ | 1970 |

|

SU273452A1 |

| Устройство для сбора и кодирования информации с годоскопических детекторов и многопроволочных пропорциональных камер | 1990 |

|

SU1835529A1 |

| Устройство для регистрации ритма сердечной деятельности и характера его изменений | 1978 |

|

SU784867A1 |

| СПОСОБ И УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ | 1995 |

|

RU2117388C1 |

Устройство для упрвления цифровым дифференциальным анализатором последовательного типа, содержащее долговременное запоминающее устройство, регистры, счетчики и логические схемы, отличающееся тем, что, с целью сокращения оборудования устройства, оно содержит сдвигающие регистры с логическими обратными связями, входы которых через логические схемы соединены с выходом регистра считывания долговременного запоминающего устройства, а выходы подключены ко входам схемы «И».

Авторы

Даты

1968-12-08—Публикация

1967-04-05—Подача