(54) ДОЛГОВРЕМЕННОЕ ЗАПОМИНАЮЩЕЕ УСТРСЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Запоминающее устройство | 1990 |

|

SU1791851A1 |

| Постоянное запоминающее устрой-CTBO | 1979 |

|

SU809379A1 |

| Долговременное запоминающее устройствоСО ВСТРОЕННыМ КОНТРОлЕМ | 1979 |

|

SU830588A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1709396A1 |

| ДОЛГОВРЕМЕННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU343306A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

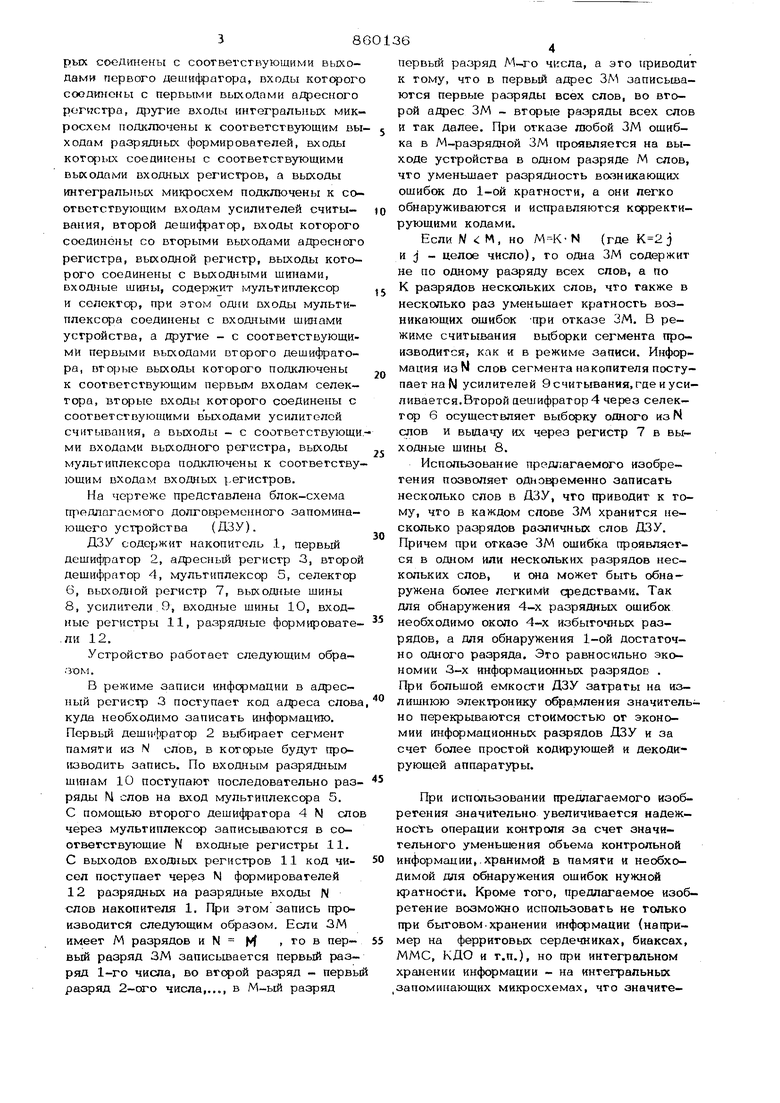

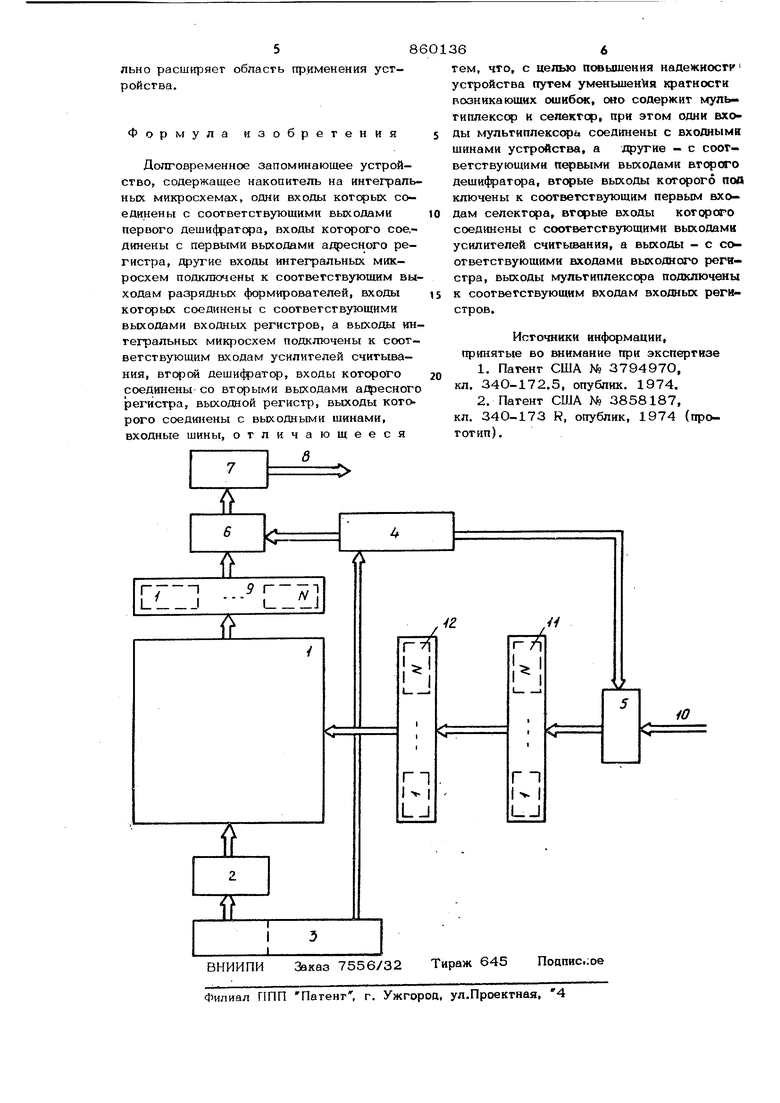

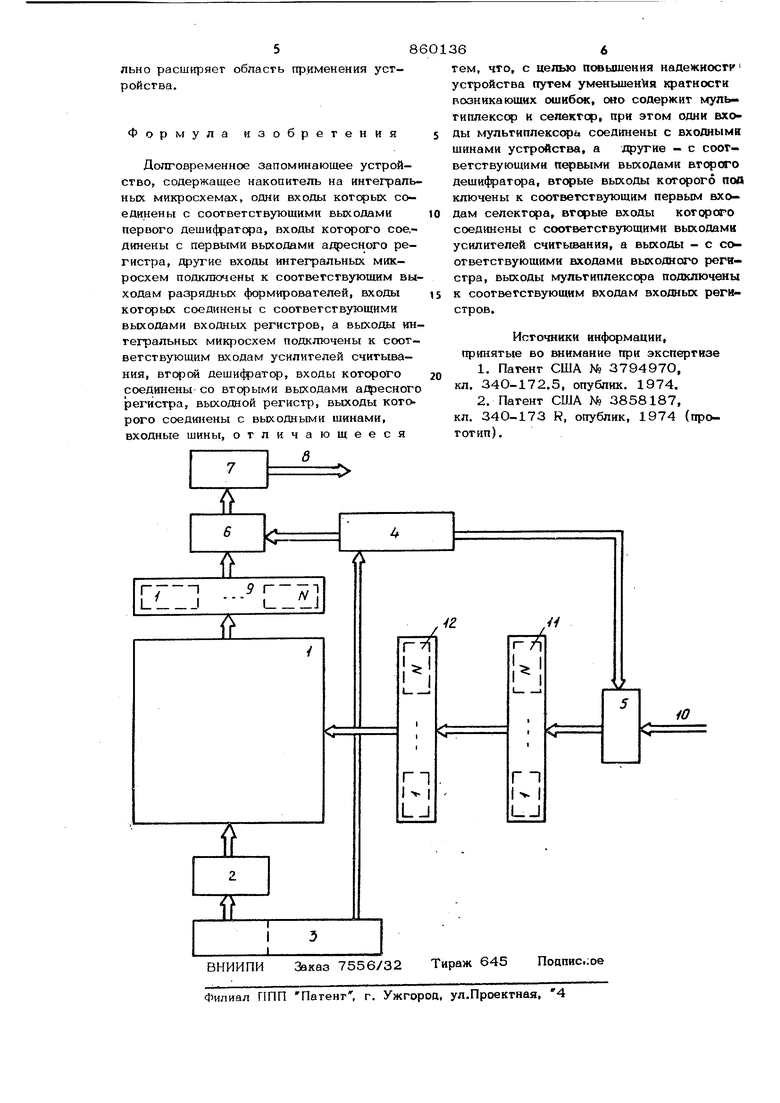

Изобретение огносигся к вычислйгельной технике, в часгносги к долговременным запоминающим устройствам (ДЗУ) на интеграпьньк запоминающих микросхемах (ЗМ) словарного типа с электрИческЫ1 перезаписью информации. Известно долговременное запоминающее устройство на интегральных запоминающих мшфосхемах, которое содержит накопитель состоящий из секций, каждая секция которого хранит слово и при считывании и записи одновременно выбираются слова иа разных секций ij. Недостатком такого устройства являегся большое количество оборудования в раз рядной части блока памяти и возникновение многократной ошибки. Наиболее близким по технической сушноств к предлагаемому является устрсйст- во, содержащее накопитель, один вход которого соединен с соответствующими выходами первого дешифратсфа, входы кота рого соединены с первыми выходами адресного регистра, другие входы накопитеЛЯ подключены к соответствующим вькодам ра ялных формирователей, входы которых соединены с соответствующими выходами входных регистров, а выходы нако пителя подключены к соответствующим входам усилителей считыванкя, вторсА дешифратор, вхошы когсрого соединены со вторыми выходами афесного регистра, вы ходной регистр, выходы которого соединены с выходными щш1ам11, входные щины. Недостатсж известного устройства возникновение многократных ошибок прв использовании в качестве элементе памяти многораарядаых ЗМ caioi apHoro тепа, что проводит к большой избыточности в контрольных разрядах, а это снижает надежность устройства. Цель изобретения - аовыщение надежности устрсЛства. путем уменьшения кратности возникающих ошибок. Указанная цель достигается тем, что известное долговременное запоминающее устройство, содержащее накопитель, на mw тегральных микросхемах, одни входы которых cocflmieHH с соотвегсгвующими вькодами первого дешифратора, входы когсрого СООДИ11ОНЫ с первыми выходами адресного porvjcrpa, другие входы интегральных микросхем подключены к соответствующим вы ходам разрядньк формирователей, входы которых соединены с соответствующими выходами входных регистров, а выходы интегральных; микросхем подключены к со отоетствующим входам усилителей считывания, второй дешифратор, входы которого соединены со вторыми выходами адресного регистра, выходной регистр, выходы которого соединены с выходными шинами, входные шины, содержит мультиплексор и селектор, при этом орлк входы мультиплексора соединены с входными шинами устройства, а другие - с соответствующими первыми выходами второго дешифратора, вторые выходы которого подключены к соответствующим первым входам селектора, вторые входы которого соединены с соответствуюшими вььходами усилителей считывания, а выходы - с соответствующи ми входами вьисодного регистра, выходы мультиплексора подключены к соответству ющим входам входных регистров. На чертеже представлена блок-схема предлагаемого долговременного запоминающего устройства (ДЗУ). ДЗУ содержит накопитель 1, первьШ дешифратор 2, адресньй регистр 3, второй дешифратор 4, мультиплексор 5, селектор 6, выходной регистр 7, выходные шины 8, усилители, 9, входные шины 10, входные регистры 11, разрядные формировате-ли 12. Устройство работает следующим образом. В режиме записи информации в адресный регистр 3 поступает код адреса слов куда необходимо записать информацию. Первый дешифратор 2 выбирает сегмент памяти из N слов, в которые будут производить запись. По входным разрядным шинам 10 поступают последовательно раз ряды N слов на вход мультиплексора 5. С помощью второго дешифратора 4 N сло через мультиплексор записьшаются в соогвегсгвующие N входные регистры 11. С выходов входных регистров 11 код чисел поступает через N формирователей 12 разрядных на разрядные входы N слов накопителя 1. При этом запись производится следующим образом. Если ЗМ имеет М разрядов и N И , то в пер- 55 вый разряд ЗМ записьшается первый разряд 1-го числа, во втqэoй разряд - первый разряд 2-аго числа,..., в М-ый разряд

первый разряд М-го числа, а это приводит к тому, что в первый адрес ЗМ записьша- югся первые разряды всех слов, во вгорой адрес ЗМ - вторые разряды всех слов И так далее. При отказе любой ЗМ ошнбка в М-разрядной ЗМ проявляется на выходе устройства в одном разряде М слов, что уменьшает разрядность возникающих ошибок до 1-ой кратности, а они легко обнаруживаются и исправляются корректирующими кодами. Если N :М, но (где j и j - целое число), то одна ЗМ содержит не по одному разряду всех слов, а по К разрядов нескольких слов, что также в несколько раз уменьшает кратность возникающих ошибок При отказе ЗМ, В режиме считывания выбфки сегмента производится, как и в режиме записи. Информация из N слов сегмента накопителя поступает на N усилителей 9 считывания, где и усиливается.Второй дешифратор 4 через селектор 6 осуществляет выбелку одного из N слов и выдачу их через регистр 7 в выходные шины 8. Использование предлагаемого изобретения позволяет одновременно записать несколько слов в ДЗУ, чго приводит к тому, что в каждом слове ЗМ хранится несколько разрядов различных слов ДЗУ. Причем при отказе ЗМ ошибка проявляется в одном или нескольких разрядов нескольких слов, и она может быть обнаружена более легкими средствами. Так для обнаружения 4-х разрядньгх ошибок необходимо около 4-х избыточных разрядов, а для обнаружения 1-ой достаточно одного разряда. Это равносильно экономии 3-х инфсфмацисжных разрядов . При большой емкости ДЗУ затраты на излишнюю электронику обрамления значительно перекрываются стоимостью от экономии информационных разрядов ДЗУ и за счет более простой кодирующей и декодирующей аппаратуры. При использовании предлагаемого изобретения значительно увеличивается надежность операции контроля за счет значительного уменьшения объема контрольной информации,.хранимой в памяти и необходимой для обнаружения ошибок нужной кратности. Кроме того, предлагаемое изобретение возможно использовать не только при бытовом-хранении информации (например на ферриговых сердечниках, биаксах, ММС, КДО и т.п.), но при интегральном хранении информации - на интегральных .запоминающих микросхемах, что значительио расширяет область применения устройства.

Формула изобретения

Долговременное запоминающее устройство, содержащее накопитель на интегральньсх. микросхемах, одни входы котфых соединены с соответствующими выходами первого дешифрат эа, входы которого сое,динены с первыми вькодамн адресного регистра, другие входы интегральных микросхем подключены к соответствующим выходам разрядных формирователей, входы которых соединены с соответствующими вькодами входных регистров, а выходы интегральных микросхем подключены к соответствующим входам усилителей считывания, второй дешифратор, входы которого соединены со вторыми вькодами адресного регистра, ВЬЕХ.ОДНОЙ регистр, выходы которого соединены с выходными шинами, входные шины, отличающееся

8

тем, что, с целью псвьоиения надежносп устройства путем ум сьшен я крагносги возникающих ошибок, оно содержит мультиплексор и сепекгор, при этом одни входы мультиплексора соединены с входными щиками устройства, а другие - с соогветствующими первыми выходами агор ото дещифратора, вторые выходы которого пой ключены к соотвегствующим первым входам селектора, вторые входы которого соединены с соответствующими выходами усилителей считывания, а выходы - с соответствующими входами выходного регистра, выходы мультиплексора подключены к соответствующим входам входных регистров.

Источники информации, принятые во внимание при экспертизе

кл. 34О-173 R, опублик, 1974 (прототип).

Авторы

Даты

1981-08-30—Публикация

1979-07-13—Подача