Изобретение относится к области вычислительной техники и может быть использовано в устройствах хранения и обработки информации.

Известны долговременные запоминающие, устройства (ДЗУ), содержащие накопитель с усилителями сброса и считывания информации, регистр адреса, дешифратор адреса, регистр числа и блок декодирования ошибок.

Однако эти ДЗУ громоздки, тяжелы и сложны, т. к. операция первоначальной записи информации в ДЗУ является весьма трудоемкой. ДЗУ известной конструкции не позволяют декодировать ошибки в адресной части. При необходимости декодировать эти ошибки требуется ввести дополнительное устройство.

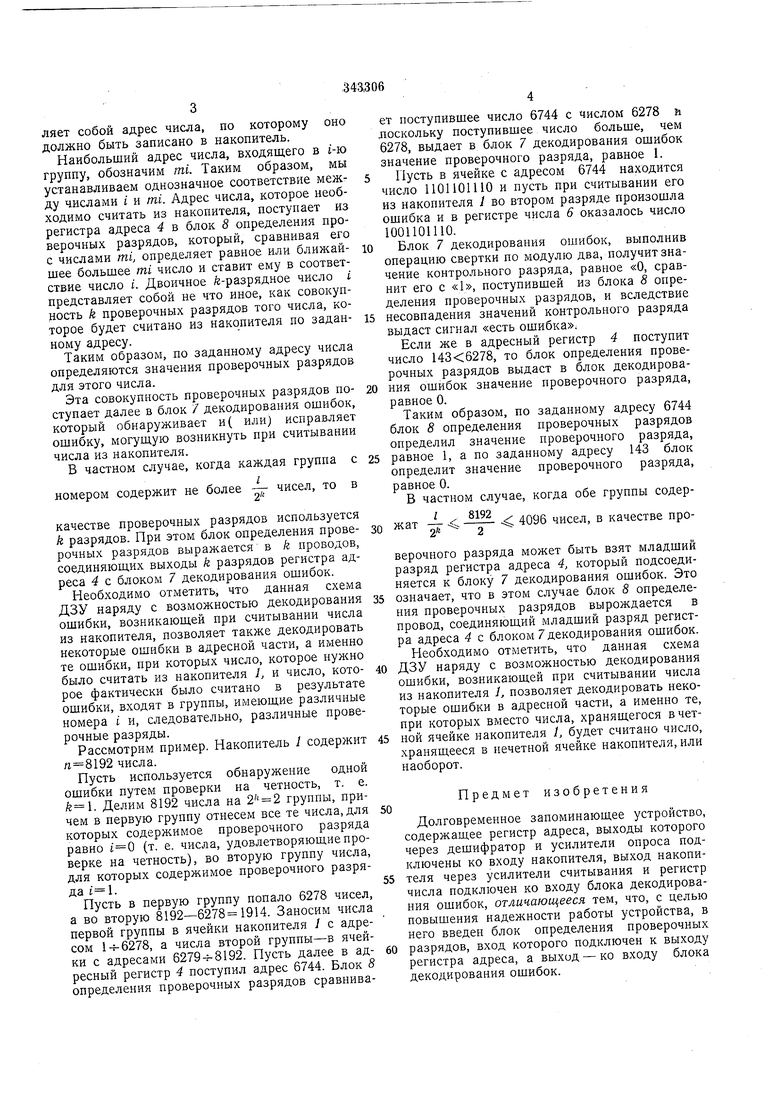

Целью изобретения является повыщение надежности работы устройства, для чего в устройство введен блок определения проверочных разрядов, вход которого подключен к выходу регистра адреса, а выход-ко входу блока декодирования ошибок.

Иа чертеже приведена блок-схема предлагаемого ДЗУ.

число из накопителя; дешифратор адреса 5 для дешифрирования адреса числа; регистр числа 6 для промежуточной памяти числа, считанного из накопителя; блок 7 декодирова;ния ошибок для обнаружения и (или) исправления ошибок, возникающих при считывании числа из накопителя, и блок 8 определения проверочных разрядов для определения проверочных разрядов числа.

Накопитель / и регистр числа 6 содержат только п информационных разрядов и не содержат проверочных разрядов. Блок 8 определения проверочных разрядов анализирует содержимое регистра адреса 4 и определяет значения проверочных разрядов, которые далее поступают в блок 7 декодирования ошибок.

Предложенное устройство работает следующим образом. Пусть выбран код, содержащий п информационных и k проверочных разрядов при . И пусть в накопителе нужно записать / чисел. Разобьем множество / чисел на 2 групп, причем в г-ю группу отнесем все те числа, для которых совокупность проверочных разрядов,

ляет собой адрес числа, по которому оно должно быть записано в накопитель.

Наибольший адрес числа, входящего в i-ю группу, обозначим mi. Таким образом, мы устанавливаем однозначное соответствие между числами i и mi. Адрес числа, которое необходимо считать из накопителя, поступает из регистра адреса 4 в блок 8 определения проверочных разрядов, который, сравнивая его с числами mi, определяет равное или ближайшее большее mi число и ставит ему в соответствие число I. Двоичное fe-разрядное число i представляет собой не что иное, как совокупность k проверочных разрядов того числа, которое будет считано из накопителя по заданному адресу.

Таким образом, по заданному адресу числа определяются значения проверочных разрядов для этого числа.

Эта совокупность проверочных разрядов поступает далее в блок 7 декодирования ошибок, который обнаруживает и( или) исправляет ошибку, могуш.ую возникнуть при считывании числа из накопителя.

В частном случае, когда каждая группа с

номером содержит не более чисел, то в

ft

качестве проверочных разрядов используется /г разрядов. При этом блок определения проверочных разрядов выражается в /г проводов, соединяюш,их выходы /е разрядов регистра адреса 4 с блоком 7 декодирования ошибок.

Необходимо отметить, что данная схема ДЗУ наряду с возможностью декодирования ошибки, возникаюш,ей при считывании числа из накопителя, позволяет также декодировать некоторые ошибки в адресной части, а именно те ошибки, при которых число, которое нужно было считать из накопителя I, и число, которое фактически было считано в результате ошибки, входят в группы, имеющие различные номера i и, следовательно, различные проверочные разряды.

Рассмотрим пример. Накопитель I содержит числа.

Пусть используется обнаружение одной ошибки путем проверки на четность, т. е. . Делим 8192 числа на 2 2 группы, причем в первую группу отнесем все те числа, для которых содержимое проверочного разряда равно (т. е. числа, удовлетворяющие проверке на четность), во вторую группу числа, для которых содержимое проверочного разряда .

Пусть в первую группу попало 6278 чисел, а во вторую 8192-6278 1914. Заносим числа первой группы в ячейки накопителя I с адресом 1-7-6278, а числа второй группы-в ячейки с адресами 6279-ь 8192. Пусть далее в адресный регистр 4 поступил адрес 6744. Блок 8 определения проверочных разрядов сравнивает поступившее число 6744 с числом 6278 и доскольку поступившее число больше, чем 6278, выдает в блок 7 декодирования ошибок значение проверочного разряда, равное 1. Пусть в ячейке с адресом 6744 находится число 1101101110 и пусть при считывании его из накопителя I во втором разряде произошла ошибка и в регистре числа 6 оказалось число

loqiioiiio.

Блок 7 декодирования ошибок, выполнив операцию свертки по модулю два, получит значение контрольного разряда, равное «О, сравнит его с «1, поступившей из блока и определения проверочных разрядов, и вследствие

несовпадения значений контрольного разряда выдаст сигнал «есть ошибка.

Если же в адресный регистр 4 поступит число , то блок определения проверочных разрядов выдаст в блок декодирования ошибок значение проверочного разряда, равное 0.

Таким образом, по заданному адресу 6744 блок 8 определения проверочных разрядов определил значение проверочного разряда,

равное 1, а по заданному адресу 143 блок определит значение проверочного разряда, равное 0. В частном случае, когда обе группы содер8192

30 жат

- 4096 чисел, в качестве проверочного разряда может быть взят младший разряд регистра адреса 4, который подсоединяется к блоку 7 декодирования ошибок. Это

означает, что в этом случае блок S определения проверочных разрядов вырождается в провод, соединяющий младший разряд регистра адреса 4 с блоком 7 декодирования ошибок. Необходимо отметить, что данная схема

ДЗУ наряду с возможностью декодирования ошибки, возникающей при считывании числа из накопителя 1, позволяет декодировать некоторые ошибки в адресной части, а именно те, при которых вместо числа, хранящегося в четной ячейке накопителя I, будет считано число, хранящееся в нечетной ячейке накопителя, или наоборот.

Предмет изобретения

Долговременное запоминающее устройство, содержащее регистр адреса, выходы которого через дешифратор и усилители опроса подключены ко входу накопителя, выход накопителя через усилители считывания и регистр числа подключен ко входу блока декодирования ошибок, отличающееся тем, что, с целью повышения надежности работы устройства, в него введен блок определения проверочных

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| Устройство кодирования и декодирования информации | 1990 |

|

SU1783628A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО„. -..,-•. ."р л С^аог^'-.---'^--:: '•^k^Vfi''-'- | 1973 |

|

SU375675A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1989 |

|

SU1780191A1 |

Даты

1972-01-01—Публикация