Известны арифметические устройства снециализироваииых цифровых вычислительных машин, содержащие сумматоры накопительного тииа, сдвигающие регистры, ключи, блок управления, а также схему анализа множителя и схему определения частного.

Предложенное устройство отличается от известных тем, что оно содержит схемы «Исключенного ИЛИ, причем выходы первого регистра сдвига подсоединены ко входам первых схем «Исключенного ИЛИ, другие входы которых соединены с блоком управления, выходы схем подключены ко входам первого сумматора. Выходы второго регистра сдвига связаны со входами вторых схем «Исключенного ИЛИ, вторые входы которых соединены с блоком управления. ВЫХОДЕ : этих схем иодключен) ко входам второго сумматора. Выходы третьего регистра сдвига иодсоелинены через третьи схемы «Исключенного ИЛИ, также соединенные с блоком управления, ко входам третьего сумматора. Выходы суммы и иереиоса первого сумл1атора подключены через соответствующие ключи, связанные с блоком управлеиия, ко вторым схемам «Исключенного ИЛИ, а выходы третьего сумматора через ключи подсоединены ко второму регистру сдвига.

В устройстве использован способ умножения с промежуточным суммированием частных гроизведений с убыстрением расиространениь переносов при окончательном суммировании.

Этот способ умножения с aнaлнзo. нескольких разрядов удачно сочетается с одним из методов асмнхронного деления с логическим убыстрением, основанном на уменьшении разрядной сетки остатка, используемого для определения знака и цифр частного.

Извлечение квадратного корня основано на следующих соотношениях:

7

+ /(2 + (А) У,,, + , .2( + ;2-) X, О, УО о, sign (,) - ,. О

., Х,,. const.

Все указанные операции могут быть реали25 зоваиы в структуре, в состав которой входят три накопительных регистра и ряд регистров сдвига.

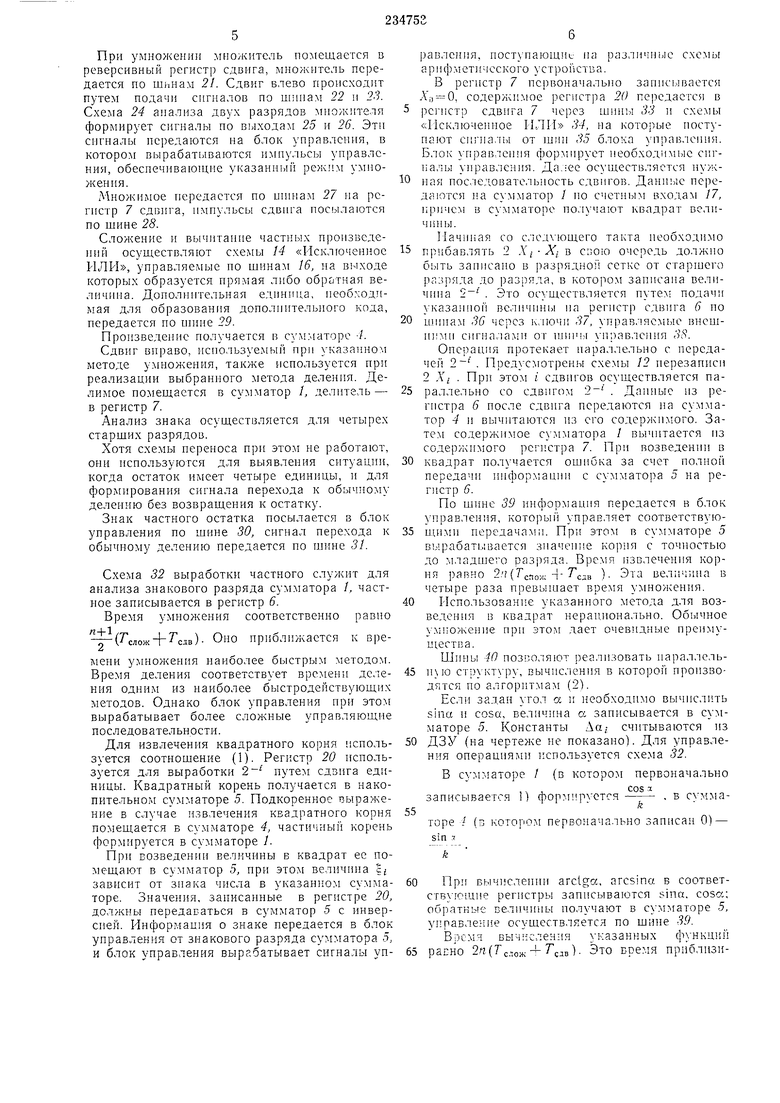

рсноса, схемы 3 межгруппового переноса, сумматоры 4 и 5 пакопителы-юго типа, регистры 6 и 7 сдвига, шину 8 сигнала блока управлепия, П1нну 9 переноса, ключп W, пишу 11 управления, схемы 12 «Исключенное ИЛИ, гиимы управления, схемы 14 «Р1сключеи11ое ИЛИ, шины 15 передачи слагаемых, илшу 16 управдеиия, счетные входы 17, шину 18 управления, ключ /Я реверсивный регистр 20 сдвига, шину 21 нодачи множителя, шины 22 н 23 -правления, схему 24 анализа двух разрядов множителя, выходы 25 и 26 схемы анализа множителя, шины 27 подачи множимого, шину 28 нодачи имнульсов сдвига, 29 подачи еднпицы, шину 30 подачи знака частиого остатка, шину 31 подачи сигнала нрн комбипанпп 1111, схему 32 выработки цифр частного, ншну 33 нередачн содержимого регистра, cxeMiji 34 «РТсключепного ИЛИ, нгииы 35 управления, ншны 36 нередачи, ключи 37, нн1ны 38 унраилення, шины 39 управления, шины 40 передачи, схему 41 «Исключенное

ИЛИ.

Трпгонометрнческие операции вычислення основаны на соотношепнях:

Yi + -cfXi2xC,:-f 1 ИГ; ; YI

Да,- : arctg2а : V n, Да,

1

C l

sin y.

я л n

П COS AoijП COS ЛУ.

Иервый сумматор / со схемами 2 внутригруппового переноса п схемами 3 межгруппового переноса идентичен наконнтельныА сумматорам 4 и 5. Эти блоки используются для реалнзаинн операцнн алгебранческого сложения. Региетры 6 н 7 также идентичны но конетрукцнн.

Так как сложение является очень важной оне|1а1и ей, как это следует нз анализа реигае.11)1х задач, расс.мотрим вначале О|)1аннзаци1() сложения в предлагаемом блоке.

Каждый сумматор 1, 4, 5 нмеет пезавиеимую систему адресации, что позволяет ускорить суммирование в трн раза. Однако статнетические нселедовапия программ показывают, что такой режим реализовать трудно.

Ряд ноеледовательных сложений типичен для умножения, поэтому должны быть предусмотрены соответствующие аппаратурные решения, позволяюш,не сократить время, затрачиваемое на это.

В предлагаемом устройстве используется еледующнй метод сложения.

1 1 1 1 Иервое слагаемое ИЕРВОЕ СЛОЖЕИИЕ

11 Второе слагаемое

00000Иервая сумма 11111 Иервая группа перепосов 00000 Первая логнчеокая сумма ВТОРОЕ СЛОЖЕНИЕ

11111 Третье слагаемое 11111 Вторая сумма 00000 Вторая группа переносов 11111 Иервые переносы 0 0) О Вторые нереносы 11111 Вторая логическая сумма ТРЕТЬЕ СЛОЖЕИЙЕ

Четвертое слагаемое

00000 Третья логическая сумма 11111 Иервые нереносы 11111 Результпруюшне нереносы

Вторые переносы

111110 Результат

Из примера следует, что нерепосы во втором накопительном регистре генерируются в два раза медленнее, чем в том случае, еслн бы онн вырабатывались в первом регистре в обычном режиме сложения.

Логическое сложение осуш,ествляется в сумматоре 1, причем соответствуюш,ие схемы переноса не работают.

Иереносы суммируются в сумматоре 4, в котором также предусмотрены соответствуюш.ие схемы переноса.

Указанный лгетод умножения имеет следующие временные характеристики: каждый цикл характеризуется операцией сложения и сдвига, поэтому нод время раснространения переноса в другом регистре отводят по крайней мере два указанных интервала времени. Так как это время достаточно для раснространения нереносов, нолное время сложения т чисел равно (т-1-1) ( + 5сдв)При многократном сложеннн схемы переноса су гматора / отключаются сигналом, передаваемым по шине 8, и сигналы переноса регистра передаются по шине 9 па ключи 10, управляемые сигналами но шинам //. Ключи 10 подсоедииены к схемам 12 «Исключенное ИЛРЬ, унравляемым блоком унравления по шинам 13 (блок управления на чертеже не представлен).

Обычное сложение обеспечивается обычной нпструкцией алгебраического сложения.

Если сложение осуществляется в сумматоре /, слагаемые посылаются через схемы 14 от ппгн 15. Схемы 14 получают спгналы управления но шинам 16. Выходы схемы 14 связаны со ечетнымн входамн 17 сумматора /.

Переносы наканливаются в регистре 7, и после окончательного сложения блок управления формирует сигнал по шнне 18, в результате чего открывается ключ 19 и разрешается сложение содержимого сумматора / с содержимым сумматора 4.

При умножении множитель помещается в реверсивный регистр сдвига, множитель передается по шинам 21. Сдвиг влево происходит путем подачи сигналов ио шинам 22 и 23. Схема 24 анализа двух разрядов множителя формирует сигналы ио выходал 25 и 26. Эти сигналы передаются на блок управления, в котором вырабатываются импульсы унравления, обеснечиваюи1,ие указанный режим умножения.

Множимое передается по ишнам 27 на регистр 7 сдвига, импульсы сдвига посылаются по шине 28.

Сложение и вычитанне частных произвсдеиий осуш,ествляют схемы 14 «Исключенное ИЛИ, управляемые ио шинам 16, на выходе которых образуется ирямая либо обратная величина. Дополнительная единина, необход мая для образования доиолннтельного кода, передается по niinie 29.

Произведение получается в сум.маторе /.

Сдвиг вправо, используемый при указанном методе умножения, также используется при реализации выбранного метода деления. Делимое помещается в сумматор 1, делитель - Б регистр 7.

Анализ знака осуществляется для четырех старших разрядов.

Хотя схемы переноса при этом не работают, они используются для выявления ситуации, когда остаток имеет четыре единицы, и для формирования сигнала перехода к обычному делению без возвращения к остатку.

Знак частного остатка посылается в блок управления ио шние 30, сигнал иерехода к обычному делению передается по шине 31.

Схема 32 выработки частного служит для анализа знакового разряда сумматора /,, частное записывается в регистр 6.

Время умножения соответственно равно

(слож-j- сдв) Оно нрнближается к времеии умножения наиболее быстрым методом. Время деления соответствует времени деления одним из наиболее быстродействующих методов. Однако блок управления ири этом вырабатывает более сложные управляющие последовательности.

Для извлечения квадратного корня используется соотношение (1). Регистр 20 используется для выработки путем сдвпга единицы. Квадратный корень получается в накопительном сумматоре 5. Подкоренное выражение в случае извлечения квадратного корня помещается в сумматоре 4, частичный корень формируется в сумматоре 1.

При возведении величины в квадрат ее помещают в сумматор 5, при этом величина с зависит от знака числа в указанном сумматоре. Значения, записанные в регистре 20, должны передаваться в сумматор 5 с инверсией. Информан1 я о знаке передается в блок управления от знакового разряда сумматора 5, и блок управления вырабатывает сигналы управления, ноступающи на различные схемы арифметического ycTpoiiCTBa.

В регистр 7 первоначаль)ю записывается А;, 0, содержимое регистра 20 передается в

сдвига 7 через 33 и схемы «Псключеиное ИЛИ 34, на которые поступают сигиа,1ы от шли 35 блока управления. Блок управления формирует необходимые сигналы управления. Да::ее осуществляется нужиая после;ювательиость сдвигов. Данные передаются на с мматор / но счетным входам 17, в с мматорс пол Чают квадрат величтил.

Начиная со следмошего такта необходимо

прибавлять 2 .( Xi в С1;ою очередь должио быть записано в разрядной сетке от старшего разряда до разряда, в котором записана величина . Это осун1ествляется путем подачи указанной величины на регистр сдвига 6 ио

36 через ключи 37, управляемые внсшИ1 Л И сигналами ог шины управлсиня 38.

Операция протекает параллельно с передачей 1 . Предусмотрены схемы 12 перезаписи 2 Xi . При этом i сдвигов осуществляется параллельно со сдвигом . Данные из регистра 6 после сдвига передаются на сумматор 4 и вычитаются из его содержимого. Затем содержимое сумматора / вычитается из содержимого регистра 7. При возведении в

квадрат получается ошибка за счет полиой передачп ииформации с сумматора 5 на регистр 6.

По шине 39 информация передается в блок управления, который управляет соответствующими передачами. При этом в сумматоре 5 вырабатывается зиачепие корня с точностью до младшего разряда. Врсмп 11звлечения корня равно 2. (Гспож т-Тсдв ). Эта величина в четыре раза превьпиает время умножения.

Использование указанного метода для возведения в квадрат нераилонально. Обычное умножение при этом дает очевидные преимущества.

Шпны 40 позволяют реализовать параллельп ю структуру, вычисления в которой производятся по алгоритмам (2).

Если задан угол а, и необходимо вычислить sina и COSH, величина а заиисывается в сумматоре 5. Константы Да/ счнтынаются из

ДЗУ (на чертеже не показано). Для управления операциями используется схема 32.

В сумматоре / (в котором первоначально

., .cos 3.

заиисывается 1) формируется , в суммаk

торе / (в котором первоначально записан 0) - sin у.

При вычислении arctga, arcsina в соответствуюпдие регистры записываются sina. cosa;

обратные келичины получают в сумматоре 5,

управление осуществляется по 39.

Время вычисления указанных функц Й тельно в четыре раза превышает время умножения. Известны различные методы интегрирования. Формулы, основанные на усреднении в частной области, редко исиользуются на нрактике, так как их трудно реализовать в специализироваиных устройствах тина ПДА, а также в других специализированных вычислительных устройствах. Преимундеством указанных формул является существенное убыстрение вычислений. Устройство, реализующее указанные формулы, сиособно отрабатывать в реальном масщтабе времени нроцессы с относительно высокой граничной частотой. Формулы второго порядка имеют вид: Yn.A УП + 1 п + 2 4- Лз . В предлагаемом устройстве К„, , Уп-i, У ,г хранятся в магнитном оперативном запомииающем устройстве (МОЗУ). Для убыстреиия ироцесса передачи констант из ДЗУ (.4,, А.,, А-л) они иередаются через специальиые клрочи (иа чертеже не показаны) на регистр 20. В результате выполнения поднрограммы интегрирования множимые (У„, Yn-i, Ул-2) подаются в регистр 7 и осуществляется оиераиия умиожения и быстрого сложения ряда величин. Интегрирование занимает время з/2 (п-р +4)7слож -|-/2(«+2)Гсдв , только в три раза иревышаюидее время умножения. Предлагаемое арифметическое устройство обладает высоким быстродействием и исиользует специфику круга рещаемых задач. Предмет пзобретения Арифметическое устройство сиециализпроваппой цифровой вычислительной мащины на сумматорах накопительного типа, сдвигающих регистрах, ключах, содержащее блок управления, схему анализа множителя, схему определения частиого, отличающееся тем, что, с целью повыщения эффективности устройства при выполиении арифметических операций- вычислении квадратного корня, прямых и обратных тригонометрических функций и иитегрирования, оно содержит схемы «Исключенного ИЛИ, причем выходы первого регистра сдвига подсоединены ко входам первых схем «Исключенного ИЛИ, другие входы которых соединены с блоком управления, выходы схем нодключены ко входам первого сумматора; выходы второго регистра сдвига связаны со входами вторых схем «.Исключенного Р1ЛИ, вторые входы которых соединены с блоком управления, выходы этих подключены ко входам второго сумма тора; выходы третьего регистра сдвига подсоедииеиы через третьи схемы «Исключепного ИЛИ, также соедипенные с блоком управления, ко входам третьего сумматора, выходы суммы и переноса первого сумматора подключены через соответствующие ключи, связанные с блоком управления, ко вторым схемам «{-1сключенного ИЛИ, а выходы третьего су.мматора через ключи подсоединены ко второму регистру сдвига.

J, 2 31 г

яда 17 7Г 4; foftf rif i i л.

ti

ji7 L JL J 75 « 7 (

a № .Pl Fn: CP:,n СР;/8гКР /г -Р.И )гЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| Арифметическое устройство | 1973 |

|

SU650072A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1971 |

|

SU302002A1 |

Даты

1969-01-01—Публикация