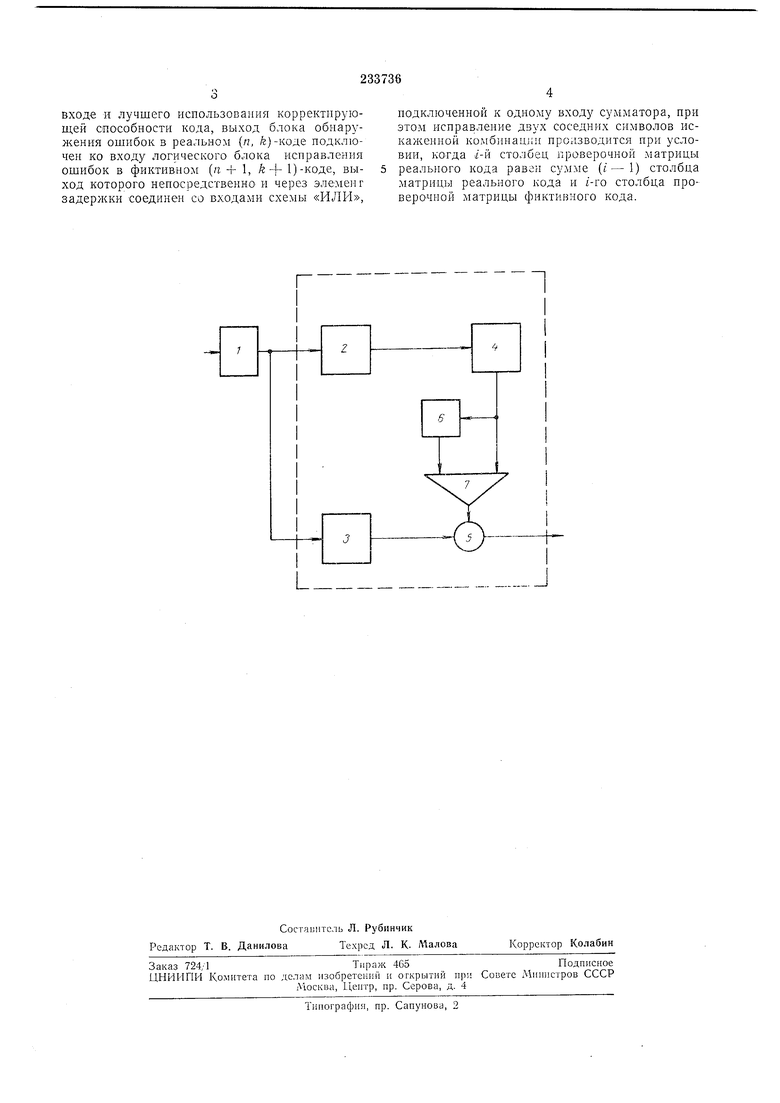

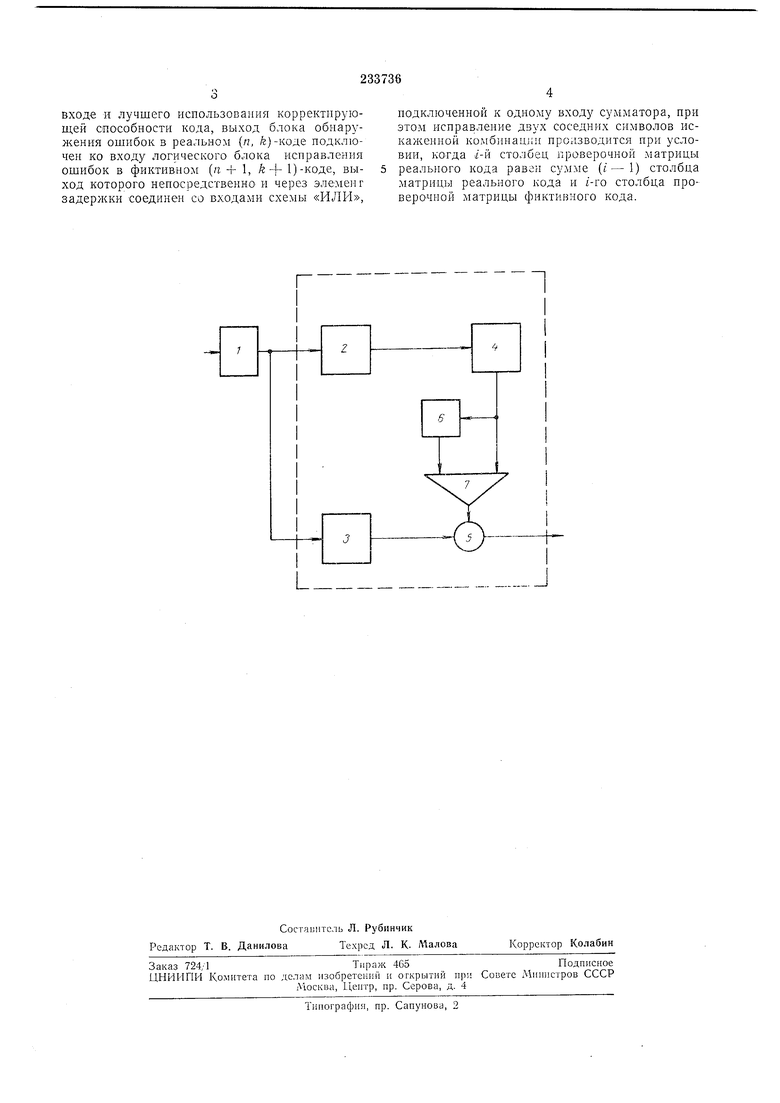

Известны устройства для устранения эффекта размножения ошибок ири относительной фазовой модуляции, ири которых между фазовььм детектором и иеремножителем нрием.ника включено декодирурощее устройст- 5 во рекуррентного кода. Педостатко1М таких устройств является то, что ириемник должен быть построен обязательно по способу сравнения полярности и ме- 10 тод сравнения фаз ие может быть иснользоваи. Особенностью описываемого устройства является то, что выход блока обнаружения ошибок в реальном (п, ft)-коде иодключен ко вхо- 15 ду логического блока исправления ошибок в фш тивном (л+1, /гЧ-1)-коде, входной сигнал логического блока с помогцью элемента задержки и схемы «НЛР производит исправление двух смежных символов искаженной пи- 20 формации, при этом г-й столбец проверочной матрицы реальиого кода равен сумме (i-1) столбца матрицы реального кода и г-го столбца проверочной матрицы фиктивного кода. Указанные отличия позволяют уменьшить чис- 25 ло независимых ошибок на входе и лучше использовать корректируюшую способность кода. Сущность нзобретения состоит в том, что па передающей стороне кодирование производится обычным образом с помощью реального ЗО кода, а прием осуществляется с использованием декодпрующего устройства. На чертеже показана блок-схема декодпрующего устройства. Информация из капала, преобразованная в фазовом детекгоре /, поступает па блок 2 обнаружения ошибок, формируюн ий синдром по матрице реального кода, н на иакоиптель 3 кодовой комбинации. Логический блок 4 исправления ошибок форм 1рует с 1Г11ал исправления в соответствии с матрицей фиктивного кода. Каждый сигнал исправления ошибок производит исправлеаие двух соседних символов в сумматоре 5 с помощью элемента 6 задержки иа один такт и схе.мы 7 типа «ИЛИ. В системе без исправления ошибок накопитель 3, блок 4, эле.мент 6 и су.:матор 5 не используются. И р е д м е т изобретения Декодирующее устройство для канала связи с передачей двоичной информации с помощью относительной фазовой модуляции, содержащее иакопитель кодовой комбинации, блок обнаружения ошибок, логический блок для псиравления ошибок, сумматор и регистр задержки, отличающееся тем, что, с целью уменьшения числа независимых ошибок иа

входе и лучшего использования корректирующей опособиости кода, выход блока обиаружения ошибок в реальном {«, й)-коде подключен ко входу логического блока исправления ошибок в фиктивном (п + 1, /г+ 1)-коде, выход которого непосредственно и через элемеи г задержки соединеи со входами схемы «ИЛИ,

подключенной к одному входу сумматора, при этом исправление двух соседних символов искаженной комбинации про,1зводится при условии, когда 1/-Й столбец проверочной матрицы реального кода равен сумме (1-1) столбца матрицы реального кода и /-го столбца проверОЧИой матрицы фиктивного кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодер циклического кода | 1988 |

|

SU1599996A1 |

| Устройство для декодирования двоичного кода | 1984 |

|

SU1220128A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО РЕКУРРЕНТНОГО КОДА | 1967 |

|

SU205877A1 |

| СПОСОБ И ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ДВУХ ОШИБОК В ПРИНИМАЕМОМ КОДЕ | 2006 |

|

RU2336559C2 |

| Устройство для исправления стираний | 1989 |

|

SU1633498A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Устройство для декодирования с коррекцией ошибок | 1988 |

|

SU1584108A1 |

Даты

1969-01-01—Публикация