Изобретение относится к области вычислительной техники и может быть использовано в цифровых интегрирующих машинах.

Известные преобразователи числовой информации, содержаидие регистры, схему сравнения, счетчик, схему запрета и группу вентилей, не иреобразуют числа в последовательность многоразрядных приращений.

Предлагаемое устройство отличается тем, что выходы старших разрядов регистра соединены с первыми входами схемы сравнения, вторые входы которой соединены с выходами счетчика, а выход соединен с запрещающим входом схемы запрета и с разрешающим входом группы клапанов, вторые входы которых соединены с выходами младших разрядов регистра, а выходы - с первыми входами сборок, вторые входы которых соединены с выходом схемы запрета.

Это позволяет расширить функциональные возможности преобразователя.

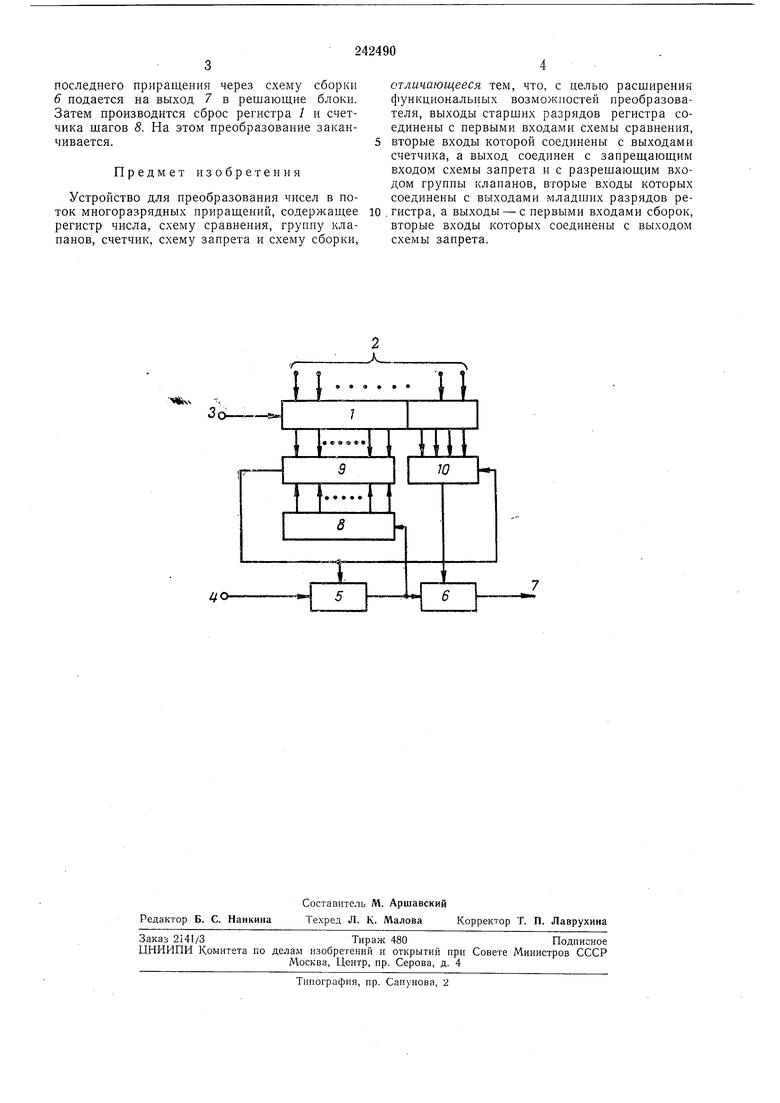

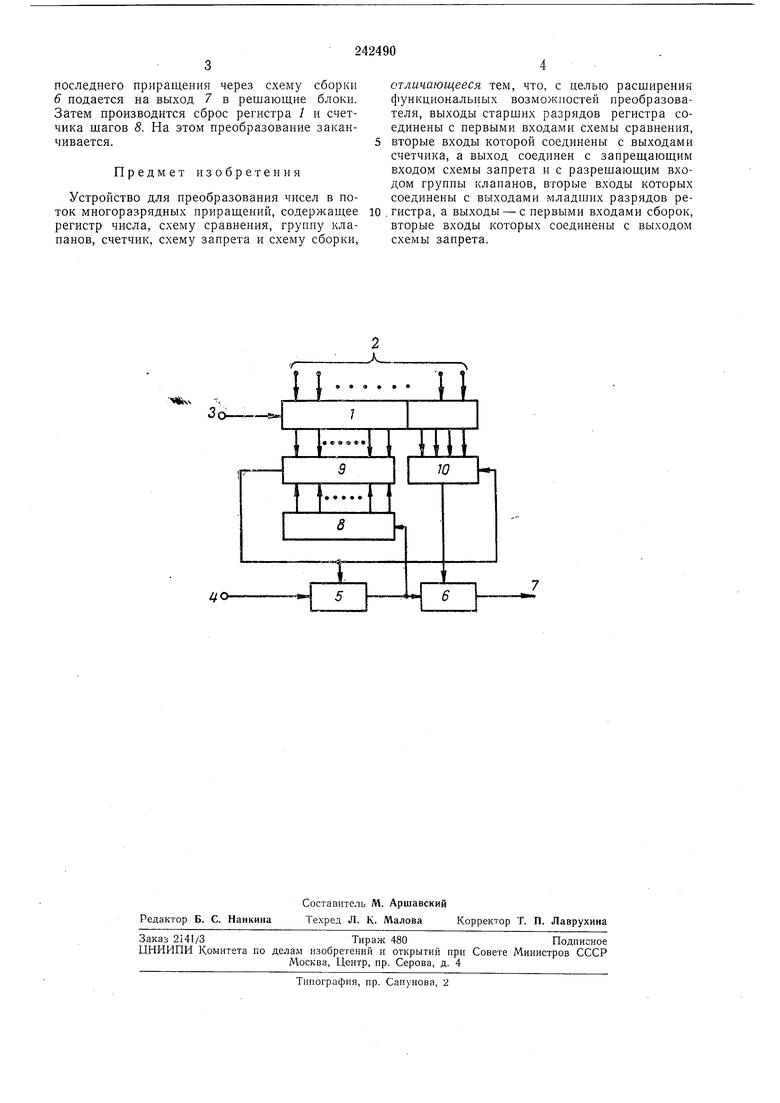

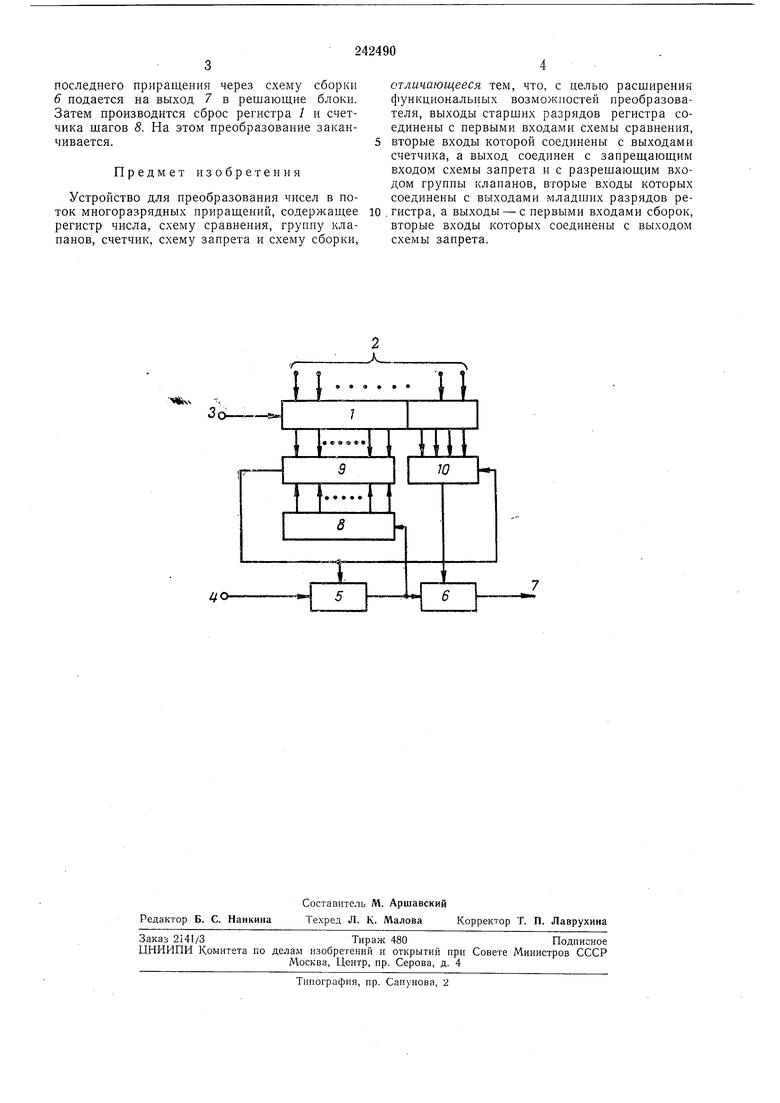

На чертеже приведена блок-схема описываемого устройства.

Оно содержит регистр 1, построенный на статических триггерах, входы 2 для занесения числа из ЦВМ параллельным кодом, вход 3 для занесения числа из ЦВМ последовательным кодом, вход 4 импульсов из устройства управления, схему запрета 5, схему сборки 6, выход 7 преобразователя, счетчик шагов 8,

схему сравнения 9, группу клапанов 10, производящую выборку содержимого младших разрядов регистра 1.

В статический регистр / записывается тразрядное число по входу 2 в параллельном коде или по входу 3 в последовательном коде. В иоследнем случае регистр должен быть сдвигающим. Затем на вход 4 из устройства управления ЦИМ начинают поступать импульсы, следующие в начале каждого шага интегрирования. Эти импульсы через открытую схему запрета 5 и схему сборки 6 поступают на выход 7 в решающие блоки ЦИМ. Каждый импульс соответствует максимальному приращению 2, где п - количество разрядов приращения. Одновременно с выхода схемы запрета 5 эти импульсы поступают на вход (т-п)-разрядного счетчика 8 шагов интегрирования. Содержимое этого счетчика непрерывно сравнивается в схеме сравнения 5 с содержимым старших (т - «) разрядов регистра /, которые содержат целое количество максимальных приращений. В случае равенства двух (т-«)-разрядных чисел на выходе схемы сравнения 9 появляется сигнал окончания выдачи на выход максимальных приращений. Этот сигнал поступает также на разрешающий вход группы п клапанов 10, с помощью которых выбирается код младших п разрядов репоследнего приращения через схему сборки 6 подается на выход 7 в решающие блоки. Затем производится сброс регистра 1 и счетчика шагов 8. На этом преобразование заканчивается.

Предмет изобретения

Устройство для преобразования чисел в поток многоразрядных приращений, содержащее регистр числа, схему сравнения, группу клапанов, счетчик, схему запрета и схему сборки.

отличающееся тем, что, с целью расширения функциональных возможностей преобразователя, выходы старших разрядов регистра соединены с первыми входами схемы сравнения,

вторые входы которой соединены с выходами счетчика, а выход соединен с запрещающим входом схемы запрета и с разрешающим входом группы клапанов, вторые входы которых соединены с выходами младших разрядов регистра, а выходы - с первыми входами сборок, вторые входы которых соединены с выходом схемы запрета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ | 1972 |

|

SU354409A1 |

| Способ уравновешивания цифровых автоматических экстремальных мостов переменного тока и устройство для его осуществления | 1983 |

|

SU1150553A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Устройство для программного управления намоточным оборудованием | 1984 |

|

SU1273879A2 |

| Линейный интерполятор | 1986 |

|

SU1383302A1 |

| Цифровой усреднитель длительности временных интервалов | 1982 |

|

SU1057921A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Устройство для вычисления тангенса | 1984 |

|

SU1187162A1 |

Vfcxv

lieesoj I

П( I

Даты

1969-01-01—Публикация