рои элемент задержки - с первыми входами второго и третьего элементов И, вторые входы которых соединены соответственно с прямым и инверсным выходами второго триггера, первьй и второй входы которого через со ответственно третий и четвертый элементы задержки соединены соответственно с инверсньм выходом первого триггера и выходом второго элемента И, выход генератора импульсов сое динен с вторым входом первого элемента И, выходы второго и третьего элементов И и инверсньй выход первого триггера соединены соответственно с третьим первым и четвертым выходами блока управления, причем блок анализа содержит сумматор, схему сравнения, два элемента НЕ и три сумматора по модулю два, первый и второй входы блока анализа соединены с соответствующими входами схемы 1 2 сравнения, выход которой соединен с первым входом первого сумматора по модулю два и через первьй элемент НЕ - с третьим выходом блока анализа, знаковые разряды первого и второго входов которого соединены соответственно с первыми вторым входами второго сумматора по модулю два, выход которого соединен с вторым входом первого сумматора по модулю два, выход которого соединен с первым входом третьего сумматора по модулю два, второй вход и выход которого соединены соответственно с выходом знака сумматора и входом второго элемента НЕ; выход и вход которого соединены соответственно с вторым и первым выходами блока анализ.а, третий и четвертый входы которого соединены соответственно с первым и вторым входами сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1984 |

|

SU1188750A1 |

| Устройство для вычисления гиперболических функций | 1980 |

|

SU957208A1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ arctg(y/x) | 2015 |

|

RU2595486C1 |

| Арифметическое устройство | 1980 |

|

SU903868A2 |

| Устройство для вычисления функции @ ( @ - @ )/( @ + @ ) | 1982 |

|

SU1076911A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1357951A2 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ТАНГЕНСА, содержащее два сумматоравычитателя, два сдвиговых регистра, блок управления и блок анализа, причем информационные входы первого и второго сумматоров-вычитателей соединены с прямыми выходами соответственно первого и второго сдвиговых регистров, входы управления сдвигом которых соединены с первым выходом блока управления, первый и второй выходы блока анализа соединены с управляющими входами соответственно первого и второго сумматоров-вычитателей, отличающееся тем, что, с целью повышения быстродействия, в него введены четыре группы элементов И, причем вход пуска устройства соединен с входом пуска блока управления и входами сброса первого и второго сумматоров-вычитателей, установочные входы которых соединены с выходами элементов И соответственно первой и второй групп, первые входы которьк соединены соответственно с прямым и инверсным выходами первого сдвигового регистра, установочный вход которого соединен с входом задания переменной устройства и установочным входом второго сдвигового регистра, выходы первого и второго сумматоров-вычитателей соединены соответственно с первым и вторым информационными входами блока анализа и первыми входами элементов И соответственно третьей и четвертой групп, выходы которых соединены с информационными входами соответственно первого и второго сдвиговых регистров, прямые выходы которых соединены соответственно с первым и вторым входами синхронизации сумматоров-вычитателей, k/) вторыми входами элементов И всех групп и выходом готовности устройства, причем блок управления содержит генератор импульсов, два триггера, счетчик, дешифратор нуля, три элемента И, элемент ИЛИ и четыре элемента задержки, вход Пуск блока управления соединен с установочным вхо00 дом счетчика и через первый элемент задержки - с первым входом первого триггера, прямой выход и второй вход S которого соединены соответственно с первым входом первого элемента И . и выходом элемента ИЛИ, первый и второй входы которого соединены соответственно с первым входом первого элемента И и выходом элемента ИЛИ, первьй и второй входы которого соединены соответственно с входом признака перехода блока управления и выходом дешифратора нуля, вход которого соединен с выходом счетчика, счетный вход которого соединен с выходом первого элемента И, вторым оыходом блока управления и через вто

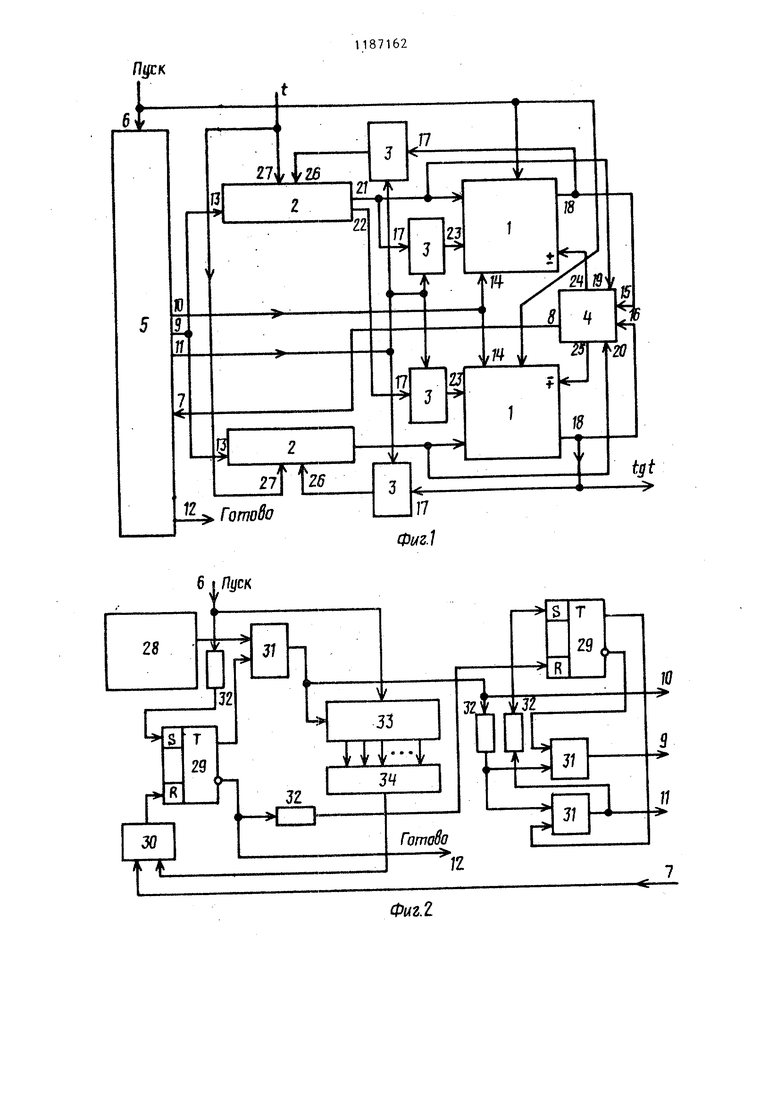

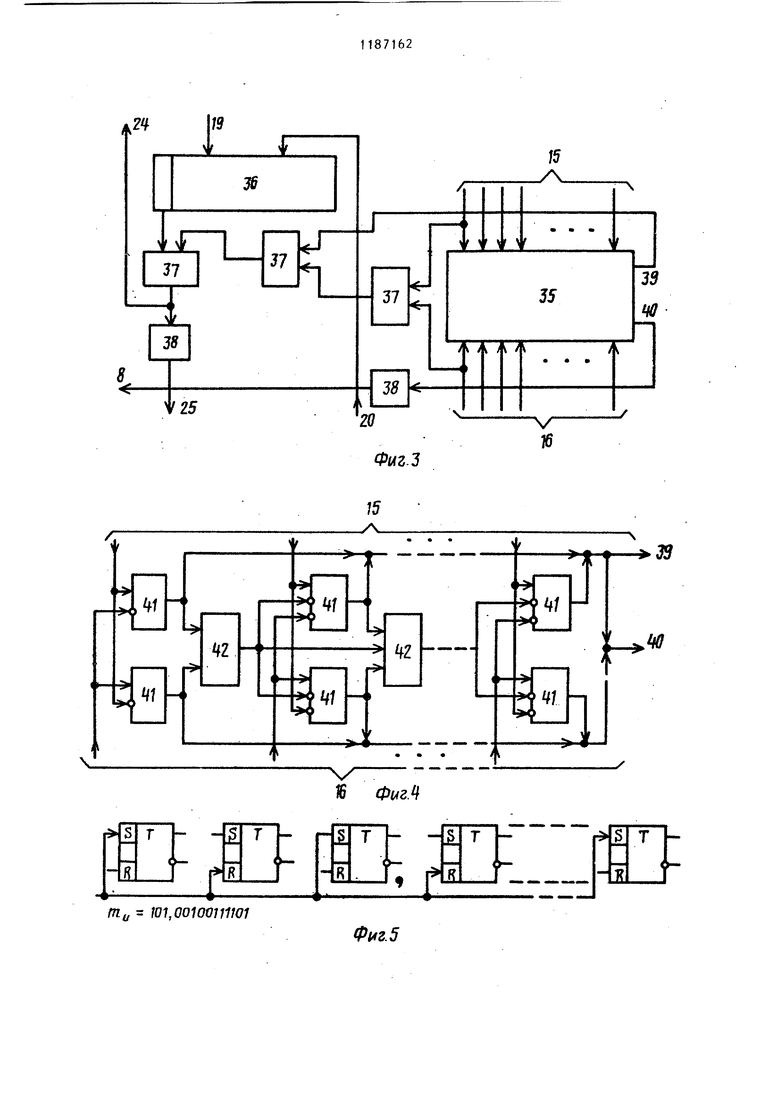

Изобретение относится к вычислительной технике и может использоваться при аппаратном вычислении элементарных функций в цифровых системах предварительной обработки информации . Цель изобретения - повышение быст родействия. На фиг. 1 представлена блок-схема устройства для вычисления тригономет рического тангенса; на фиг. 2 и 3 функциональные схемы блока управления и блока анализа соответственно; на фиг. 4 - схема сравнения; на фиг. 5 и 6 - схема организации цепей сброса сумматоров-вычитателей. Устройство для вычисления тангенса содержит сумматоры-вычитатели 1, сдвигающие регистры 2, группы элементов ИЗ, блок 4 анализа, блок 5 управления, вход 6 пуска, вход 7 бло ка управления, выход 8 блока анализа выходы 9 - 12блока управления, входы 13 сдвиговых регистров, входы 14 сумматоров-вьиитателей, входы 15 и 16 блока анализа, входы 17 элементов И, выходы 18 сумматоров-вычитателей, входы 19 и 20 блока анализа. прямой 21 и инверсный 22 выходы первого сдвигового регистра,.вхоДы 23 сумматоров-вычитателей, выходы 24 и 25 блока анализа, входы 26 и 27 сдвиговых регистров. Блок управления содержит генератор 28 импульсов, триггеры 29, элемент ИЛИ 30, элементы И 31, элементы 32 задержки, счетчик 33 и дешифратор 34.. Блок анализа содержит схему 35 сравнения, сумматор 36, сумматоры 37 по модулю два, элементы НЕ 38, выходы 39 и 40. Схема сравнения содержит элементы И 41 и элементы ИЛИ 42. Все сумматоры-вычитатели 1, комби-, национный сумматор 36, схема 35 срав-, нения, группы элементов И 3, сдвигающие регистры 2 содержат (п+3)-разрядных компонент, где п - число разрядов аргумента t, представленного двоичным числом без знака. Для входной, промежуточных и выходной величин принят масштаб, равный 2, т.е. запятая подразумевается находящейся между п-м и (п+1)-м разрядами (нумерация ведется от младших к старшим). Связи между входом занесения всего устройства (аргумент t) и вторыми входами сдвигаюпщх регистров 2 выполнены п-разряднымй шинами. Причем выполнены эти связи со смещением шин на один разряд в сторону старших разрядов (для первого регистра 2) rt и на два разряда в сторону младших разрядов (для второго регистра 2). При этом во втором регистре 2 в качестве второго входа занесения использованы инверсные разряд ные входы, т.е. содержимое заносится в обратном коде со знаком минус (4 t-2 Связи между прямым 21 и инверсным 22 выхода.ми первого сдвигающего регистра с входами групп элементов И 3 производятся со смещением шин на один разряд в сторону младших разрядов. При смещении шин некоторые из них повисают в воздухе. Если это шины младших разрядов, то они связы ваются с низким, нулевым уровнем (для регистров 2 и первой группы элементов И 3), либо с высоким, еди ничным уровнем (для второй группы элементов И 3). В случае, если это знаковые шины, то они подключаются к знаковым разрядам источника инфор мации. Входы Сброс обоих сумматоров-вычитателей соединены с входами R некоторых (назовем их j-ми) триггеров и с входами S остальных (назовем их i-ми) триггеров их нако пительных регистров. К J-M триггера отнесены все те триггеры первого ил второго сумматоров-вычитателей 1, номера которых совпадают с номерами разрядов двоичного представления в дополнительном коде величин -2,8452 или -0,0426-2 соответ венно разрядов, содержащих нули. Параметр (длительность временной задержки) элемента 32 задержки выбирается равным половине периода следования импульсов от генератора 28. Амплитуда импульсов равна высокому, т.е. единичному уровню, а длительность меньше половины периода следования. При отсутствии импульса на вы ходе генератора - низкий, соответствующий нулю, уровень напряжения. Период следования импульсов генерато ра 28 должен быть не меньшим, чем удвоенное время сложения чисел в сум 11 24 маторе-вычитателе 1 (принимается, что время сдвига содержимого сдвигающих регистров 2 не больше времени сложения сумматоров-вычитателей). Все величины представлены в дополнительном коде. В этом же коде работают все сумматоры. Работа устройства основана .на итерационном алгоритме и ряде вспо- могательных соотношений qj ,sin(Xj., -Yj,,,)sign (U+6); ., -qj.,a)2-J; ; ..Y.YJ-, qj., U2; для ,5, где j 1,2,...,(n+2) - номер итерарации;n разрядность аргумента t (без знака); г - номер итерации (), для которой X.Yr в пределах разрядной сетки, или номер последней итерации. , -2-, .t - 2,8452, t-0,0426. Г+1,если 81§пг|-1,если стоп при . Работа предлагаемого устройства происходит в два этапа: занесение в регистры 2 аргумента и вьтолнение предварительных вычислений величин, участвую(цих в итерациях, и вьшолнение итераций (для вычисления тангенса). Перед началом вычисления триггеры 29 блока 5 управления сброшены в О (это делается в конце предьадущего процесса вычисления тангенса, либо при включении питания). Значе- ние аргумента t(, 7/4) поступает извне через шины занесения на. вход первого и второго сдвигающих регистров 2, куда благодаря особому смещению шин в связях заносятся вели-. чины 2t и С приходом сигнала Пуск (импульс с положительной амплитудой, соответствугацей высокому, единичному уровню) в первый и во второй сумматоры-вычитатели 1 заносятся двоичные величины, равные приближенному (п+3)-разрядному представлению констант -2,8452 и -0,0426-2 ответственно, путем избирательного сброса в О или установки в 1 тех или иных триггеров их накопительных регистров. Затем эти величины поступают с выходов сумматоров-вычи тателей 1 на первый 15 и второй 16 входы блока 4 анализа, который опре деляет, какое из нихбольше. На пер вом 24 и втором 25 выходаз4 этого блока появляются соответственно низкий и высокий уровни, которые, поступив на первый и второй суммато ры-вычитатели 1, переключают их в режим сложения и вычитания соотве ственно. Также одновременно -с приходом сигнала Пуск через первый вход 6 в блок 5 управления этим сигналом в вычитающий счетчик 33 заносится число п+3 (для последующего подсчета числа итераций). . Спустя некоторое время сигнал Пуск, поступая на вход первого триггера 29, устанавливает его в 1, открывая тем самым первый элемент И 31. Очередной импульс от генератора 28 пройдет на второй выход 10 блока 5 и далее на синхровходы 14 сумматоров-вычитателей 1, производя подсуммирование содержимого первого сдвигающего регистра 2 и вы читание содержимого второго соответ ственно к содержимому первого и от содержимого второго сумматоров-вычи тателей 1. Их новые содержимые будут 2.f- 2,8452 и l/4t - 0,0042 Этот же сигнал от генератора 28, поступив на вычитающий счетчик 33, уменьшит его содержимое на единицу, и, пройдя через элемент 32 задержки и через элемент И 31, появится на третьем выходе 11 блока 5 управления. Сигнал с этого выхода являет ся разрешающим на взаимную перезапись с помощью четырех групп элемен тов ИЗ, содержимых сдвигающих регистров с одноименньми сумматорамивычислителями. Причем в сумматорывычитатели 1 засыпается содержимое только первого регистра 2, уменьшен ное в два раза за счет смещения шин в многоразрядных связях между этими узлами. Выход 22 - инверсньй, поэто му во второй сумматор-вычитатель 1 занесется величина - t -2 , в то ж время в первьй сумматор-вычитатель занесется величина t. Выполнение вьмислительного проце са происходит итерациями, т.е. одинаковыми в своей последовательности действиями. Число итераций (п+2){ однако они могут закончиться раньше, если Xf,Yp, в последнем случае число итераций будет равно г. Одна из итераций описьшается следующим образом. Текущие содержимые сумматороввычитателей 1 Xj-i и YJ., и .сдвигающих регистров поступают на входы 15, 16, 19 и 20, соотг ветственно, блока анализа, где они сравниваются с помощью схемы 35 сравнения, комбинационного сумматора 36 и трех сумматоров 37 по модулю два Если содержимые сумматоров-вычитателей равны, на втором выходе 40 схемы 35 сравнения появится сигнал низкого уровня напряжения, который, пройдя через первый элемент НЕ 38, превратится в сигнал высокого уровня и .поступит на третий выход 8 блока 4 анализа. Далее он попадает на второй вход 7 блока 5 управления, где через элемент ИЛИ 30 поступает на вход первого триггера 29 Последний сбрасьшается в О., закрывая дальнейшее поступление сигналов от генератора.28 и подавая с инверсного выхода высокий сигнал на вы-г ход 12 Готово, а через элемент 32 задержки - на вход второго триггера 29, устанавливая его в О и подготавливая блок 5 управления для новых вьиислений тангенса. I Если же содержимые сумматороввычитателей 1 не равны, на выходе 39 схемы 35 Сравнения с помощью элементов И 41 и ИЛИ 42 образуется сигнал высокого уровня, если.код числа, интерпретируемый как число без знака, на первом входе 15 больше, чем на втором 16 Этот сигнал вместе с Сигналами с выхода комбинационного сумматора 36 и с выхода второго сумматора 37 по модулю два, учитьшающего знаки сравниваемых чисел, суммируется с помощью сумматоров 37 по модулю два и поступает на первый 24 и через второй элемент HjE - на второй выход 25 блока 4 анализа. Этот сигнал (на выходе 24) равен 1 Ч 4- 1 .Он управляет режимом работы первого (с выхода 24) и второго (с выхода 25) сумматоров-вычитателей 1. 7 .1 Очередной импульс от генератора 28 проходит через открытый первьй элемент И 31 на второй выход 10 и да лее на синхровход 14 обоих сумматоров-вь1читателей 1. Он разрешает подсуммирование содержимых первого и второго сдвигающих регистров 2 к содержимым одноименных сумматоров-вычитаталей 1 (причем, поскольку один из них работает в режиме вычитания, то к его содержимому происходит подсуммирование содержимого сдвигающего регистра 2 со знаком минус). Этот же импульс, пройдя через эле мент 32 задержки, поступает через элемент И 31, открытый высоким сигна лом с инверсного выхода второго триг гера 29, на первый выход 9 блока 5 управления и далее на входы 13 сдвига обоих сдвигающих регистров 2, Этим самым содержимое обоих регистров 2 уменьшается вдвое. Заметим, что сдвиг - арифметический, т.е. знаковый разряд не сдвигается, а соседний со знаковым разряд при сдвиге повторяет его значение. Таким образом, новые содержимые регистров 2 приготавливаются для следующей итерации, если она состоится. Каждая итерация приводит к уменьшению содержимого вычитающего счетчика 33. В тот момент, когда оно ста нет равным нулю, сработает дешифратор 34 нуля, на выходе которого высо кий сигнал поступит через эле- . мент ИЛИ 30, на вход первого триггера 29, сбросив его в нуль. Это приводит к тому, что прекратится подача импульсов от генератора 28, так как первый элемент И 31 закроется. Одновременно на выход 12 поступит сигнал Готово% так как ите ации эакончй 2лись и результат готов. Значение тангенса находится на выходах п младших разрядов в виде п-разрядного двоичного числа без знака в масштабе 2. После сигнала Готово второй триггер также сбросится в О с помощью элемента 32 задержки, подготавливая блок 5 управления к очеред- ному вычислению тангенса. Остановимся подробнее на работе схемы 35 сравнения. Если цифры в старших разрядах равны, то сравнение выполняется для следующих разрядов, более младших и т.д. Если какие-то сравниваемые разряды не равны, то сигнал об этом передается в виде высокогб уровня, если на первом входе 15 . единица, а на втором 16 нуль, на первьш выход 39 схемы 35 сравнения. Одновременно сигнал 1 с первого элемента 41 данного разряда, пройдя через элемент ИЛИ 42 на соседний и последующие более младшие разряды, запрещает сравнение в остальных разрядах. Если числа равны во всех разрядах, на втором вьпсоде 40 появится сигнал в виде низкого уровня напряжения. В остальных случаях на выходе 40 - высокий уровень Напряжения, подаваемьй через монтажные ИЛИ с выходов либо первых, либо вторых элементов 41. Максимальная относительная погрешность вычисления тангенса зависит от разрядности пив лучшем случае (при ) составляет «у 0,1%. Быстродействие обратно пропорционально разрядности п. Среднее время вьиисления одного значения тангенса равно 2. n.-tfsj (tp - время сложения на сумматоре-вычитателе 1).

0

§

3Ti

ГопюЗо

/7

С

23

Я

24

15

К:.

8

25

M/W ь

23

Г7

1Я

/

tgt

17

Фиг2

Фмг.Л

/

- р

2

f

f

9И1

t

HI

м

Z

/

16 ф1АгЦ

m, Ю1,001001W01

S.

Фиг. 5

3;;;; ;

С

Щ inwwffoo

fpuz:6

| Цифровой функциональный преобразователь | 1976 |

|

SU744595A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-23—Публикация

1984-04-24—Подача