Изобретение относится к области электросвязи и может быть использовано в устройствах многоканальной связи и в аппаратуре обработки результатов измерений.

В известных селекторах информационных каналов связи, содержаш;их счетчики импульсов и матрицу, каждый из локальных коммутаторов имеет отдельный счетчик.

Целью настоящего изобретения являлось сокр-ащение числа счетчиков до одного, независимо от числа несинфазных каналов.

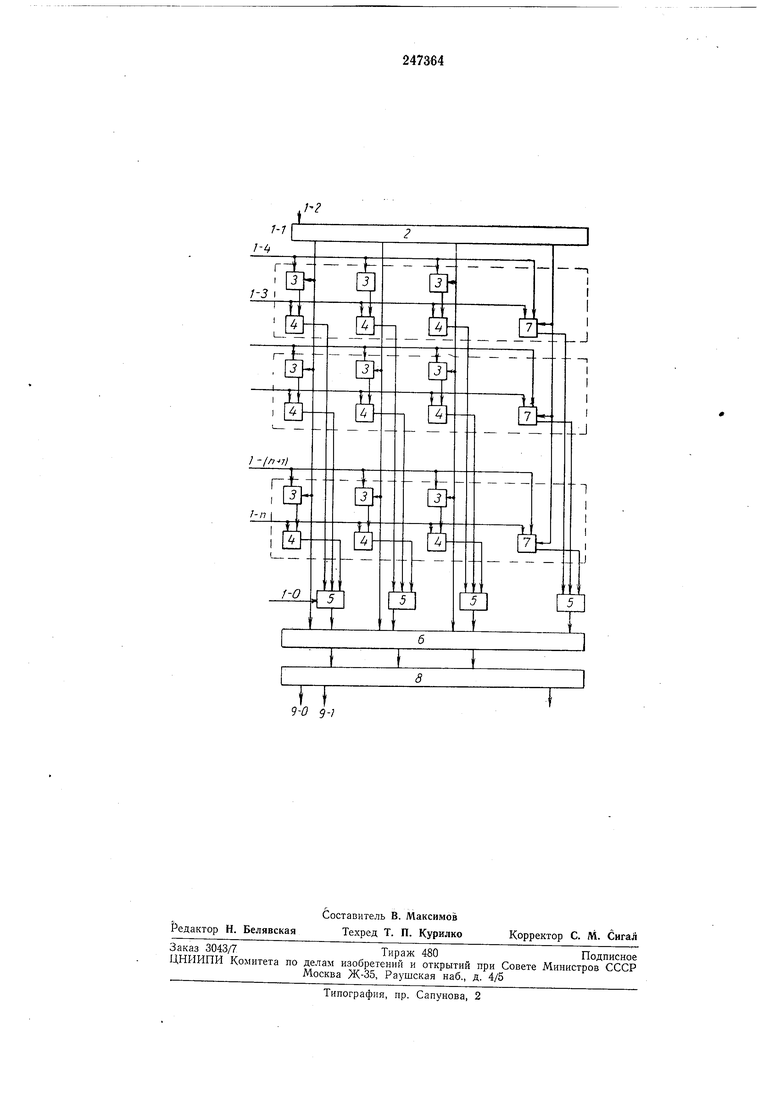

Поставленная цель достигается за счет того, что выходы счетчика для каждого из разрядов непосредственно, а также через последовательно соединенные цепочки из схем «И и ячеек памяти, объединенных по выходам схемами «ИЛИ, соединены с соответствующими входами сумматора, включенного на входе матрицы.

Блок-схема селектора информационных каналов связи приведена на чертеже.

Селектор информационных каналов связи работает от нескольких последовательностей импульсов, получаемых с выхода специальной аппаратуры, не показанной на чертеже. На счетный вход /-/ счетчика 2 поступают импульсы первой последовательности, которая принимается за основную. Синхроимпульс этой последовательности поступает на вход 1-2 и устанавливает счетчик 2 в исходное

состояние. На вход 1-3 поступают импульсы второй последовательности, а ее синхроимпульсы подаются на вход 1-4 и т. д. На вход /-п поступают импульсы п-ок последовательности, а ее синхроимпульсы подаются на вход 1 - (п+1). Все перечисленные последовательности импульсов синхронны, но не синфазны между собой. Во времени каждая последовательность импульсов привязана к своим синхроимпульсам, периоды следования которых одинаковы. В результате воздействия импульсов, поступающих на вход /-/ счетчика 2 последовательно во времени, получают текущие значения номеров каналов, определяемых

этой последовательностью. После выделения всех номеров каналов этой последовательности счетчик устанавливается на нуль и т. д. Моменты совпадения некоторых положений счетчика 2 и синхроимпульсов всех остальных,

кроме первой, последовательностей фиксируются через схемы «И 3 ячейками памяти 4. Запись чисел в ячейках памяти 4 осуществляется последовательно но мере прохождения синхроимпульсов. За один период синхроимпульсов первой последовательности в ячейках памяти 4 запишется столько чисел, сколько мы имеем последовательностей без первой. Эти числа будут иметь значения от нуля до максимальной емкости счетчика 2. Каждое из

синхронизации. Числа, запис-анные в ячейках памяти 4, являются эквивалентом расстояния всех синхроимнульсов относительно синхроимпульсов первой последовательности. При каждом положении счетчика 2 на входы 1-3, 1-п и им соответствующие последовательно во времени подаются импульсы, которые определяют свои каналы. После прохождения импульса через последний вход 1-п счетчик 2 изменяет свое состояние на единицу. Затем последовательно подаются импульсы на входы /-3, 1-п и т. д.

Числа, записанные в ячейках памяти, считываются без стирания импульсами, поступающими на входы 1-3, 1-п и др., и подаются через схемы «ИЛИ 5 на сумматор 6. В сумматоре 6 производится вычитание чисел. Вычитаются числа, записанные в ячейках памяти 4, из чисел, записанных в данный момент в счетчике 2. Вычитание производится по абсолютной величине носледовательно по мере поступления импульсов опроса на входы 1-3, 1-п и др.

Числа в счетчике могут меняться от нуля до его полной емкости. Отставание фазы синхроимпульсов может достигать такой же величины. Сдвиг между этими числами образует критическую ситуацию. Действительно, числа в ячейках памяти 4 и в счетчике 2 могут оказаться больше или меньше друг относительно друга. Если число в счетчике 2 будет больше, чем число, записанное в ячейках 4 памяти, то сумматор 6, произведя вычитание из первого -числа второго, верно онределит номер импульса и канала. В противоположном случае сумматор может выдать ошибочный результат. Для устранения этого для каждой последовательности введены дополнительные ячейки памяти 7. Эти ячейки предназначены для фиктивного увеличения емкости счетчика 2 на один разряд. В дополнительные ячейки памяти 7 записывается единица нри установке счетчика 2 в нулевое положение. Информация из указанных ячеек памяти 7 считывает так же, как и с других ячеек памяти 4. Однако сброс единицы из

дополнительных ячеек памяти 7 производится синхроимпульсами той последовательности, к которой относится ячейка. Таким образом, числа в счетчике 2 могут теперь иметь в два раза больше значений, чем числа, записанные в ячейках памяти 4, не считая дополнительных ячеек памяти 7. В результате на входы сумматора 6 всегда будет поступать уменьшаемое, не меньшее, чем вычитаемое, и, следовательно, результат вычитания при любых числах,будет верным.

Полученные сумматором числа преобразуются в данной матрице S и в единичном коде поступают на ее выходы. На выходе матрицы

8 номера выделенных каналов или импульсов сдвинуты относительно номеров первой последовательности на единицу. Это означает, что на нулевом выходе 9-О матрицы 8 окажутся первые каналы всех последовательностей,

кроме первой; на первом выходе 9-1 матрицы 8 окажутся вторые каналы всех последовательностей, кроме первой и т. д. Номера каналов первой последовательности и номера выходов матрицы 8 совпадают. Однако при

необходимости сдвиг первой последовательности относительно всех других последовательностей можно ликвидировать, например, путем подачи на схему «ИЛИ 5 младшего разряда счетчика 2 импульсов последовательности со входа /-0.

Предмет изобретения

Селектор информационных каналов связи, содержащий счетчики импульсов и матрицу, отличающийся тем, что, с целью уменьшения количества счетчиков импульсов при выделении каналов из я несинфазных групп каналов,

выходы счетчика для каждого из разрядов неносредственно, а также через последовательные цепочки из схем «И и ячеек памяти, объединенных по выходам схемами «ИЛИ, соединены с соответствующими входами сумматора, включенного на входе указанной матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755293A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1661788A1 |

| Линейный аппроксиматор | 1983 |

|

SU1157548A1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1651293A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| Устройство интерполяции для отображения графической информации | 1988 |

|

SU1525717A1 |

Даты

1969-01-01—Публикация