Изобретение относится к области вычислительной техники и может быть использовано при конструировании настольных вычислительных машин.

Известны электронные клавишные вычислительные машины, выполняюш,ие арифметические операции, вычисление элементарных функций, различные формульные вычисления, содержащие запоминающее устройство, устройство управления арифметическими операциями, сумматор, устройство управления передачей информации, блок режимов и устро11ство ввода-вывода.

Недостаток известных мащин - низшая эффективность использования их.

Предлагаемая машина отличается тем. что она содержит блок синхронно-символьной обработки порядков, входы которого соединены с устройством ввода, с запоминающим устройством п с устройством управления арнфмстически.ми онерациями, а выходы подключены к устройству управления арифметическими онерациями и через устройство управления передачей информации - к запоминающему устройству.

Это позволяет упростить мащину и повысить ее быстродействие и производительность.

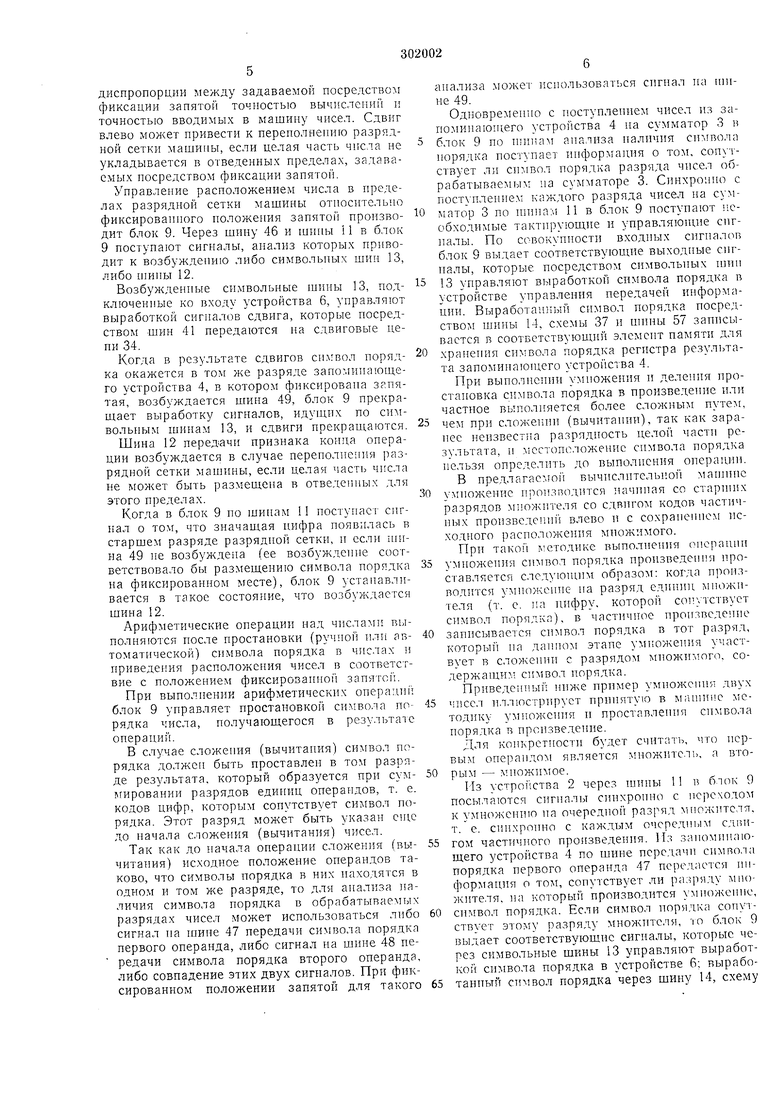

На фиг. 1 изображена блок-схема предлагаемой вычислительной мащины; на фиг. 2 - схема, иллюстрирующая связи запоминающего устройства с блоком синхронно-символьной обработки норядков и с другими устройствами мащнны. Вычислительная машина содержит устройство 1 ввода, устройство 2 управления арифметическими операциями, сумматор 3, запоминающее устройство (ЗУ) 4; шины 5 занесения мантиссы и норядков, устройство 6 управления нередачей информации, устройство 7

вывода, блок 8 режимов, блок 9 синхронносимвольной обработки порядков, шины 10 анализа наличия символа порядка, шины 11 синхронного унравления, шину 12 передачи признака конца операции, символьные шины 13,

шину 14 простаповки символа порядка, шины 15 коммутации, шину 16 управления занесением символа порядка, шины 17-24 обмена информацией, шины 25 н 26 унравления блоком режимов, шины 27 и 28 управления

устройством вывода, шины 29 режима, шины 30 пересылок, регистровую часть 31 ЗУ 4, блок 32 местного управления, вентили 33 пересылок, сдвиговые цепи 34, схему 35 занесения мантиссы числа, схему 36 занесения символа

порядка, схему 37 простаповки символа порядка, схе.му 38 считывания символа норядка, арифметические цепи 39, шины 40 управления пересылками, шины 41 управления сдвигами, шину 42 блокировки занесения мантиссы, коки занесения символа норядка, тину 45 занесении символа норядка, типу 46 пе)едачн символа норядка нз входного регистра, типу 47 неродачн снмво.ча порядка нсрвого онеранда, niKHV 48 нередачи символа норядка второго ог1е)а11да, гнииу 49 фиксированного положения, jHiiHy 50 передачи сн.вола норядка резу;11.та1а, кодовые HIHIIU 51 и 52 нересьг.чок, кодовые НН1НЫ 53 и 54 сдвига, кодовые нмннл 55 занисн, шины 56 и 57 записи символа порядка, шипы 58 считывания символа норядка, кодовые шииы 59 и 60 суммирования.

Предлагаемая вычислителвная машина работает следующим образом.

При нажатии на клавиши устройства в этом устройстве вырабатываются коды, соответствуюи ше - числам, знакам, норядкам и командам.

Порядок вводится естествениыл образом посредством нажатия иа клавишу десятично запятой после иабора разряда единин, числа. При нажатии иа клавиигу десятичио занято из устройства I з блок 9 си 1хропио-символьиой обработки иорядков через шииу 16 нередается уиравля ощий сигнал (1ризнак 1ажатия на клавишу десятично за 1ятой). Блок 9 выдает соответству 0 цую и форма и ю через символьные 13 в усаройство 6.

Через 44 передается , котор Й является раз )еп1аю цим дл символа порядка и запоми1 а О,ее ycTpofic 4 3 устройства 1 носредс1 ом 45 схемы 36.

Символ порядка, занисан ;ый иа онределе иое место в оиределе 1ый регистр запомя 1а о цего устройства 4, приводит к возбуждени о из 10 анализа 1аличия символа порядка, а -- ередачи символа порядка из входиого регистра 46, по которой в блок 9 поступает информация о том, что в чиеле проставле символ орядка. Блок сиихроиио-символь 1ой обработки порядков устанавливается в такое состояние, что при повторном пажатин па клавишу десятично запятой сигпал, приходящий из устройства i в блок 9 по 16, пе вызывает возбуждения символьпых шин 13, и следовательно, не появляется сигнал иа шиие 44 и повтор юй записи символа порядка не происходит.

Такое выполнение запесепия символа порядка и дальнейшей обработки числа с уче1-ом его порядка реализуется при спецпальпой оргапиза дии регистровой части 31 запомипаюшего устройства 4.

Каждая разрядная ячейка в регистровой части 31 состоит из места для размещения кода разряда и элемента памяти для символа порядка.

Каждое место для размеи1еиия кода орядка связано двухсторон 1ими связями с сумматором 3 посредством кодовых ши1 59 п 60, арифметических цепей 39 и шии 23 п 24, а также связано с устройством ввода посредством кодовых П1ИН 55, схемы 35 ма тиссы числа и кодовых 43.

Кроме того, в 3anoMH aioHiero устрОЙС Ва 4 ie . 1 Нфор., iO 1 в Т .

пли другую сторо у, вынол 1яемый в ,

устройстве 4 по , ) из

устройства 6 через 41 сдв говые , 34.

1;СЛ ОЛОЛ. :ia ISITO l )аНО i еKOjopo.M разряде разряд 10 1 сетк ), го

в случае, когда в этом разряд за 1исыва отся единицы вводимого числа (т. е. пифра и порядка), возбуждается одна из 10, а имеипо 49 фикеироваииого оложенг1я; блок 9 выдает соответству 01цую информа 1ию,

и через посре.дство 13, устройства )Л1равле ия ередаче | ,ии 42 блокируется за1 есение числа в .за омииающее устройство 4, ocyniecTвляемое из устройства ввода но кодов 5 м 43.

Вводимое число приводится в такое расноложеиие от 1осптель 1о разряд ой сетки , что символ порядка в ne (числе) оказывается в том разряде разрядной , в кочором фиксирова а запятая.

При вводе в ,елых чисел порядка, как правило, е за осптся. Поэтому он долже ав- оматическ 1 роставлен при перехо.те к онера ий. Это

зиачит, что анализ по15яд| а в и ростапо1)Ка символа порядка , случае его ОТСУТС1ВПЯ р()и) ДО

ача;1а собстве 1(; ар}1ф.ет1 ческих onepai i i.

Э1у выполняет блок 9 СИ ХрО ПОсимво.тьпой обработки порядков.

Совокуп ость , поступа10П,пх через ины и и через нишу 46, устанавливает сое1ояпие блока 9 такпм oбpaзo, что символ прядка записа во регистр запомииа он1его устройства 4, то повтор 1ой его в этот регистр ie производится; если же символ порядка е , то в блоке 9 вырабатыва отся спе и-1аль ые сигналы, которые по спмБОЛьп з м 13 поступа от в

устройство 6 управлеппя передачей И форл1ации. При этo. уетройство 6 вырабатывает символ порядка, который записывается к запоми 1а 0 дее устройство 4 через 14, схему 37 и шииу 57 в оди из элемеитов памяти

для храпения символа иорядка, а в тот, который соответствует младше.му разряду входного регистра. Любые преобразования информации иосле этого вь полпя отся ад числом, которому сопутствует символ норядка.

При работе с фиксирова иой запятой кроме простановки символа порядка в числе еобхоД - мо расположп чпсло в разрЯД 0 сетке .

Если порядка расположе ie к же орядке, в котором фиксирова1 а запятая, то число должно быть сдвинуто вправо или влево до такого толоже ия, чтобы символ порядка аходился в тол же разряде. Сдвиг вправо может привестп к отере дробной части числа, что свидетельствует о

диспропорции между задаваемой посредством фиксации запятой точностью выч1 слеиий и точностью вводимых в машину чнсел. Сдвиг влево может привести к переполнению разрядной сетки машины, если целая часть числа не укладывается в отведенных пределах, задаваемых посредством фиксации запятой.

Управление расположением числа в пределах разрядной сетки машины относительпо фиксированного положения запятой пронзводит блок 9. Через шипу 46 и шины i 1 в блок 9 поступают сигналы, анализ которых приводит к возбуждепию либо символьных шин 13, либо ншны 12.

Возбужденные снмвольные шины 13, подключенные ко входу устройства 6, управляют выработкой сигналов сдвига, которые носредством шин 41 передаются па сдвиговые цени 34.

Когда в результате сдвигов снмвол порядка окажется в том же разряде запоминающего устройства 4, в котором фиксирована занятая, возбуждается шина 49, блок 9 прекращает выработку сигналов, идущих по символьным шинам 13, и сдвиги прекращаются.

Шина 12 передачи признака конца операции возбуждается в случае переполнения разрядной сетки машины, если целая часть числа не может быть размещена в отведенных для этого пределах.

Когда в блок 9 по шипам 11 поступасг сигнал о том, что значащая цифра ноявилась в старшем разряде разрядной сетки, н если пшна 49 не возбуждена (ее возбуждение соответствовало бы размещению символа порядка на фиксированном месте), блок 9 устанавливается в такое состояние, что возбуждается шина 12.

Арифметические операции над чнслалп выполняются после простановки (ручной или автоматнческой) символа порядка в числах н приведения расположения чисел в соответствие с положением фиксированной запятой.

При выполнении арифметических оиерашн блок 9 управляет простановкой символа порядка числа, получающегося в результате операций.

В случае сложеиия (вычитания) символ порядка должен быть проставлен в том разряде результата, который образуется при суммировании разрядов единиц операндов, т. е. кодов цифр, которым сопутствует символ порядка. Этот разряд может быть указан еще до пачала сложения (вычитания) чисел.

Так как до начала операции сложения (вычитатшя) исходное положение операндов таково, что символы норядка в них находятся в одном и том же разряде, то для анализа наличия символа порядка в обрабатываемых разрядах чисел может использоваться либо сигнал па шине 47 передачи символа порядка первого операнда, либо сигнал на шине 48 передачи символа порядка второго операнда, либо совпадение этих двух сигналов. При фиксированном положении запятой для такого

анализа .может использоваться сигнал па HIHне 49.

Одновременно с поступлением чисел из заномицаюп1его устройства 4 на сумматор 3 в блок 9 по тпинам анализа наличия си гвола порядка поступает информация о том, сопутствует ли спмвол порядка разряда чнсел обрабатываемым на сумматоре 3. Синхронно с поступлением каждого разряда чисел на сумматор 3 по пи1над1 11 в блок 9 поступают необходимые тактирующие и управляющне сигналы. По совокуппости входных сигналов блок 9 выдает соответствующие выходные сигналы, которые посредством символьпых ншн 13 управляют выработкой символа порядка в устройстве управления передачей информации. Выработанный символ порядка посредством шины 14, схемы 37 н тины 57 записывается в соответствующий элемепт памяти для хранения порядка регистра результата запоминатотцего устро11ства 4.

При выполнении умножения н деления простановка силшола порядка в произведение или частное выполняется более сложным путем, чем при сложении (вычитапии), так как зарапее неизвестна разрядность целой части результата, н местоположенне символа норядка нельзя определить до выполнения операции.

В предлагае:-1ой вычнслительной манщпе умножение производится начиная со старншх разрядов множителя со сдвиголг кодов частичных нронзведеин влево и с сохранением нсходного расположения множимого.

При такой методике выполнения онсрацнн умножения символ порядка пропзведенпя проставляется следуюпи1м образом: когда производится умпоженпе на разряд е.диниц множителя (т. е. па цифру, которой сопутствует символ норядка), в частичное нр01гзведенне записывается символ порядка в тот разряд, который на данном этапе умножения участвует в сложепин с разрядом множилюго, содержапдим символ норядка.

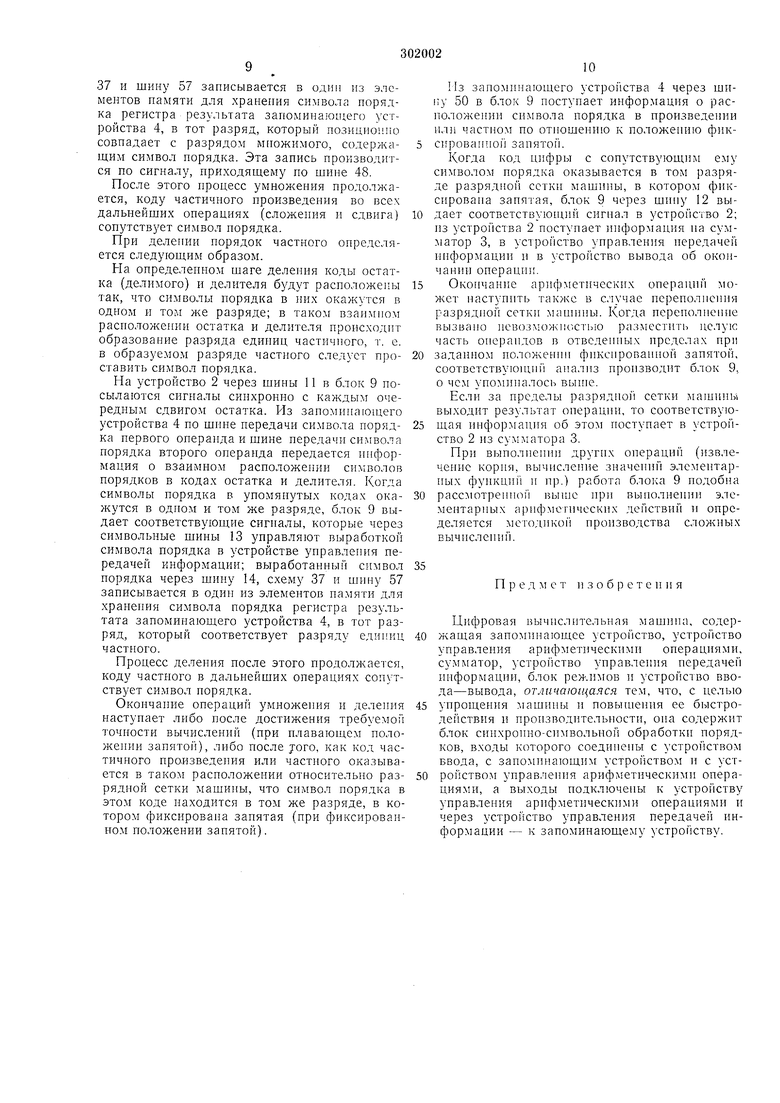

Приведенный ниже пример умножения двух чнсел иллюстрирует припятую в маншие ieтодику умножения и проставлепня снмвола норядка в нронзведенпе.

Для конкретности будет считать, что нсрвым операндом является множитель, а вторым - множимое.

Из устройства 2 через шины 11 в блок 9 посылаются сигналы синхронно с переходом к умножению па очередной разряд множителя, т. е. синхронно с каждым очередным сднигом частичного произведения. Из запоминающего устройства 4 по шипе передачи символа порядка первого операнда 47 передастся информация о том, сопутствует ли разряду множителя, па который производится умножеппе, символ порядка. Если символ порядка сопутствует этому разряду множителя, то блок 9 выдает соответствующие сигналы, которые через символьные щины 13 управляют выработкой символа порядка в устройстве 6; выработанпый стпшол порядка через щипу 14, схему

Разряд

множителя,

на который

производится

умножение

11 1, 1

множитель 2 2, 2 2 множимое

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО для ПЕРЕРАБОТКИ ЧИСЛОВОЙ И БУКВЕННОЙ ИНФОРМАЦИИ | 1969 |

|

SU255656A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| ЭЛЕКТРОННАЯ КЛАВИШНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1973 |

|

SU395837A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ УМНОЖЕНИЕМ И ДЕЛЕНИЕМ | 1973 |

|

SU368601A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1968 |

|

SU209032A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| Арифметическое устройство | 1978 |

|

SU711570A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

О 2 4 6 i 8, 6

частичное произведение 1

частичное произведение 2

частичное произведение 3

результат

37 и шину 5 записывается в одни из элементов памяти для храпения символа порядка регистра результата запоминающего устройства 4, в тот разряд, который позициоипо совпадает с разрядом множимого, содержащим символ порядка. Эта запись производится по сигналу, приходящему по шине 48.

После этого нроцесс умножения продолжается, коду частичного произведения во всех дальнейших операциях (сложения и сдвига) сопутствует символ порядка.

При делении порядок частного определяется следующим образом.

Па определенном шаге деления коды остатка (делимого) и делителя будут расноложеиы так, что символы порядка в них окажутся в одном и том же разряде; в таком взаимном расположении остатка и делителя происходит образование разряда единиц частичного, т. е. в образуемом разряде частного следует проставить сн.мвол порядка.

На устройство 2 через шины 11 в блок 9 посылаются сигналы синхронно с каждым очередным сдвигом остатка. Из запомннающего устройства 4 но шнне передачи символа порядка первого операпда н шине передачи символа порядка второго онеранда передается нпформация о взаимном расположении символов порядков в кодах остатка и делителя. Когда символы порядка в упомянутых кодах окажутся в одном и том же разряде, блок 9 выдает соответствующие сигиалы, которые через символьные щины 13 управляют выработкой символа порядка в устройстве управления передачей информации; выработанный символ порядка через шину 14, схему 37 н шину 57 записывается в один из элементов намяти для хранения символа порядка регистра результата запоминающего устройства 4, в тот разряд, который соответствует разряду единиц частного.

Процесс деления после этого продолжается, коду частного в дальнейших операциях сопутствует си.мвол норядка.

Окончание операций умиоження и деления наступает либо носите достижения требуемой точности вычислений (при плавающем положении запятой), лнбо после joro, как код частичного нро-нзведения или частного оказывается в таком расположении относительно разрядной сетки машины, что символ порядка в этом коде находится в том же разряде, в котором фиксирована запятая (при фиксированно.м положении занятой).

10

Из запоминающего устройства 4 через шину 50 в блок 9 ностунает информация о расположении символа порядка в произведении илн частном по отпошепию к полол ению фнксированной занятой.

Когда код цифры с сопутствующим ему символом порядка оказывается в том разряде разрядной сеткп машины, в котором фиксирована запятая, блок 9 через щину 12 выдает соответствуюн ий сигнал в устройство 2; нз устройства 2 поступает информация на сумматор 3, в устройство управления передачей ннформацин и в устройство вывода об окончании оиеранни.

Окончание арифметических операций может наступить также в случае нереполнепия разрядпой сетки машины. Когда иеренолнепие вызвано невозможностью разместнть целую часть онерандоБ в отведенных пределах при

заданном положенун фнкснрованной запятой, соответствующнй анализ пронзводнт блок 9, о чем уноминалось выше.

Если за нределы разрядиой сетки машины выходит результат операцни, то соответствующая информация об этом поступает в устройство 2 из сумматора 3.

При вынолпенни другнх операций (извлечеиие корпя, вычисление значений элементарных функций и пр.) работа блока 9 подобна

расс: 1отренной выше при вьиюлнении элементарных арнфмегическпх действий и определяется методикой производства сложиых вычислепий.

35

П р е д м е т н з о б р е т е п п я

Цифровая вычислительная машина, содержащая заноминающее устройство, устройство управления арифметическими операцпями, сумматор, устройство управления передачей ииформацнн, блок режимов н устройство ввода-вывода, отличающаяся тем, что, с целью унрощения машины и иовы нення ее быстродействия и производительности, она содержит блок синхронно-снмвольной обработки порядков, входы которого соединены с устройством ввода, с заноминающим устройством н с устройством унравлення арифметическими операциями, а выходы подключены к устройству управления арифметическими операциями и через устройство управления передачей информации - к запоминающему устройству.

Авторы

Даты

1971-01-01—Публикация