Изобретение предназначено для использования в устройствах автоматики и вычислительной техники.

Известные счетчики требуют значительного дополнительного оборудования для контроля счета и дешифрации.

Предлагаемая схема состоит из минимального числа однотипных элементов, работа ощих в одинаковых режимах. При этом каждая однократная ошибка счета обнаруживается.

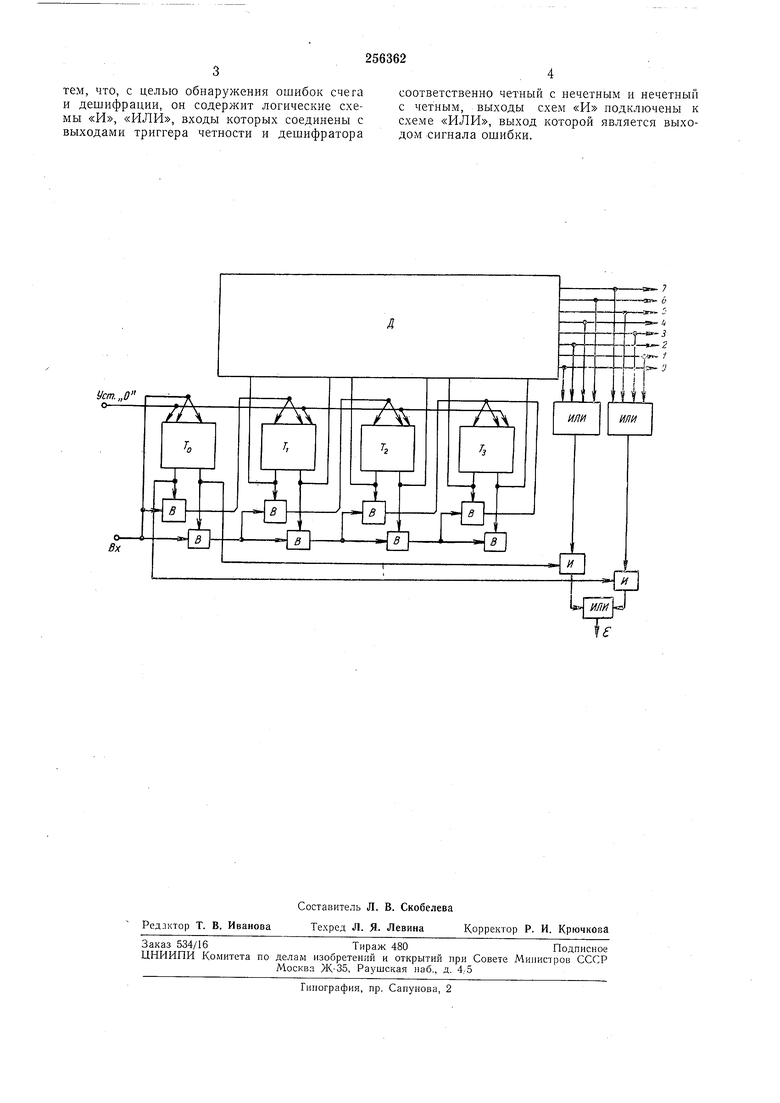

Счетчик содержит логические схемы , «ИЛИ, входы которых соединены с выходами триггера четкости и дешифратора соответственно четный с нечетным и нечетный с четным. Выходы схем «И подключены к схеме «ИЛИ, выход которой является выходом сигнала ошибки.

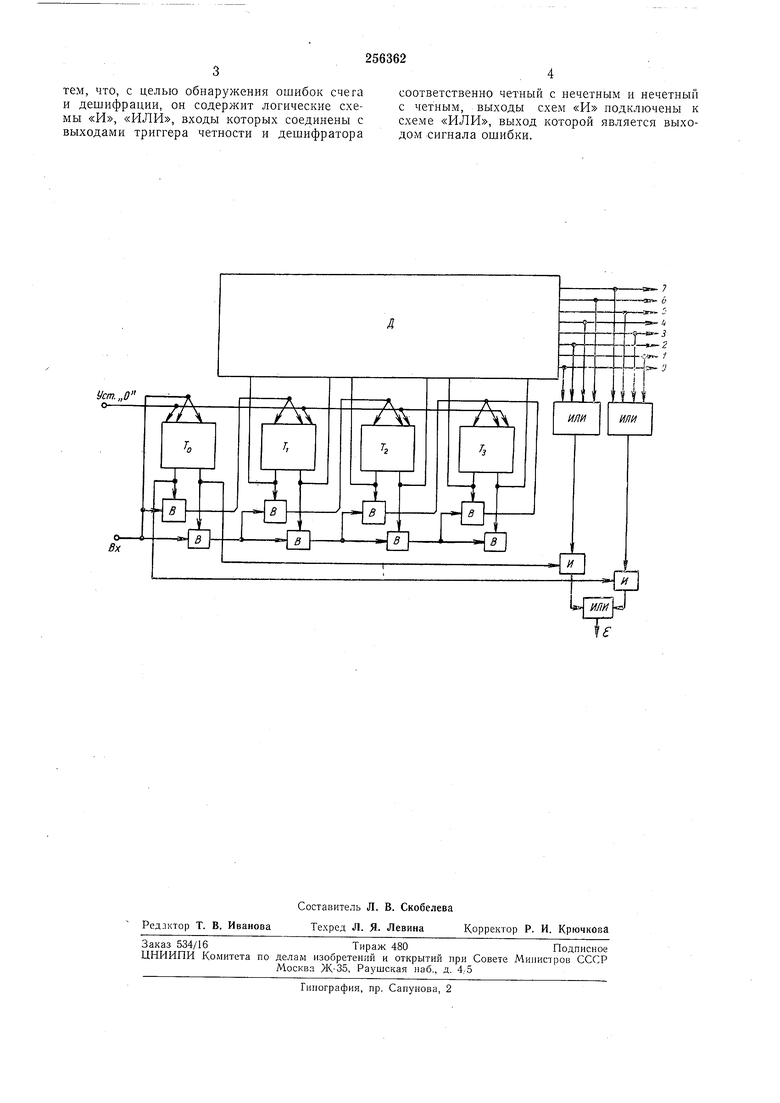

На чертеже изображена схема предлагаемого прибора.

Здесь TI, Г,, Тз - счетные триггерные разряды; Го - триггер четносги; В - вентили; Д - дешифратор; «И - схемы совпадения; «ИЛИ - схемы сборки импульсов.

Счетчик работает следуюш.им образом.

Дополнительный триггер осуш,ествляет начальный сдвиг четных входных импульсов на полпериода низшего разряда Т счетчика. Каждый разряд счетчика в процессе работы чередует поступаюшие на его вход четные и

нечетные импульсы. Нечетные импульсы поступают на вход следуюшего разряда, четные приходят на вход последуюших разрядов. Таким образом, каждый последующий разряд переключается только от нечетного импульса предыдущего. Дополнительный триггер переключается каждым входным импульсом и чередует их также, как и счетные триггеры. Нечетные импульсы переключают первый разряд, четные - остальные .последующие. Эта особенность схемы используется для преобразования импульсов в циклический код и для обнаружения ошибок счета.

Обнаружение ошибок счета осуществляется на выходе схемы.

Сигналы с четных выходов дешифратора поступают на совпадение с нечетными входными импульсами, сигналы с нечетных выходов дешифратора - с четными входными импульсами. При сбое, когда от четного входного импульса выдается сигнал с нечетного выхода дешифратора или от нечетного импульс-а - четный сигнал, соответствующая схема совпадения выдает на общий выход сигнал ошибки счета.

Предмет изобретения

тем, что, с целью обнаружения ошибок счета, и дешифрации, он содержит логические схемы «И, «ИЛИ, входы которых соединены с выходами триггера четности и дешифратора

соответственно четный с нечетным и нечетный с четным, выходы схем «И подключены к схеме «ИЛИ, выход которой является выходом сигнала ошибки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования и декодирования последовательного кода с коррекцией одиночных ошибок | 1976 |

|

SU732877A1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ | 1990 |

|

RU2022469C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КОДОВОГО ЗАМКА | 2003 |

|

RU2247205C1 |

| Й СЧЕТЧИК В КОДЕ ГРЕЯ | 1965 |

|

SU167365A1 |

| Пересчетное устройство с контролем ошибок | 1981 |

|

SU974591A1 |

| Регулируемый преобразователь переменного напряжения в переменное | 1985 |

|

SU1307515A1 |

| ЮЗНАВ | 1973 |

|

SU378933A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| Устройство для контроля четности двоичного последовательного кода | 1989 |

|

SU1702373A1 |

| Устройство для исправления ошибок при итеративном кодировании | 1977 |

|

SU680061A2 |

ifcm.,,0 о

Даты

1969-01-01—Публикация