Предложенный сумматор может быть использован при построении цифровых вычислительных машин.

Двоичные 1сумматоры с одновременным .переносом известны.

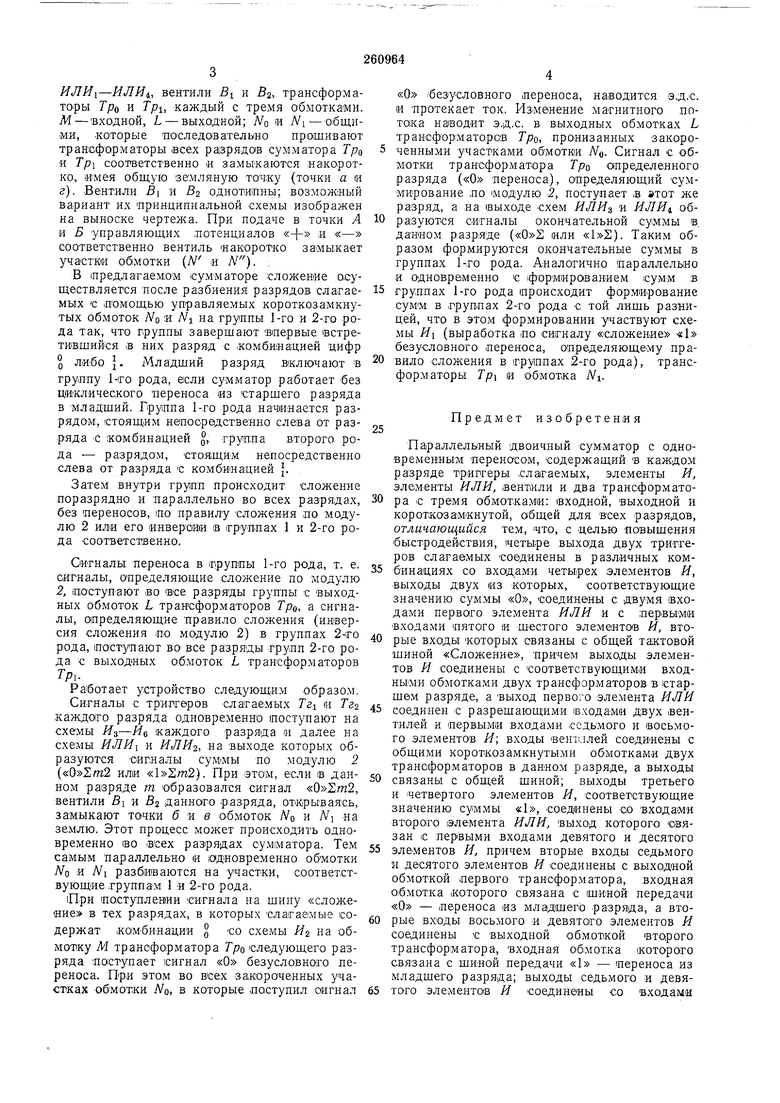

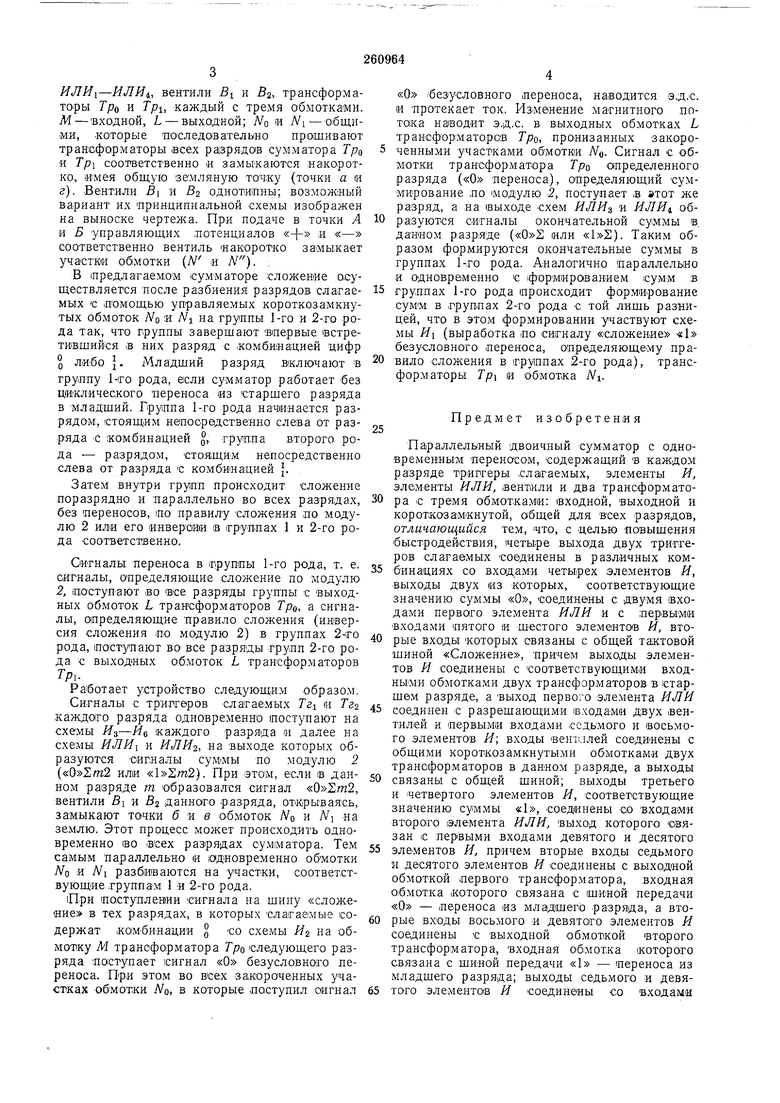

Предложенный параллельный двоичный сумматор с одновременнЫМ переносом .содержит в каждом .разряде триггеры слагаемых, элементы И, эле(Менты ИЛИ, вентили и два трансформатора с. тремя о-бмотк-ами: входной, выходной и короткозамкнутой, общей для всех разрядов. Отличается он тем, что четыре выхода двух триггеров слагаемых соединены во Btex возможных комбинациях со входами четырех элементов И, выходы двух из -которых, cooTiBeTiCTByromne значению суммы «О, соединены с двумя входами первого элемента ИЛИ и с первыми входами пятого и шестого элементов И, вторые входы которых связаны с общей тактовой шиной «.Сложение. Выходы элементов И соедииены с соответствующими входными обмотками двух тр анофарматоров в старщем разря.де, а выход первого элемента ИЛИ соединен с разрешающими входами двух вентилей и первыми входами седьмого и восьмого элементов И. Входы вентилей соединены 1C общи1М1И короткоеамкнутыми обмотками двух транбформаторов в .данном разряде, а выходы связаны с общей шиной. Выходы третьего и четвертого элементов И, соответствующие значению суммы «1, соединены со входами второго элемента ИЛИ, выход которого ОБЯзан с первыми входами .девятого и десятого элементов И. Вторые входы седьмого

и десятого элементов И соединены с выходной обмоткой первого трансформатора, входная обмотка которого связана с шиной передачи «О - переноса из младшего разряда, а вторые входы восьмого и де.вятого элементо в И

соединены с выходной обмоткой второго трансформатора, входная обмотка которого связана с шиной передачи «1 - переноса из младшего разряда. Выходы седьмого и девятого элементов И соединены со входами третьего

элемента ИЛИ, выход которого связан с выходной .клеммой «О суммы в данном разряде, а ВЫХОДЫ восьмого и десятого элементов И соединены со входами четвертого элемента ИЛИ, выход которого связан с выхо.дной клеммой «1 суммы в данном райря.де.

Сумматор снабжен «линией разбиения слагаемых на группы, которая выполнена на трансформаторах с двумя короткозамкнутыми обмотками, что позволяет ускорить сложение

и, сделать его практически не зависящим от чи1сла разрядов.

ИЛ ИI-ил Hi, вентили В и В-, трансформаторы Тро и Tp-i, каждый с тремя Обмотками. М - ВХОДНОЙ, L - выходной; Л/о и Al-общими, которые последовательно прошивают трансформаторы всех разрядов сумматора Тр и Tpi соответственно « замыкаются накоротко, общую земляную точку (точки а и г). Вентили В и Вч однотипны; возможный вариант их принципиальной схемы изо;бражен на выноске чертежа. При подаче в точки А и Б управляющих .потенциалов «-|- и «- соответственно вентиль накоротко за-мыкает участки обмотки ( « N). .

В 1предлатаемом сумматоре сложение осуществляется после разбиения разрядов слагаемых с ломощью управляемых короткозамкнутых обмоток NU и NI на группы 1-го и 2-го рода так, что группы завершают .впервые 1встретивщийся .в них разряд с .комбинацией цифр о либо J. Младщий разряд включают в группу 1-го рода, если сумматор работает без циклического переноса «з старшего разряда в Младший. Группа 1-го рода начинается разрядом, стоящим непосредственно слева от разряда с .комбинацией д, группа второго рода - разрядом, стоящим непосредственно слева от разряда с комбинацией .

Затем внутри групп происходит сложение поразрядно и параллельно во всех разрядах, без переносов, то правилу сложения по модулю 2 ИЛИ его «нвераии s группах 1 и 2-го рода соответственно.

Сигналы Переноса в .ripymnbi 1-го рода, т. е, сигналы, определяющие сложение по модулю 2, (ГЮступают во все разряды группы с выходных обмоток L трансформаторов Трд, а сигналы, о пределяющие правило сложения (инверсия сложения по модулю 2) в группах 2-го рода, поступают во все разрЯДы групп 2-го рода с выходных обмоток L траисфор.маторов Тр,.

Работает устройство следующ.им образом.

Сигналы с три.ргеров слагаемых Тг, и Tzz каждого разряда одновременно поступают на схемы Яз-Яв каждого разряда и далее на схемы ИЛ MI и ИЛИ2, на выходе которых образуются Сигналы суммы по модулю 2 ( или ). При этом, если s данном разряде т образовался сигнал , вентили BI И Вз данного разряда, открываясь, замыкают точки 5 и е обмоток NO и Л на землю. Этот процесс может происходить одновременно IBO всех разрядах сум матора. Тем самым параллельно и одновременно обмотки Л/о и разбиваются на участки, соотвехствующие группа-м 1 и 2-го рода.

Ори поступлении Сигнала на щипу «сложение в тех разрядах, в которых слагаемые содержат комбинации g СО схемы И на обмотку М трансформатора Тро следующего разряда поступает сигнал «О безусловного переноса. При этом во всех закороченных участках обмотки NO, в которые поступил сигнал

«О безусловного переноса, наводится э.д.с. и протекает ток. Изменение магнитного потока наводит э.д.с. в выходных обмотках L трансформаторов Тро, пронизанных закороченными участками обмотки Сигнал с обмотки трансформатора Тро определенного разряда («О переноса), определяющий суммирование по модулю 2, поступает в тот лее разряд, а на 1выхаде схем ИЛИ И ИЛИ/), образуются сигналы окончательной суммы в. данном разряде ( или ). Таким образом формируются окончательные суммы в группах 1-го рода. Аналогично параллельно и одновременно с |формированием сумм в группах 1-го рода происходит формирование сумм в .группах 2-го рода с той лишь разницей, что в этом формировании участвуют схемы Я (выработка по сигналу «сложение «1 безусловного переноса, определяющему правило сложения в группах 2-го рода), трансформаторы Тр и обмотка /Vj.

Предмет изобретения

Параллельный двоичный сумматор с одновременным Переносом, содержащий в каждом разряде триггеры слагаемых, элементы И, элементы ИЛИ, вентили и два трансформатора с тремя обмотками: входной, выходной и короткозамкнутой, общей для всех разрядов, отличающийся тем, что, с целью повышения быстродействия, четыре выхода двух триггеров слагаемых соединены в различных комбинациях со входами четырех элементов Я, выходы двух из которых, соответствующие значению суммы «О, соединены с двумя входами первого элемента ИЛИ и с первьши входами ПЯТОГО и Шестого элементов И, вторые входы которых связаны с общей та1ктовой шиной «Сложение, причем выходы элементов Я соединены с соответствующими входными обмотками двух трансформаторов в старщем разряде, а выход первого элемента ИЛИ соединен с разрешающими входами двух вентилей и первыми входами седьмого и восьмого элементов Я; входы вениллей соединены с общими короткозамкнутыми обмотками двух трансформаторов в данном разряде, а выходы связаны с общей шиной; выходы третьего и четвертого элементов Я, соответствующие значению суммы «1, соединены со входа)ми второго элемента ИЛИ, выход которого связан с первыми входами девятого и десятого элементов И, причем вторые входы седьмого и десятого элементов Я соединены с выходной обмоткой первого трансформатора, входная обмотка которого связана с шиной передачи «О - переноса из младшего разряда, а вторые входы восьмого и девятого элементов Я соединены с выходной обмоткой второго трансформатора, входная обмотка (которого связана с шиной передачи «1 - переноса из младшего разряда; выходы седьмого и девятого элементов Я соединены со входамИ

третьего элемента ИЛИ, выход которого связан С выходной клеммой «О оумл1ы в данном разряде, а выходы восьмого и десятого элементов И соединены со входами четвертого элемента ИЛИ, выход которого связан с выходной клеммой «1 суммы IB данном разряде.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения-вычитания чисел с плавающей запятой | 1986 |

|

SU1376080A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1989 |

|

SU1656526A2 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| Накапливающий сумматор с запоминанием переноса | 1978 |

|

SU943710A1 |

| Устройство для суммирования с услов-НыМ пЕРЕНОСОМ | 1979 |

|

SU824196A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1005027A1 |

| Комбинационный двоичный сумматор | 1990 |

|

SU1795453A1 |

| Устройство для умножения чисел в непозиционной системе счисления | 1981 |

|

SU1015382A1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| Арифметико-логическое устройство для сложения и вычитания чисел по модулю | 2017 |

|

RU2639645C1 |

WpoHopop/tc noffbi Kmopaieiofn-fff) розр(с , OHcifiqpMamg ры -горазрява

Даты

1970-01-01—Публикация