1

Изобрете.ние относится к цифровой вычислительной технике и может быть ис пользованоДЛЯ построения арифметических устройств ци эовых вычислительных машин.

Известны накапливаюише сумматоры, в состав которых входят триггерные накапливающий и приемный регистры и элементы И и ИДИ, необходимые для реализации логики работы сумматора. Приемный,() регистр таких сумматоров используется не только для приема слагаемых, но участвует также при выполнении сложения в логике организации переноса нз младших разрядов в старшие Г11 и 2 .ts

Наиболее близким к взобрете moo является накапливающий сумматор с запомишнием переноса, содержащий в каждом разряде 1счетный триггер и триггер аа- поминаквя переноса, элементы И и ИЛИ,. 20 элемент задержки, первый вход пврвого элемента И соединен со входом соответствующего разряда слагаемого . сумматора а второй вход - с управляющей шивой

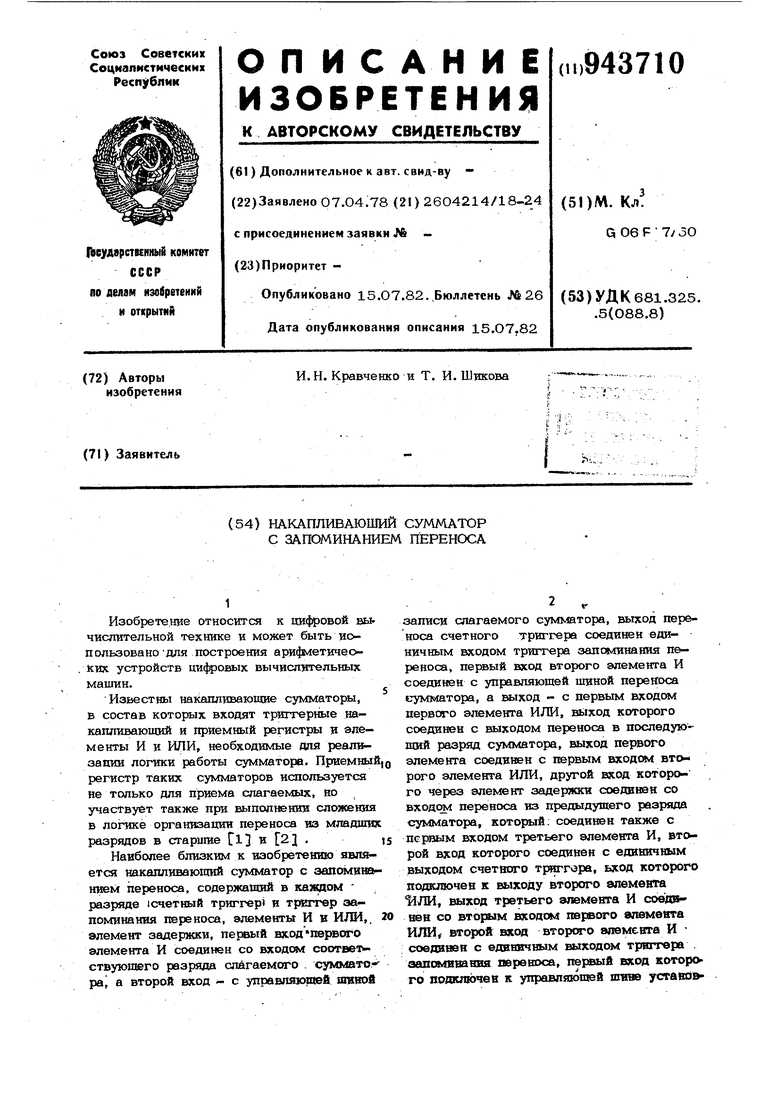

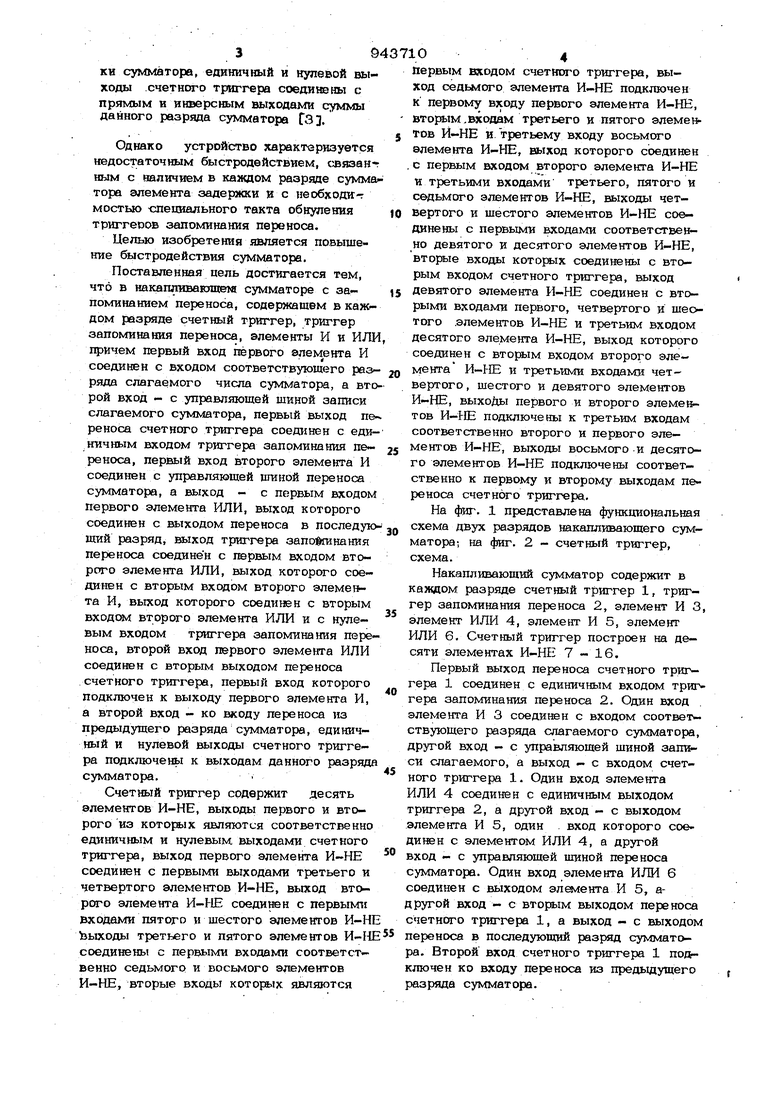

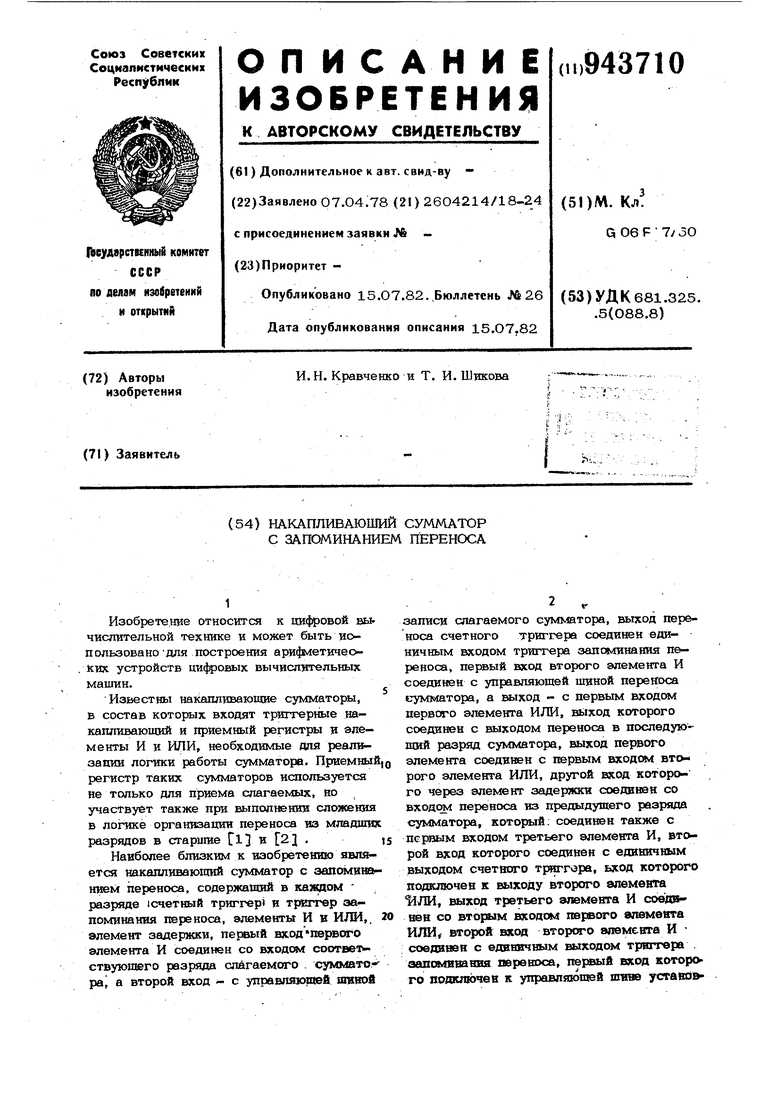

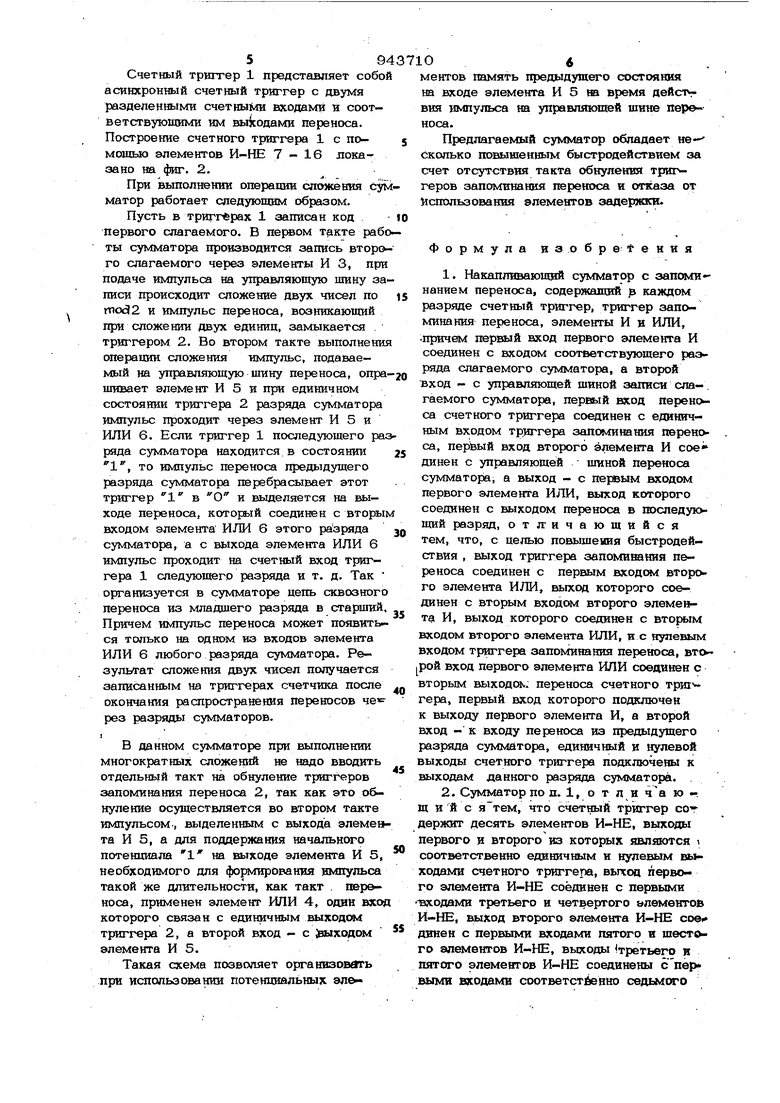

записи слагаемого сумматора, выход переноса счетного триггера соединен единичным входом трипгера запоминания переноса, первый вход второго элемента И соединен с управляющей шиной переноса сумматора, а выход - с первым виолам первого элемента ИЛИ, выход которого соединен с выходом переноса в последую-пшй разряд сумматора, выход первого элемента соединен с первым входом второго элемента ИЛИ, другой вход которого через элемент задержки соедвван со входочм переноса из предыдушего разряда сумматора, который: соединен также с перяым входом третьего элемента И, второй вход которого соединен с единичным выходом счетного тряггора, вход которохч) подключав к выходу второго эхюмевта %ЛИ, выход третьего эпемевта И соедявев со вторым входом первого аламевта ИЛИ, второй вход второго апемевта И соедввев с ещснвчным выходом триггера аапомвваввя переноса, первый вход которого подключев к управляющей шнве уставов ки сумматора, единичный и нулевой выходы счетного триггера соединены с прямым и инверсным выходами суммы данного разряда сумматора ГЗ. Однако устройство характеризуется недостаточным быстродействием, сжязанг ным с наличием в каждом разряде сумма тора элемента задержки И с иеобходи-г мостью специального такта обнуления триггеоов запоминания переноса. Целью изобретения является повышение быстродействия сумматора. Поставленная цель достигается тем, что в накаппивакяцем сумматоре с запоминанием переноса, содержащем в каждом разряде счетный триггер, триггер запоминания переноса, элементы И и ИЛИ причем первый вход первого И соединен с входом соответствующего разряда слагаемого числа сумматора, а вто рой вход - с управляющей шиной записи слагаемого сумматора, первый выход пе реноса счетного триггера соединен с единичным входом триггера запоминания пе- реноса, первый вход второго элемента И соединен с управляющей тиной переноса сумматора, а выход - с первым входом первого элемента ИЛИ, выход которого соединен с выходом переноса в последую щйй разряд, выход триггера запойганания переноса соединен с первым входом второго элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, выход которого соединен с вторым входом второго элемента ИЛИ и с нулевым входом триггера запоминания пере носа, второй вход первого элемента ИЛИ соединен с вторым выходом переноса счетного триггера, первый вход которого подключен к выходу первого элемента И, а второй вход - ко шсоду переноса из предыдущего разряда сумматора, единичный и нулевой выходы счетного триггера подключень к выходам данного разряда сумматора, Счетный триггер содержит десять элементов И-НЕ, выходы первого и второго из которых являются соответственно единичным и нулевым выходами счетного триггера, выход первого элемента И-НЕ соединен с первыми выходами третьего и четвертого элементов И-НЕ, выход второго элемента И-НЕ соединен с первыми входами пятого и шестого элементов И-Н Ьыходы третьего и пятого элементов И-Н соединены с первыми входами соответственно седьмого и восьмого элементов И-НЕ, вторые входы которых являются Первым входом счетного триггера, выход седьмого элемента И-НЕ подключен к входу первого элемента И-НЕ, вторым .входам третьего и пятого элементов И-НЕ и. третьему входу восьмого элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ и третьими входами третьего, пятого и седьмого элементов И-НЕ, выходы четвертого и шестого элементов И-НЕ соединены с первыми входами соответственно девятого и десятого элементов И-НЕ, вторые входы KOTOjbix соединены с вторым входом счетного триггера, выход девятого элемента И-НЕ соединен с вторыми входами первого, четвертого и шеотого .элементов И-НЕ и третьим входом десятого элемента И-НЕ, выход которого соединен с вторым входом второго элемента И-НЕ и третьими входами четвертого , шестого и девятого элементов И-НЕ, выхо/ц 1 первого и второго элементов И-НЕ подключены к третьим входам соответственно второго и первого элементов И-НЕ, выходы восьмого и десятого элементов И-НЕ подключены соответственно к первому и второму выходам переноса счетного триггера. На фиг. 1 представлена функциональная схема двух разрядов накапливающего сумматора-, на фиг. 2 - счетный триггер, схема. Накапливающий сумматор содержит в каждом разряде счетный триггер 1, триггер запоминания переноса 2, элемент И 3, элемент ИЛИ 4, элемент И 5, элемент ИЛИ 6, Счетный триггер построен на десяти элементах И-HIt 7 - 16. Первый выход переноса счетного триггера 1 соединен с единичным входом триггера запоминания переноса 2. Один вход . элемента И 3 соединен с входом соответствующего разряда слагаемого сумматора, другой вход - с управляющей шиной записи слагаемого, а выход - с входом счетного триггера 1. Один вход элемента ИЛИ 4 соединен с единичным выходом триггера 2, а другой вход - с выходом элемента И 5, один вход которого соединен с элементом ИЛИ 4, а другой вход - с управляющей шяной переноса сумматора. Один вход элемента ИЛИ 6 соединен с выходом элемента И 5, адругой вход - с вторым выходом переноса счетного триггера 1, а выход - с выходом переноса в последующий разряд сумматора. Второй вход счетного триггера 1 под-ключен ко входу переноса из предьщутцего разряда сумматора. Счетный триггер 1 представляет собо асинхронный счетный триггер с двумя разделенными счетными входами н соответствующими им выходами переноса. Построение счетного триггера 1 с помощью элементов И-НЕ 7-16 локазано на фиг. 2. При выполнении операшш сложения сум матор работает спедуюпшм образом. Пусть в триггерах 1 записан код первого слагаемого. В первом такте раб ты сумматора производится запись второ го слагаемого через элементы И 3, при подаче импульса на управляющую шину за писи происходит сложение двух чисел по rTiod2 и импульс переноса, возникающий при сложении двух единиц, замыкается . триггером 2. Во втором такте выполнени операшщ сложения импульс, подаваемый на управляющую щину переноса, onpa шивает элемент И 5 и при единичном состоянии триггера 2 разряда сумматора импульс проходит через элемент И 5 и ИЛИ 6. Если триггер 1 последующего ра ряда сумматора находится, в состоянии 1, то импульс переноса предыдущего разряда сумматора перебрасывает этот триггер 1 в О и выделяется на выходе переноса, который соединен с вторы входом элемента ИЛИ б этого разряда сумматора, а с выхода элемента ИЛИ 6 импульс проходит на счетный вход триггера 1 следующего разряда и т. д. Так организуется в сумматоре цепь сквозного переноса из младшего разряда в старший Причем импульс переноса может появиться только на одном из входов элемента ИЛИ 6 любого разряда сумматора. Результат сложения двух чисел получается записанным на триггерах счетчика после окончания распространения переносов че рез разряды сумматоров. В данном сумматоре при выполнении многократных сложений не надо вводить отдельнь1й такт на обнуление триггеров запоминания переноса 2, так как это обнуление осуществляется во втором такте импульсом., выделенным с выхода злеме та И 5, а для поддержания начальнсо о потенциала 1 на выходе элемента И 5, необходимого для формирования импульса такой же длительности, как такт . переноса, применен элемент ИЛИ 4, одвв вход которого связан с единичным выходом триггера 2, а второй вход - с ;выходом элемента И 5. Такая схема позволяет организовйть при использовании потенциальных эл&ментов память предыдущего состояния на входе элемента И 5 аз время дейс1 вия импульса на управляющей щине переноса. Предлагаемый сумматор обладает неСколько повышенным быстродействием за счет отсутствия такта обнуления триггеров запоминания переноса и отказа от Использования элементов задержки. Формула иаобре ения 1.Накапливающий сумматор с запоми нанием переноса, содержащий р каждом разряде счетный триггер, триггер запоминания переноса, элементы И и ИЛИ, причем первый вход первого элемента И соединен с входом соответствующего разряда слагаемого сумматора, а второй вход - с управляющей шиной записи ела-. гаемого сумматора, первый вход переноса счетного триггера соединен с единичным входом триггера запоминания парено са, первый вход второго элемента И сое динен с управляющей щиной переноса сумматора, а выход - с первым входом первого элемента ИЛИ, выход которого соединен с выходом переноса в последующий разряд, отлгичающийся тем, что, с целью повышения быстродействия , выход триггера запомишния переноса соединен с первым входом второго элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, выход которого соединен с втор« 1М входом второго элемента ИЛИ, и с нулевым входом триггера запоминания переноса, BTCV вход первого элемента ИЛИ соединен с вторым выходе,, переноса счетного триг гера, первый вход которого подключен к выходу первого элемента И, а второй вход - к входу переноса из предыдущего разряда сумматора, единичный и нулевой выходы счетного триггера подключены к выходам данного разряда сумматора. 2.Сумматор по п. 1, о т ли ча ю щ и и с , что счетный триггер cor держит десять элементов И-НЕ, выходы первого и второго из которых являются 1 соответственно единичным и нулевым вь} ходами счетного триггера, выход первого элемента И-НЕ соединен с первыми -входами третьего и четвертого элементов И-НЕ, выход второго элемента И-НЕ сое двнен с первыми входами пятого и щест го элементов И-НЕ, выходы третьего и пятого элементов И-НЕ соединены с пер вымн вкодамв соответственно сваылого

и восьмого элементов И-НЕ, вторые в со«ды которых являются первым входам с 1ет ного триггера, выход седьмого элемента И-НЕ подключен к первому входу перво го элемента И-НЕ, вторым входам третьего и пятого элементов И-НЕ и третьему входу восьмого элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, и третьими входами третьего, пятого и седьмого элементов И-НЕ, выходы четвертого и шестого элементов И-НЕ соединены с первыми входами соответственно девятого и десятого элементов И-НЕ, вторые входы которых соединены с вторым входом счетного триггера, выход девятого элемента И-НЕ соединен с вторыми входами первого, чет вертого и шестого элементов И-НЕ, и третьим входстл десятого элемента И-НЕ,

выход которого соединен с вторым входом второго элемента И-НЕ и третьим входами четвертого, шестого и девятого элементов И-НЕ, выходы первого и вто рого элементов И-НЕ подключены к третьим входам соответственно второго и первого элементов И-НЕ, выходы восьмого и десятого элементов И-НЕ подключены соответственно к первому и второму выходам переноса счетного триггера.

Источники инфopv aшш, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 351214, кл. G,06F 7/5О, 1972.

2.Авторское свидетельство СССР №531157, кл. G06F 7/5О, 1974.

3.Р. К. Ричарде Арн4метические one- рашга на ЦВМ. М., ИИЛ, 1957, с. 115119 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ | 2005 |

|

RU2308073C2 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

giuHO Запись числа 1рКШЧ ч S№№тс КИ+1}0 Шина „Перенос перенос Om(i-l)p

s

Lz

a

«N4

t±d

L..t

Авторы

Даты

1982-07-15—Публикация

1978-04-07—Подача