входами логического нуля и логической единицы преобразователя. Кроме того, преобразователь деся тичного разряда десятков в двоичный код содержит десять элементов И и четыре элемента ИЛИ, выходы которых являются выходами преобразователя разряда десятков в двоичный код, инверсный вход младаиего разряда которого соединен с первыми входами первого, второго, третьего и четвер того элементов И, вторые входы кото рых соединены соответственно с инверсными входами третьего, четвертого, второго и третьего разрядов преобразователя разряда десятков в двоичный код, прямой вход первого разряда которого соединен с первыми входами пятого, шестого и седьмого элементов И, вторые входы которых соединены соответственно с первыми входами восьмого, девятого и вторым входом восьмого элементов И и с пря Jviыми входами третьего и второго и инверсным входом второго разрядов преобразователя разряда десйтков в двоичный код,,инверсный вход трет го разряда которого соединен соответственно с третьими входами шесто го и седьмого элементов И и вторым входом девятого элемента И, первый и второй входы.десятого элемента И соединены с инверсным входом четвер того разряда преобразователя разряд десятков в двоичный код, выходы дву младших разрядов которого соединены соответственно с прямым входом первого и инверсным входом второго раз рядов преобразователя разрядов деся ков в двоичный код, выходы первого и пятого, четвертого и девятого, седь мого и десятого элементов И соедине вы соответственно с входами первого второго и третьего элементов ИЛИ, выходы второго, третьего, шестого и восьмого элементов И соединены с вхо дами четвертого элемента ИЛИ. Преобразователь десятичного разряда сотен в двоичный код содержит тринадцать элементов И и пять элемен тов ИЛИ, выходы которых являются выходами старших разрядов преобразователя разряда сотен в двоичный код прямой вход первого разряда которого соединен с первыми входами первого, второго, третьего и четвертого элементов И, вторые входы которых соеди нены соответственно с инверсными вхо дами четвертого, второго, прямыми вх дами третьего и четвертого разрядов преобразователя разряда сотен в двоичный код, прямой вход первого разряда которого соединен с первыми входами пятого, шестого и седьмого элементов И, вторые входы которых соединены соответственно с прямыми вхо дами четвертого, пятого и инверсным входом третьего разрядов преобразователя разряда сотен в двоичный код, прямой вход второго разряда которого соединен с третьим входом седьмого элемента И и с первыми входами восьмого и девятого элементов И, вторые входы которых соединены соответственно с инверсным и прямым входами третьего разряда преобразователя разряда сотен в двоичный код, инверсный вход второго разряда которого соединен с .первыми входами десятого и одиннадцатого элементов И, вторые входы которых соединены с прямым входом третьего разряда преобразователя разряда сотен в двоичный код, прямой вход четвертого разряда которого через двенадцатый и тринадцатый элементы И соединен соответственно с первыми входами первого и второго элементов ИЛИ, вторые входь которых Соединены соответственно с выходами восьмого и девятого элементов И, а третий вход первого элемента ИЛИ соединен с выходом одиннадцатого элемента И, выходы первого и шестого элементов И соединены соответственно с первыми входами третьего и четвертого элементов ИЛИ, вторые входы которых соединены с выходами пятого и второго элементов И, выходы третьего, четвертого, седьмого и десятого элементов И соединены с входами пятого элемента ИЛИ, входы первого, второго и третьего разрядов преобразователя разряда сотен в двоичный код соответственно являются выходaivffl трех младших разрядов преобразователя разряда сотен в двоичный код, помимо этого, в нем разряд сумматора состоит из трех мультиплексеров, выходы которых являются соответственно выходами суммы, младшего и старшего разрядов переноса сумматора, а управляющие входы всех мультиплексеров соединены соответственно с входами первого и второго слагаемых и с входами младшего и старшего разрядов переноса, первый вход первого мультиплексера соединен с прямым входом третьего слагаемого, а первые входы второго и третьего г 1ультиплексеров соединены с входом логического нуля, второй и третий входы первого и второго мультиплексеров соединены соответственно с, инверсным и прямым входами третьего слагаемого, четвертые входы первого и второго мультиплексеров - соответственно с прямым входом третьего слагаемого и входом логической единицы, пятые входы первого и второго мультиплексеров соединены соответственно с инверсным и прямым входами третьего слагаемого, шестой и седьмой входы первого и второго мультиплексеров соединены соответственно с прямом входсяи третьего слагаемого и входом логической единицы., входы с первого по седьмой третьего мультиплексера соединены с входом логического нуля, восьмой и девятый входы первого мультиплексера соединены с инверсным входом третьего слагаемого, восьмой и девятый входы второго и третьего мультиплексеров соединены соответственно с прямым и инверсным входами третьего слагаемого, с прямым входом третьего слагаемого и входом логического нуля, десятый и один.надцатый входы первого, второго и третьего мультиплексеров соединены соответственно с прямым входом третьего слагаемого, с входом логической единицы и входом логического нуля, двенадцатый вход первого, и второго мультиплексеров соединен с инверсным входом третьего слагаемого, а двенадцатый, тринадцатый и четырнадцатый входы третьего мультиплексера соединены соответственно с прямым входом третьего слагаемого/ с входом логического нуля и входом логической единицы, тринадцатый и четырнадцатый входы первого мультиплексера соединены соответственно с прямым и инверсным входами третьего слагаемого, а пятныдцатый и шестнадцатый входы первого мультиплексера соединены соответственно с инверсным и прямым входами третьего слагаемого, тринадцатый и четырнадцатый входы второго мультиплексера соединены соответственно с входом логической единицы и инверсным входом третьего слагаемого, пятнадца.тый и шестнадцатый входы второго мультиплексера - с инверсным входом третьего слагаемого и входом ло гической единицы, пятнадцатый и шестнадцатый входы третьего мультиплексера соединены соответственно с прямым входом третьего слагаемого и входом логической единицы- .

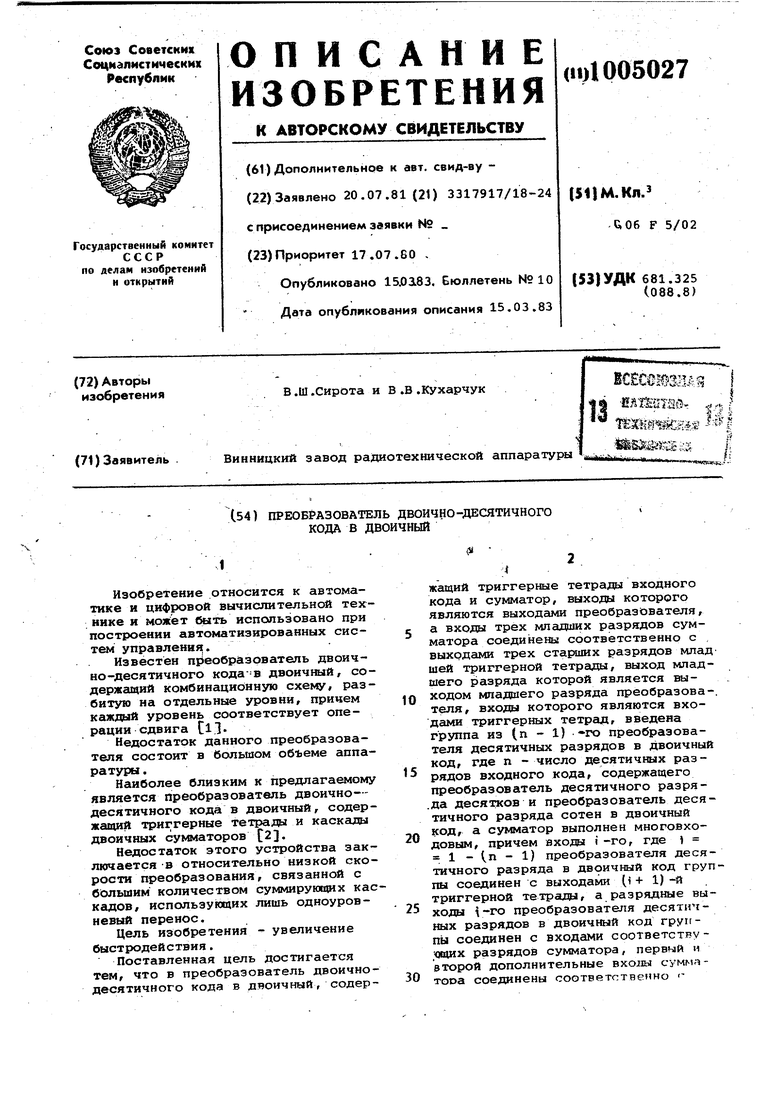

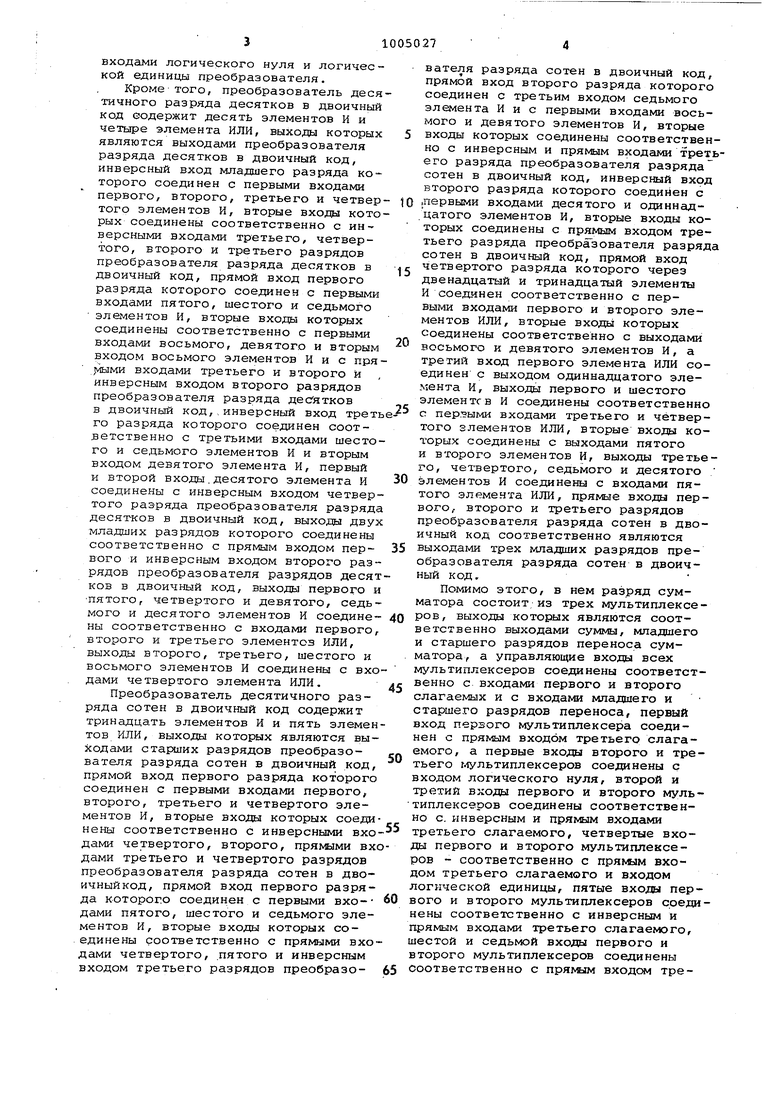

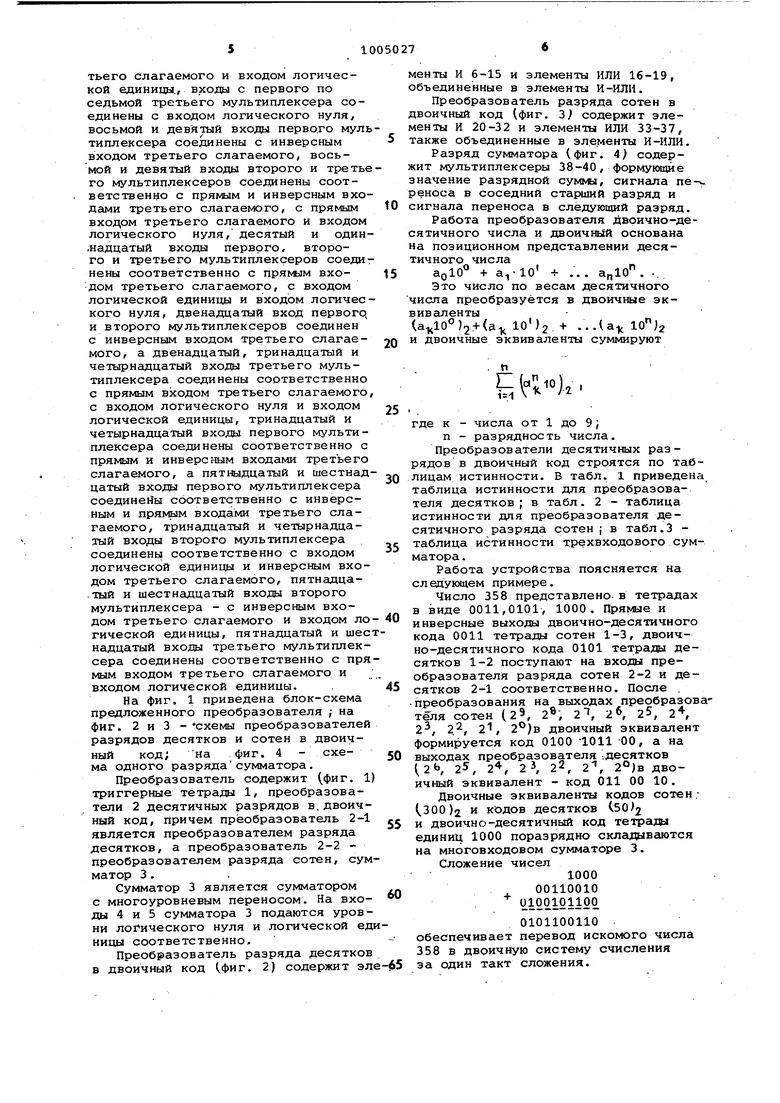

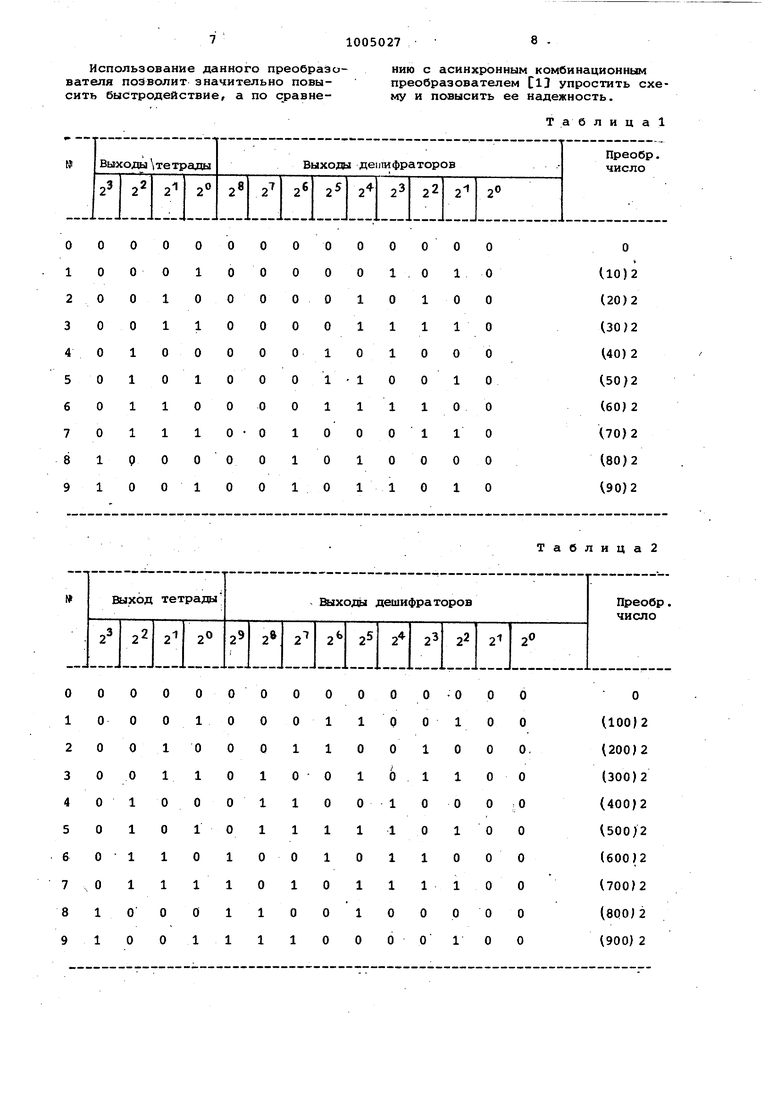

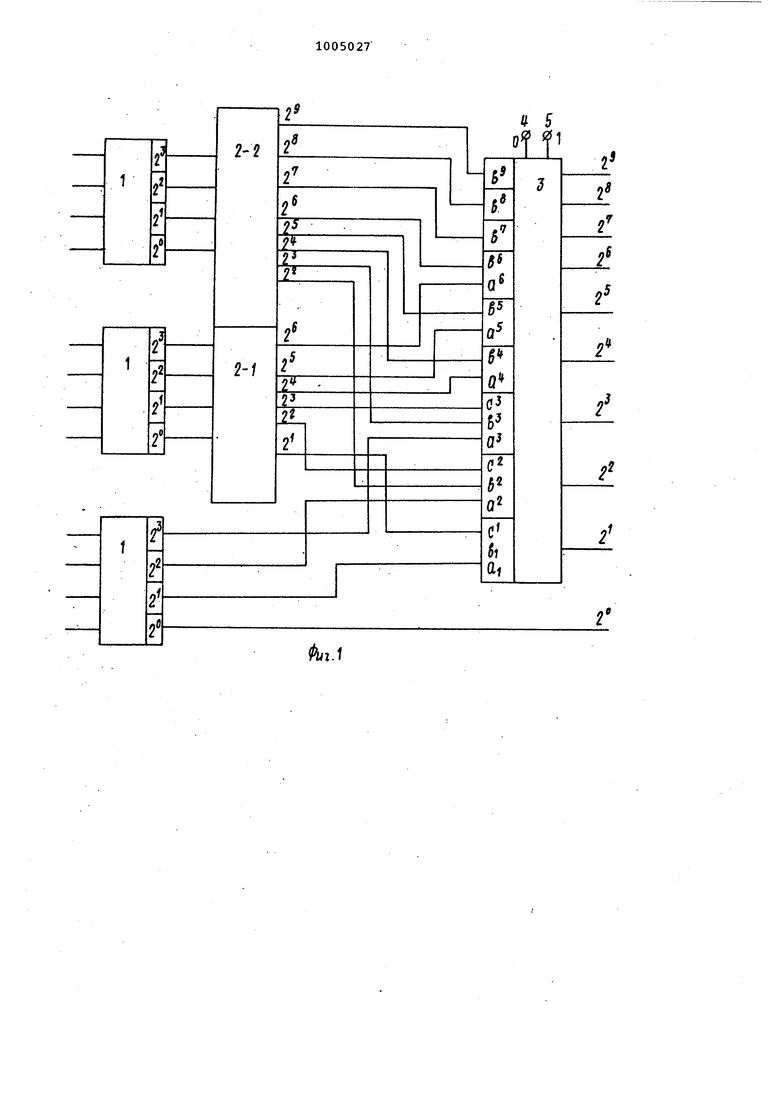

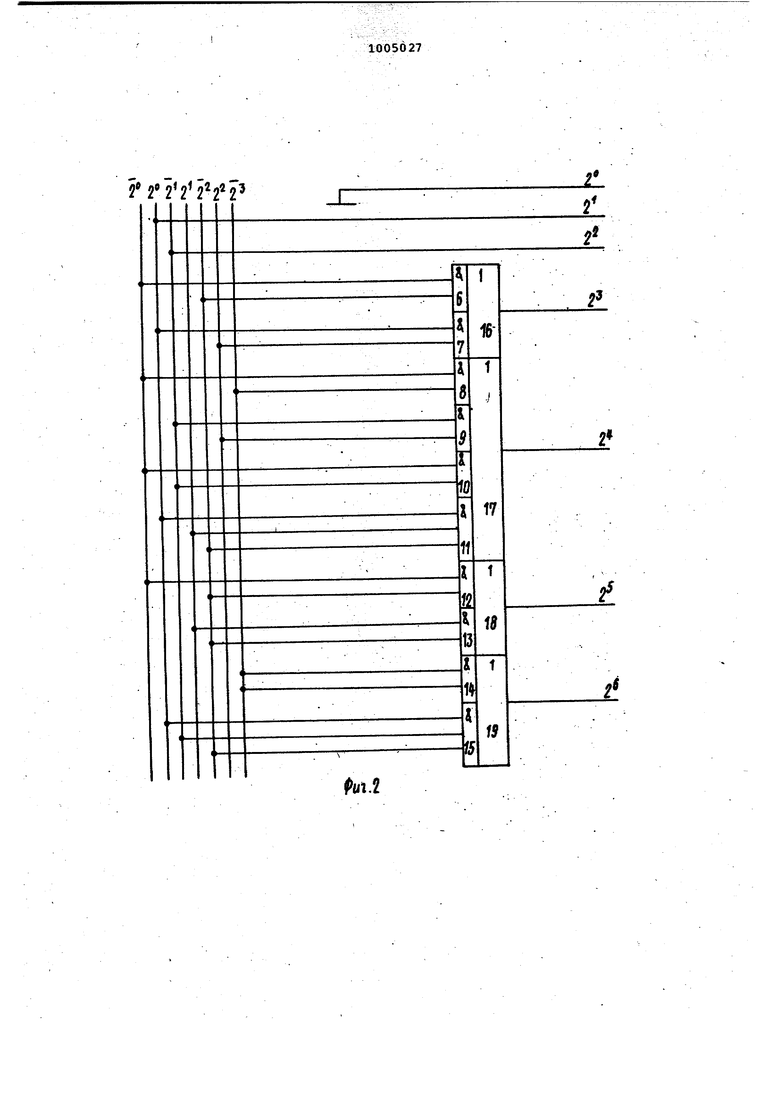

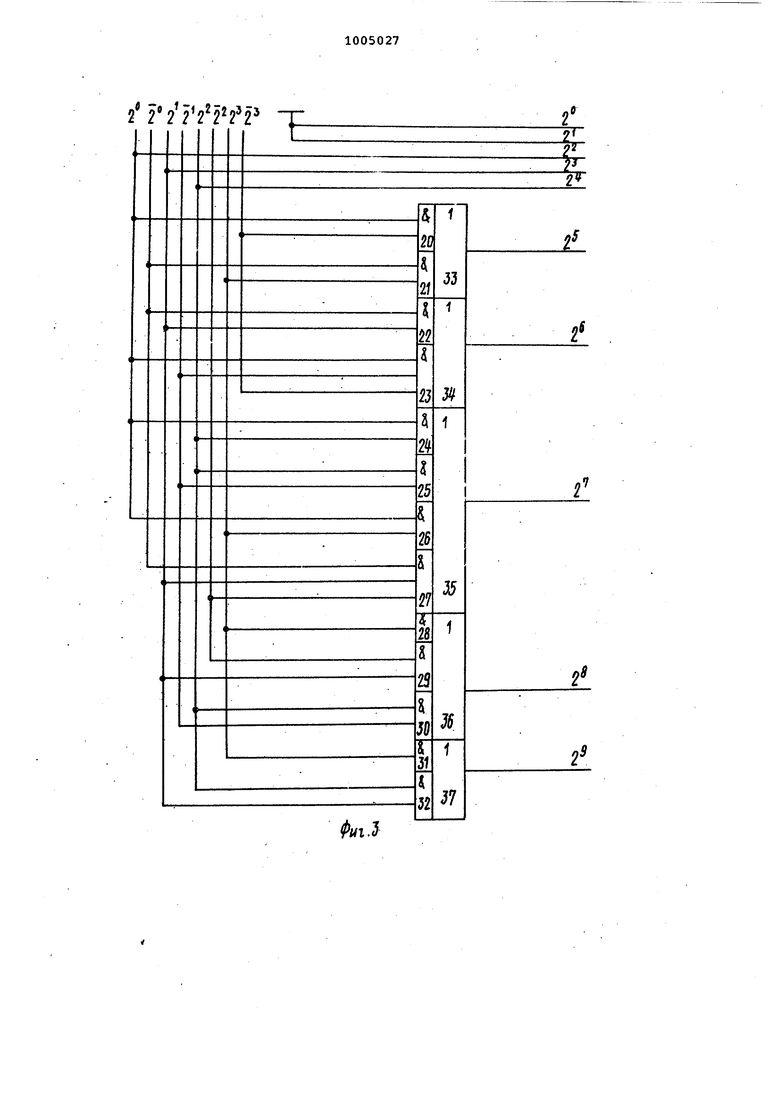

На фиг. 1 приведена блок-схема предложенного преобразователя ; на фиг. 2 и 3 - схемы преобразователей разрядов десятков и сотен в двоичный код; на фиг. 4 - схема одного разрядасумматора.

Преобразователь содержит (фиг. 1) триггерные тетрады 1, преобразователи 2 десятичных разрядов в. двоичный код, причем преобразователь 2-1 является преобразователем разряда десятков, а преобразователь 2-2 преобразователем разряда сотен, сумматор 3. .

Сумматор 3 является сумматором с многоуровневым переносом. На входы 4 и 5 сумматора 3 подаются уровни логического нуля и логической единицы соответственно.

Преобразователь разряда десятков в двоичный код (фиг. 2) содержит эле

менты И 6-15 и элементы ИЛИ 16-19, объединенные в элементы И-ИЛИ.

Преобразователь разряда сотен в двоичный код (фиг. 3) содержит элементы И 20-32 и элементы ИЛИ 33-37, также объединенные в элементы И-ИЛИ.

Разряд сумматора (фиг. 4) содержит мультиплексеры 38-40, формующие значение разрядной суммы, сигнала пе реноса в соседний старший разряд и сигнала переноса в следующий разряд.

Работа преобразователя двоично-десятичного числа и ДВОИЧНЫЙ основана на позиционном представлении десятичного числа

ао10° + + ... апЮ. ...

Это число по весам десятичного числа преобразуется в двоичные эквиваленты

()2.+ (ai 10)2 + ...(а и двоичные эквиваленты суммируют

5 К°)

где к - числа от 1 до 9; п - разрядность числа.

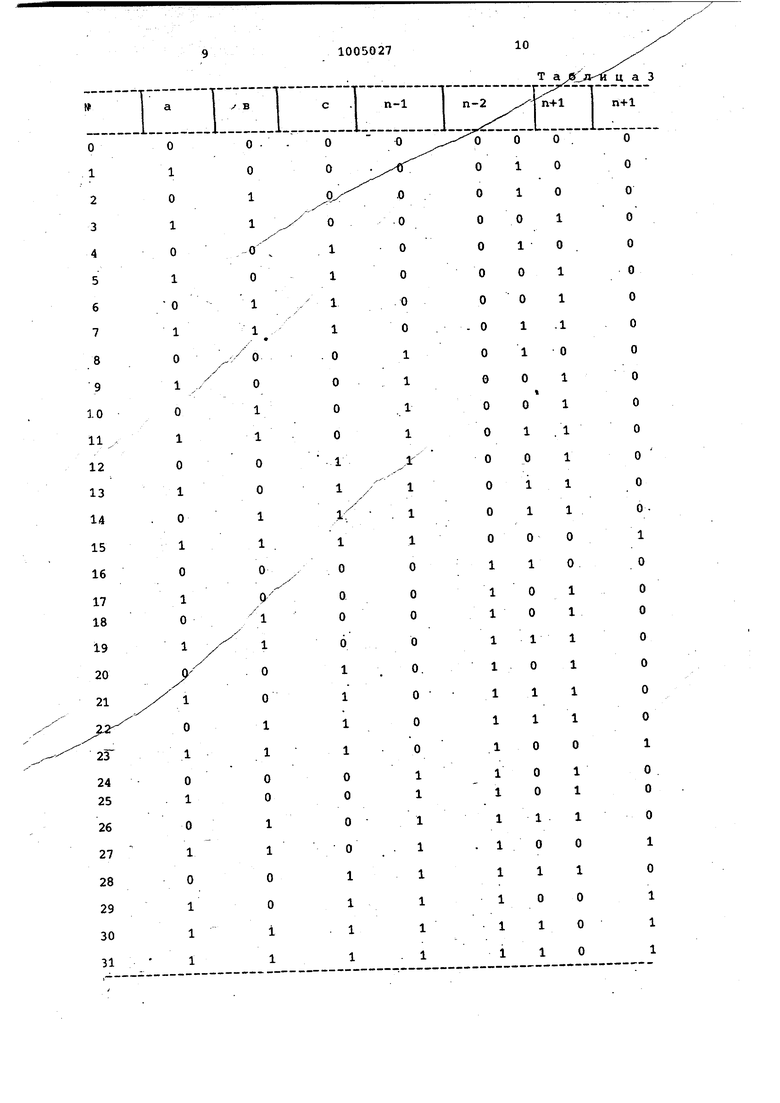

Преобразователи десятичных разрядов в двоичный код строятся по таблицам истинности. В табл. 1 приведен таблица истинности для преобразователя десятков; в табл. 2 - таблица истинности для преобразователя десятичного разряда сотен ; в табл.3 таблица истинности трехвходового сумматора .

Работа устройства поясняется на ел еяующем примере.

Число 358 представлено, в тетрадах в виде 0011,0101, 1000. Прямые и инверсные выходы двоично-десятичного кода ООН тетрады сотен 1-3, двоично-десятичного кода 0101 тетрады десятков 1-2 поступают на входы преобразователя разряда сотен 2-2 и десятков 2-1 соответственно. После . преобразования на выходах преобразов теля сотен (2, 2, 2, 2, 2, 2, 2., 21, 2)в двоичный эквивалент формируется код 0100 1011 00, а на выходах преобразователя десятков (24 25, 2, 23, 22, 2, 2°)в двоичный эквивалент - код 011 00 10.

Двоичные эквиваленты кодов сотен; (300)2 и кодов десятков (.50)2 и двоично-десятичный код тетрады единиц 1000 поразрядно складываются на многовходовом сумматоре 3.

Сложение чисел

1000

, 00110010 0100101100

0101100110

обеспечивает перевод искомого числа 358 в двоичную систему счисления за один такт сложения.

Использование данного преобразователя позволит значительно повысить быстродействие, а по qpaBHeнию с асинхронным комбинационным преобразователем 1 упростить схему и повысить ее надежность.

Таблица формула изобретения 1. Преобразователь двоично-деся тичного кода в двоичный, содержащий триггерные тетрады входного кода и сумматор, выходы которого являют ся выходами преобразователя, а вхо ды трех младшйх разрядов сумматора соединены соответственно с выходами трех старших разрядов младшей триггерной тетрады, выход младшего разряда которой является выходом младшего разряда преобразователя, входы которого являются входами триггерных тетрад, отличающийся тем, что, с целью повьошения быстродействия преобразователя, в него введена группа из (п- 1)-го преобразователя десятичных разрядов в двоичный код, где п - число десятич ных разрядов входного кода, содержа щего преобразователь десятичного ра ряда десятков и преобразователь дес тичного разряда сотен в двоичный код, а сумматор выполнен многовходо вым, причем входы i-го где i 1 - (п - 1) преобразователя десятичног разряда в двоичный код.группы соеди нен с выходами (f + 1) -и триггерной тетрады, а разрядные выходы i -го преобразователя десятичных разрядов в двоичный код группы соединены с входами соответствующих разрядов су матора, первый и второй дополнительные входы сумматора соединены соответственно с входами логичес кого нуля и логической единицы преобразователя. 2. Преобразователь по п. 1, о т личающийся тем, что в нем преобразователь десятичного разряда десятков в дв.оичный код содержит десять элементов И и четыре элемента ИЛИ, выходы которых являются выходами преобразователя разряда деся ков в двоичный код, инверсный вход мла.цшего раз-ряда которого соединен с первыми входами первого,второго, третьего и четвертого элементов И,вто рые входы которых соеди-нены соответствен но с инверсными входами третьего четвертого, второго и третьего разрядов преобразователя разряда де сятков в.двоичный код, прямой вход первого разряда которого соединен с первыми входами пятого, шестого и седьмого элементов И, вторые входы которых соединены соответственно с первыми входами восьмого, девятого и вторым входом восьмого элементов И и с прямыми входами третьего и второ го и инверсным входом второго разря дов преобразователя разряда десятков в двоичный код, инверсный вход третьего разряда которого соединен соответственно с третьими входами шестого и седьмого элементов И и вторым входом девятого элемента И, первый и второй вхрды десятого элемента И соединены с инверсным входом четвертого разряда преобразователя разряда десятков в двоичный код, выходы двух младших разрядов которого соединены соответственно с прямым входом первого и инверсным .входом второго разрядов преобразователя .разрядов десятков в двоичный код, выходы первого и пятого, четвертого и девятого, седьмого и десятого элементов И соединены соответственно с входами первого, второго; и третьего элементов ИЛИ, выходы второго, третьего, шестого и восьмого элементов И соединены с входами четвертого элемента ИЛИ. 3. Преобразователь по пп-. 1 и 2, отличающийся тем, что в нем преобразователь десятичного разряда сотен в двоичный код содержит тринадцать элементов И. и пять элементов ИЛИ, выходы которых являются выходами старших разрядов преобразователя разряда сотен в двоичный код, прямой вход первого разряда которого соединен с первыми входами первого, второго, третьего и четвертого элементов И, вторые входы которых соединены соответственно с инверсными входами четвертого, второго, прямыми входами третьего и четвертого разрядов преобразователя разряда сотен в двоичный код, прямой вход первого разряда которого соединен с первыми входами пятого, шестого и седьмого элементов И, вторые входы которых соединены соответственно с прямыми входами четвёртого, пятого и инверсным входом третьегр разрядов, преобразователя ; разряда; сотен в двоичный код, прямой вход второго разряда которого соединен с третьим входом седьмого элемента И и с первьп да входами вось мого и девятого элементов И, вторые входы которых соединены соответственно с инверсным и прямым вхСДами третьего разряда преобразователя разряда сотен в двоичный код, иКЗерсный вход второго разряда которого соединен с первыми входами десятого и одиннадцатого элементов И, вторые входы которых соединены с прямым входом третьего разряда преобразователя разряда сотен в двоичный код, прямой вход четвертого разряда которого через двенадцатый и тринадцатый элементы И соединен соответственно с первыми входами первого и второго элементов ИЛИ, вторые входы которых соединены соответственно с выходами восьмого и девятого элементов И,, а третий вход первого элемента ИЛИ соединен с выходом одиннадцатого элемента И, выходы первого и шестого элементов И соединены соответственно с первыми входами третьего и четвертого элементов ИЛИ, вторые входы которых.соединены с выходами пятого ,и второго элементов И, выходал третьего, четвертого, седьмого и десятого элементов И соединены с входами пятого элемента ИЛИ, прямые входы первого, второго и третьего разрядов преобразователя разряда сотен в двоичный код соответственно являются выходами трех младших раз рядов преобразователя разряда -сотен в двоичный код. 4. Преобразователь по пп, 1 - 3, отличающийся тем, что в нем разряд сумматора состоит из трех мультиплекСеров, выходы которых являются соответственно выходами суммы, младшего и старшегоразрядов переноса сумматора, а управляющие ..входы всех мультиплек Серов соединены соответственно с входами первого и второго слагаемых к с входами младшего разрядов переноса, первый вход первого мультиплексёра соединен с прямым входом третьего слагаемого, а первые входы в.торого и третьего мультиплекСеров соединены с входом логического нуля, второй и третий входы первого и второго мультиплекс ров соединены соответственно с инверсным и прямым входами третьего слагаемого, четвертые входы первого второго мультип-лексеров - соответст венно с прямым входом третьего слагаемого и входом логической единицы пятые входы первого и второго мульти плексеров соединены соответственно с х нверсным и прямым входами третьего cj araeMoro, шестой и седьмой входы первого и второго мультиплексеров соединены соответственно с прямым входом третьего слагаемого и входом логи аской единицы, входы с первого по седьмой третьего мультиплексёра соединены -Сх ходом логического нуля восьмой и .тый входы первого мул типлексёра coeдинe ы с инверсным входом третьего слагаемого , восьмой и девятый входы второго и третьего мультиплексеров соединены соответственно с прямым и инверсным входами третьего слагаемого, с прямым входом третьего слагаемого и входом логического нуля, десятый .и одиннадцатый входы первого, второго и третьего мультиплексеров соединены соответственно с пряким входом третьего слагаемого, с входом логической единицы и входом логического нуля , двенс1дцатый вход первого и втог рого мультиплексеров- соединен с инверсным входом третьего слагаемого, а двенадцатый, тринадцатый и четырнадцатый входы третьего мультиплексёра соединены-соответственно с входом третьего слагаемого, с входом логического нуля и входом логической, единицы, тринадцатый и четырнадцатый входы первого мультиплексёра соединены соответственно с прямым и инверсным входами третьего слагаемого, а пятнадцатый и шестнадцатый входы первого мультиплексёра соединены -соответственно с инверсным и входами третьего слагаемого, тринадцатый и четырнадцатый входы второго мультиплексера соединены соответственно с входом логической единицы и инверс.ным входом третьего слагаемого, пятнадцатый и шестнадцатый входы второго мультиплексёра - с инверсным входом третьего слагаемого и входом логической единицы, пятнадцатый и шестнадцатый входы третьего мультиплексёра соединены соответственно с прямым входом третьего слагаемого и входом логической единицы. Источники информации, принятые во внимание при экспертизе . 1.Алексенко А.Г. Основы микросхемотехники. Сов. радио, 1977, с. 77-78, рис. 54. 2.Патент США 3705299, кл. 235-155, 1973.

2

2L

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехдекадный преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU943705A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1981 |

|

SU1003068A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1984 |

|

SU1221758A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

Авторы

Даты

1983-03-15—Публикация

1981-07-20—Подача