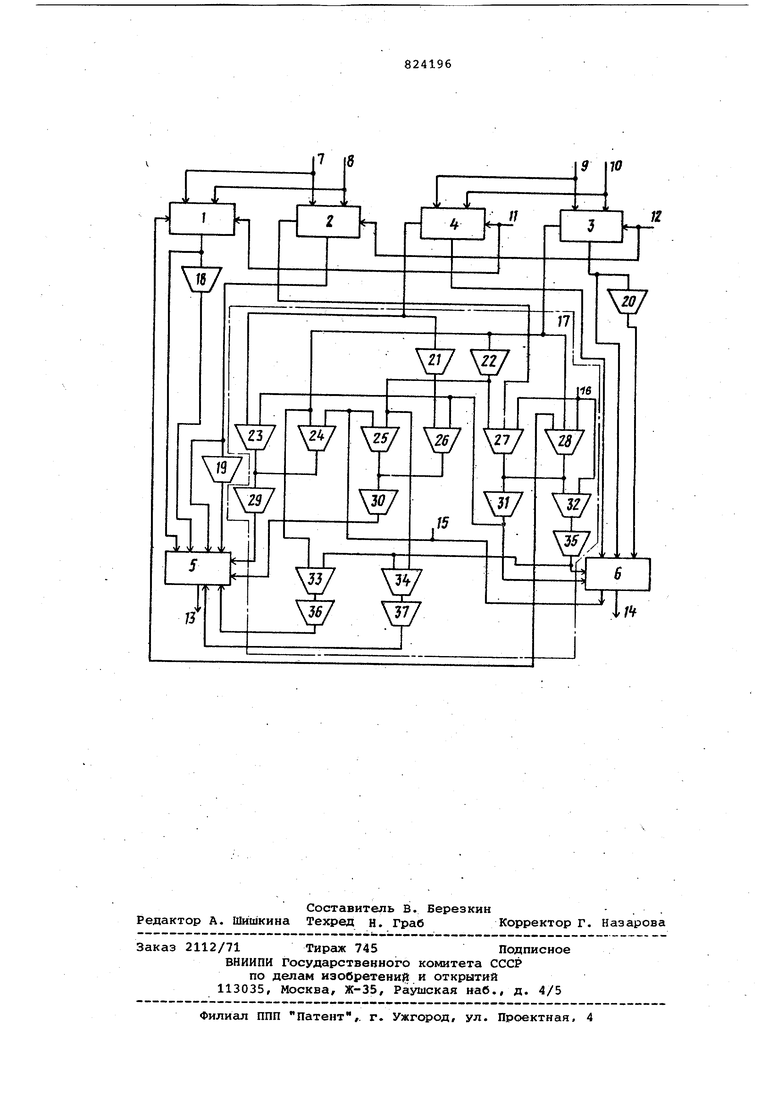

Изобретение относится к автоматик и вычислительной технике и может быт использовано при реализации техничес ких средств вычислительных машин и дискретной автоматики. Операция суммирования является ти повой при выполнении арифметических действий в ЦВМ. В устройствах цифровой фильтрации для сжатия сигналов процент операций сложения составляет 60%. Поэтому большое внимание уде ляется вопросам построения устройств алгебраического сложения. Одним из аппаратных средств решения sonpioca ускорения выполнения операции йлгебраического сложения являются суммато ры с условными суммами. Известны сумматоры с цепью условного переноса, в которых цепь формирования сумм и цепь ускоренного распространения переносов разбиваются на две части. Все цепочки начинают действовать одновременно и заканчивают свою работу одновременно f. Однако в схемах сумматоров не предусмотрены технические решения выполнения операций вычитания. Наиболее близким к предлагаемому является устройство для суммирования с условным переносом, содержа цее три сумматора, два входа у каждого из первых двух сумматоров соединены с шинами подачи старших разрядов слагаемых, два входа третьего сумматора соединены с шинами подачи младших разрядов слагаемых, третий вход первого сумматора соединен .с шиной подачи уровня.логической единицы,. третьи входы второго и третьего сумматоров соединены с шиной подачи уровня логического нуля 2. Однако устройство не может быть непосредственно использовано для выполнения операции вычитания. Цель изобретения - расширение функциональных возможностей устройства путем обеспечения выполнения операции вычитания. Поставленная цель достигается тем, что устройство для суммирования с условным переносом, содержащее три сумматора, первый и второй входы каждого из первых двух сумматоров соединены с шинами подачи старших разрядов слагаемых устройства, первый и второй входы третьего сумматора соединены с шинами подачи младших разрядов слагаемых устройства, третий вход первого сумматора соединен с шиной подачи уровня логической единицы устройства, третьи входы второго и третьего сумм торов соединены с шиной подачи уровня логического нуля устройства, содержит четвертый сумматор, первый и второй входы которого соединены с ши нами подачи младших разрядов слагаемых, а третий вход четвертого суммаiTopa соединен с шиной подачи уровня логической единицы устройства, а так же содержит два коммутатора, три блока инверсии и блок анализа состо ния сумматоров, входы которого соответственно соединены с выходами сигналов переноса сумматоров, в управляющие входы соединены с шинами подачи сигналов сложения и вычитания устройства, первый, второй третий и четвертый выходы блока анализа состояния сумматоров соединены с соотве ствующими управляющими входами перво го коммутатора, первый и второй информационные входы которого соединен с выходом первого сумматора непосред ственно и через первый блок инверсии, а третий и четйерть1й информационные входы - с выходом второго су матора непосредственно и через второ блок инверсии, первый информационный вход второго коммутатора соединен с выходом четвертого сумматора, а второй и третий информационные входы с выходом третьего сумматора непосредственно и через третий блок инвер сии, выходы первого и второго коммут торов соединень с выходными шинами соответственно старших и младших раз рядов результата, пятый, шестой и седьмой :выходы блока анализа состояния сумматоров соединены соответственно с первым, вторым и третьим управляющими входами второго коммута тора . Кроме того, блок анализа состояния сумматоров содержит элементы И-Н и НЕ, причем входы первого и второго элементов НЕ соединены с третьим и. четвертым входами блока и с первьоми входами первого и второго элементов И-НЕ соответственно, первые входы третьего и четвертого элементов И-НЕ соединены с выходами второго и перво го элементов НЕ соответственно, первый и второй входы пятого элемента И-НЕ соединены с выходом второго эле мента НЕ и вторым входом блока, первый и второй входы шестого элемента И-НЕ соединены с первым и третьим входами блока, вторые входы второго и третьего элементов И-НЕ соединены с пер.вым управляющим входом и шестым выходом блока, третьи входы пятого и шестого элёментов И-НЕ соединены со вторым управляющим входом блока, выходы первого и второго элементов И-НЕ объединены и подключены через третий элемент НЕ к первому выходу блока, выходы третьего и четвертого элементов И-НЕ объединены и подключены через четвертый элемент НЕ к третьему выхопу блока, выходы пятого и шестого элементов И-НЕ объединены и подключены к первому входу седьмого элемента И-НЕ к через пятый элемент НЕ - ко вторым входам первого и четвертого элементов И-НЕ и пятому выходу блока, второй вход седьмого элемента И-НЕ подключен ко второму управляющему входу блока, а вы- |х6д через шестой элемент НЕ - к седьмому выходу блока и первым входам восьмого и девятого элементов И-НЕ, вторые входы которых соединены с третьим входом блока и выходом второго элемента НЕ соответственно, а выходы через седьмой и восьмой элементы НЕ соответственно - со вторым и четвертым выходами блока. На чертеже изображена схема устройства. Устройство содержит сумматоры 1-4 коммутаторы 5 и б, шины 7 и 8 подачи старших разрядов слагаемых, шины 9 и 10 подачи младших разрядов, слагаемых, шину 11 подачи уровня логической единицы, шину 12 подачи уровнялогического нуля, выходные шины 13 старших разрядов результата, выходные шины 14 младших разрядов результата, шину 15 подачи сигнала сложения и шину 16 подачи сигнала вычитания, блок 17 анализа состояния сумматоров и блоки 18-20 инверсии. Блок 17 анализа состояния сумматоров содержит элементы НЕ 21 и 22, И-НБ 2328, НЕ 29-31, И-НЕ 32-34, НЕ 35-37. Шины 7 и 8 подачи старших разря дов слагаемых соединены с первыми и вторыми входами сумматоров 1 и 2. Шины 9 и 10 подачи младших разрядов слагаемых соединены с первыми и вторыми входами сумматоров 3 и 4. Третьи входы сумматоров 1 и 4 соединены с шиной 11 подачи уровня логической единицы, третьи входы сумматоров 2 и 3 соединены с шиной 12 подачи уровня логического нуля. Выходы сумматоров 1 .и 2 в прямом и в обратном кодах через блоки 18 и 19 инверсии соединены с входами коммутатора 5, выходы которого соединены с выходными шинами 13 старших разрядов результата. Выходы элементов НЕ 29, 30, 36 и 37 соединены с управляющими входами KOMTiyTaTopa 5, по этим связям подаются управляющие работой коммутатора 5 сигнгшы. Выход сумматора 4 соединен со .входом коммутатора 6. Выход сумматора 3.в прямом и в обратном кодах. через блок 20 инверсии соединен со входами коммутатора б , выходы которого соединены с выходными шинами 14 младших разрядов результата. Шина 15 подачи сигнала сложения и выходы элемента НЕ 31, элемента НЕ 35. соединены с управляющими входами коммутатора б, по этим связям подаются сигналы, управляющие работой коммутатора. Выход элемента НЕ 35 соединен также со вхо дами элементов И-НЕ 33 и 34. Шина 16 подачи сигнала вычитания соединена со входами элементов И-НЕ 27,28 и 32. Выходы сигналов переноса из сумматоров 1 и 2 соединены- со входами , элементов И-НЕ 28 и 27 соответственно. Выход сигнала переноса из-сумматора 4 соединен со входом элемента НЕ 21 ц- со входом элемента И-НЕ 23. Выход сигнала переноса из сумматора |3 соединен со входами элементов И-НЕ 24 и 33, со входом элемента НЕ 22 и со входом элемента И-НЕ 28. Устройство работает следующим образом. Сумматор 1 .выполняет сложение ста ших разрядов слагаемых/ поступающих по шинам 7 и 8, с единичным входным переносом, приходящим по шине 1. Сумматор 2 производит сложение старших разрядов слагаемых, поступаю щих на его входы по шинам 7 и 8, с нулевым входным переносом, идущим на его вход по шине 12. Сумматор 3 осуществляет сложение младших разрядов слагаемых, поступаю щих на его входы по шинам 9 и 10, с нулевым входным переносом, приходя щим на его вход по шине 12. Сумматор 4 выполняет сложение младших разрядов слагаемых, поступаю щих на его входы по шинам 9 и 10, с единичным входным переносом, поступа ющим на его вход по шине 11. При выполнении операции сложения на шину 15 поступает сигнал сложения Сигнал сложения открывает коммутатор 6 для поступления на выходные шины 14 в качестве младших разрядов резул тата с прямого выхода сумматора 3. Если на выходе сумматора 3 есть перенос, то на выходные шины 13 с коммутатор.а 5 поступает прямой выход сумматора 1. Разрешающий сигнал вырабатывается элементе НЕ 29 благода ря наличию сигналов на входах элемента И-НЕ 24 - сигнала переноса с выхода сумматора 3 и сигнала сложения с шины 15. Если на выходе сумматора 3 нет сигнала переноса, то на выходные шины 13 в качестве старших разрядов результата с коммутатора 5 поступает пряькэй выход сумматора 2. Сигнал, открывающий коммутатор 5, поступает свыхода элемента НЕ 30, который Сра батывает при наличии сигналов на вхо дах элемента И-НЕ 25, сигнала сложения с шины 15 и сигнала отсутствия переноса с выхода элемента НЕ 22. При выполнении операции вычитания на шину 16 поступает сигнал вычитания. Вели есть кольцевой перенос, то в качестве шадших разрядов результа та используется выход cyNwaTopa 4. Управляющий коммутатором 6 сигнал поступает с выхода элемеита НЕ 31 и формируется элементами И-НЕ 27. или 28 при наличии сигнала вычитания на шине 16, наличием или отсутствием переноса с выхода сумматора 3 и наличием переноса на выходе сумматора 1 или 2. В качестве старших разрядов результата операции в этом случае используется прямой выход сумматора 1 или 2. Управляющие коммутатором 5 сигналы поступают с выходов элементов НЕ 29 или 30 и формируются элементами И-НЕ 23 или 26 в зависимости от наличия сигнала переноса 1C выхода сумматора .4. При отсутствии кольцевого переноса в качестверезультата используются инвертированные блоками 16 и 20 инверсии выходные сигналы сумматоров 1 и 3. При этом управляющие коммутаторами 5 и 6 сигналы поступают с выходов элементов НЕ 35 и 37. Предлагаемое устройство позволяет выполнить операции сложения или вы-. читания без снижения быстродействия. Логическая структура устройства характеризуется высоким быстродействием, так как процесс формирования переноса из старшей части сумматора совмещен с процессом формирования прогнозируемого результата. Формула изобретения 1. Устройство для суммирования с условным переносом, содержащее три сумматора, первый и второй входы каждого из первых двух сумматоров соединены с шинами, подачи старших разрядов слагаемых устройства, первый и второй входы третьего сумматора соединены с шинами подачи младших разрядов слагаемых устройства, третий вход первого сумматора соединен с шиной подачи уровня логической единицы уст ройства, третьи входы второго и третьего сумматоров соединены с шиной подачи уровня логического нуля устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения выполнения операции вычитания, устройство содержит четвертый сумматор, первый и второй входы которо.го соединены с шинами подачи младших разрядов слагаеких, а третий вход четвертого сумматора соединен с шиной, подачи уровня логической единицы устройства, а также содержи- два коммутатора, три блока инверсии и блок анализа состояния сумматоров, входы которого соответственно соединены с выходами сигналов переноса сумматоров, а управляющие входы соединены с шинами подачи сигналов сложения и вычитания устройства, первый, второй, третий и четвертый выходы блока анализа состояния сумматоров соединены с соответствующими управляющими входами первого коммутатора, первый

и второй информационные входа которого соединены с выходом первого сумматора непосредственно и через первый блок инверсии, а третий и четвертый информационные входы - с выходом второго сумматора непосредственно и чере второй блок инверсии, первый информационный вход второго коммутатора соединен с выходом четвертого сумматора, а второй и третий информационные входы - с выходом третьего сумматора непосредственно и через третий блок инверсии, выходы первого и второго коммутаторов соединены с выходными шинами соответственно стар- / luHX и 1младпшх разрядов результата,пятый, шестой и седьмой выходы блока анализа состояния сумматоров соедидинены соответственно с первым, вторым и третьим управляющилм входами второго коммутатора.

2. Сумматор по п. 1, о т л и чающийся тем, что блок анализа состояния сумматоров содержит элементы И-НЕ и НЕ, причем входы первого и второго элементов НЕ соединены с третьим и четвертым входами блока и с первыми входами первого и второго элементов И-НЕ соответственно, первые входы третьего и четвертого элементов И-НЕ соединены с выходами второго и первого элементов НЕ соответственно, первый и второй входы пятого элемента И-НЕ соединены с выходом второго элемента НЕ и вторым входом блока, первый и второй входы шестого элемента И-НЕ соединены с первым и третьим входами блока, вторые .

входы второго и третьего элементов И-НЕ соединены с первым управляющим входом и шестым выходом блока, третьи входы пятого -и шестого элементов И-НЕ соединены со вторым управляющим входом блока, выходы первого и второго элементов И-НЕ объединены и подключены через третий элемент НЕ к первому выходу блока, выходы третьего и четвертого элементов И-НЁ объединены и через четвертый элемент НЕ соединены с третьим выходом блока, выходы пятого и шестого элементов И-НЕ объединены и подключены к первому входу седьмого элемента И-НЕ и через пятый элемент НЕ - ко вторым входс1М первого и четвертого элементов И-НЕ и пятому выходу блока, второй вход седьмого элемента И-НЕ подключен ко второму управляющему входу блока, а выход через шестой элемент НЕ - к седьмому выходу блока и первым входам восьмого и девятого элементов ИНЕ, вторые входы которых соединены с третьим входом блока и выходом второго элемента НЕ соответственно, а выходы через седьмой и восьмой элементы НЕ соответственно - со вторым и четвертым выходами блока..

Источники информации, принятые во внимание при экспертизе

1.Гаврилов Ю.В. и Пучко А.Н. Арифметические устройства быстродействующих ЭЦВМ. М., Советское радио, 1970, с. 92, рис. 2.4.5.

2.Соловьев Г.Н. Арифметические устройства ЭВМ. М., Энергия, 1978, с. 98, рис. 4.22 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения - вычитания | 1985 |

|

SU1273918A1 |

| Устройство для побитовой обработки чисел,представленных в форме с плавающей запятой | 1980 |

|

SU938284A1 |

| Сумматор | 1974 |

|

SU541173A2 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| Устройство для сложения в избыточной восьмеричной системе счисления | 1984 |

|

SU1206771A2 |

| Сумматор | 1974 |

|

SU541172A2 |

| Арифметическое устройство в системе остаточных классов | 1985 |

|

SU1290315A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| Устройство для сложения операндов с плавающей точкой с контролем | 1986 |

|

SU1310826A1 |

Авторы

Даты

1981-04-23—Публикация

1979-06-21—Подача